#### Tait Radio Communications Corporate Head Office

Tait Electronics Ltd P.O. Box 1645 Christchurch New Zealand

For the address and telephone number of regional offices, refer to the TaitWorld website:

Website: http://www.taitworld.com

#### **Technical Support**

For assistance with specific technical issues, contact Technical Support:

E-mail: support@taitworld.com Website: http://support.taitworld.com

#### To our European customers:

Tait Electronics Limited is an environmentally responsible company which supports waste minimization and material recovery. The European Union's Waste Electrical and Electronic Equipment Directive requires that this product be disposed of separately from the general waste stream when its service life is over. Please be environmentally responsible and dispose through the original supplier, your local municipal waste "separate collection" service, or contact Tait Electronics Limited.

# Contents

|   | eface .                                                                        |                                                                                                                                                                                                      |  |  |

|---|--------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|   |                                                                                | pe of Manual                                                                                                                                                                                         |  |  |

|   | -                                                                              | uiries and Comments                                                                                                                                                                                  |  |  |

|   | Updates of Manual and Equipment                                                |                                                                                                                                                                                                      |  |  |

|   | Cop                                                                            | 9yright                                                                                                                                                                                              |  |  |

|   | Disc                                                                           | zlaimer                                                                                                                                                                                              |  |  |

|   |                                                                                | minology                                                                                                                                                                                             |  |  |

|   | · ·                                                                            | al Naming Convention                                                                                                                                                                                 |  |  |

|   |                                                                                | Numbering Convention                                                                                                                                                                                 |  |  |

|   |                                                                                | ociated Documentation                                                                                                                                                                                |  |  |

|   |                                                                                | lication Record                                                                                                                                                                                      |  |  |

|   | GIU                                                                            | ssary/                                                                                                                                                                                               |  |  |

| 1 | Replac                                                                         | ring the Network Board                                                                                                                                                                               |  |  |

|   | 1.1                                                                            | Equipment Required                                                                                                                                                                                   |  |  |

|   | 1.2                                                                            | Troubleshooting                                                                                                                                                                                      |  |  |

|   | 1.3                                                                            | Before You Start                                                                                                                                                                                     |  |  |

|   | 1.4                                                                            | Removing the Faulty Board                                                                                                                                                                            |  |  |

|   | 1.5                                                                            | Replacing the Board                                                                                                                                                                                  |  |  |

|   |                                                                                | Restoring the Configuration                                                                                                                                                                          |  |  |

|   | 1.0                                                                            |                                                                                                                                                                                                      |  |  |

| 2 | Recite                                                                         | r Circuit Descriptions                                                                                                                                                                               |  |  |

| 3 | Digita                                                                         | l Circuitry                                                                                                                                                                                          |  |  |

|   | 3.1                                                                            | I CIrcultry                                                                                                                                                                                          |  |  |

|   |                                                                                | -                                                                                                                                                                                                    |  |  |

|   |                                                                                | Digital IF                                                                                                                                                                                           |  |  |

|   | 3.2                                                                            | Digital IF    21      Digital Signal Processor (DSP)    22                                                                                                                                           |  |  |

|   | 3.2<br>3.3                                                                     | Digital IF                                                                                                                                                                                           |  |  |

|   | 3.2                                                                            | Digital IF    21      Digital Signal Processor (DSP)    22                                                                                                                                           |  |  |

| 4 | 3.2<br>3.3<br>3.4                                                              | Digital IF       21         Digital Signal Processor (DSP)       22         Reduced Instruction Set Computer (RISC)       25         40 MHz Digital Clock       27                                   |  |  |

| 4 | 3.2<br>3.3<br>3.4<br>Refere                                                    | Digital IF21Digital Signal Processor (DSP)22Reduced Instruction Set Computer (RISC)2540 MHz Digital Clock27ence Switch29                                                                             |  |  |

| 4 | 3.2<br>3.3<br>3.4<br><b>Refere</b><br>4.1                                      | Digital IF21Digital Signal Processor (DSP)22Reduced Instruction Set Computer (RISC)2540MHz Digital Clock27ence Switch29Synthesizer29                                                                 |  |  |

| 4 | 3.2<br>3.3<br>3.4<br><b>Refere</b><br>4.1<br>4.2                               | Digital IF21Digital Signal Processor (DSP)22Reduced Instruction Set Computer (RISC)2540 MHz Digital Clock27ence Switch29Synthesizer29VCXO29                                                          |  |  |

| 4 | 3.2<br>3.3<br>3.4<br><b>Refere</b><br>4.1<br>4.2                               | Digital IF21Digital Signal Processor (DSP)22Reduced Instruction Set Computer (RISC)2540MHz Digital Clock27ence Switch29Synthesizer29                                                                 |  |  |

| 4 | 3.2<br>3.3<br>3.4<br><b>Refere</b><br>4.1<br>4.2<br>4.3                        | Digital IF21Digital Signal Processor (DSP)22Reduced Instruction Set Computer (RISC)2540 MHz Digital Clock27ence Switch29Synthesizer29VCXO29                                                          |  |  |

|   | 3.2<br>3.3<br>3.4<br><b>Refere</b><br>4.1<br>4.2<br>4.3                        | Digital IF21Digital Signal Processor (DSP)22Reduced Instruction Set Computer (RISC)2540MHz Digital Clock27ence Switch29Synthesizer29VCXO29Reference Switch30                                         |  |  |

|   | 3.2<br>3.3<br>3.4<br><b>Refere</b><br>4.1<br>4.2<br>4.3<br><b>Netwo</b>        | Digital IF21Digital Signal Processor (DSP)22Reduced Instruction Set Computer (RISC)2540MHz Digital Clock27ence Switch29Synthesizer29VCXO29Reference Switch30ork Circuitry33                          |  |  |

|   | 3.2<br>3.3<br>3.4<br><b>Refere</b><br>4.1<br>4.2<br>4.3<br><b>Netwo</b><br>5.1 | Digital IF21Digital Signal Processor (DSP)22Reduced Instruction Set Computer (RISC)2540MHz Digital Clock27ence Switch29Synthesizer29VCXO29Reference Switch30ork Circuitry33Top Level Block Diagram33 |  |  |

|   | 5.5                                      | I/O Buffers                                                                                                                |

|---|------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

|   | 5.6                                      | Ethernet Interface                                                                                                         |

|   | 5.7                                      | Audio and E&M Interface                                                                                                    |

|   | 5.8                                      | Clock Oscillator                                                                                                           |

|   | 5.9                                      | Power Supply                                                                                                               |

| 6 | RF Ci                                    | rcuitry                                                                                                                    |

|   | 6.1                                      | Receiver RF Circuitry - VHF Reciter                                                                                        |

|   | 6.2                                      | Receiver RF Circuitry - UHF Reciter                                                                                        |

|   | 6.3                                      | Exciter RF Circuitry                                                                                                       |

|   |                                          |                                                                                                                            |

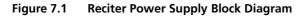

| 7 | Power                                    | Supply                                                                                                                     |

| 7 |                                          | Supply                                                                                                                     |

| 7 | 7.1                                      |                                                                                                                            |

| 7 | 7.1<br>7.2                               | <b>RF PCB</b>                                                                                                              |

|   | 7.1<br>7.2                               | RF PCB       101         Digital PCB       101                                                                             |

|   | 7.1<br>7.2<br><b>Appen</b>               | RF PCB       101         Digital PCB       101         dices       103                                                     |

|   | 7.1<br>7.2<br><b>Appen</b><br>8.1        | RF PCB       101         Digital PCB       101         dices       103         Appendix A – I2C Device Addresses       103 |

|   | 7.1<br>7.2<br><b>Appen</b><br>8.1<br>8.2 | RF PCB101Digital PCB101dices103Appendix A – I2C Device Addresses103Appendix B – ASIF Connectors104                         |

### Scope of Manual

Welcome to the TB9100 Reciter Service Manual. This manual provides servicing information for the TB9100 reciter. All other TB9100 base station servicing information is the same as the information provided in the TB8100 Service Manual.

# **Enquiries and Comments**

If you have any enquiries regarding this manual, or any comments, suggestions and notifications of errors, please contact Technical Support (refer to "Tait Contact Information" on page 2).

# **Updates of Manual and Equipment**

In the interests of improving the performance, reliability or servicing of the equipment, Tait Electronics Limited reserves the right to update the equipment or this manual or both without prior notice.

# Copyright

All information contained in this manual is the property of Tait Electronics Limited. All rights are reserved. This manual may not, in whole or in part, be copied, photocopied, reproduced, translated, stored, or reduced to any electronic medium or machine-readable form, without prior written permission from Tait Electronics Limited. All trade names referenced are the service mark, trademark or registered trademark of the respective manufacturers.

## Disclaimer

There are no warranties extended or granted by this manual. Tait Electronics Limited accepts no responsibility for damage arising from use of the information contained in the manual or of the equipment and software it describes. It is the responsibility of the user to ensure that use of such information, equipment and software complies with the laws, rules and regulations of the applicable jurisdictions.

# Terminology

To align with the PowerPC documentation, this document uses the term "word" to refer to a 32-bit number; a 16-bit number is referred to as a "halfword". This convention is continued through the sections in this document relating to the DSP. However, other documentation on the DSP may refer to a "word" as being a 16-bit quantity.

In this text, the term "asserted" refers to a signal being driven to its active state, regardless of whether that active state is logic high or logic low. Conversely, the term "negated" refers to a signal being driven to its inactive state.

# **Signal Naming Convention**

Active low logic signals are indicated in the text with an overbar or by a negation bubble on schematic symbols. However, due to limitations of the schematic editor, active-low signal names have been indicated on the schematics with an "\_N" suffix.

Hexadecimal numbers are indicated with a "0x" prefix. Binary numbers are indicated with a "0b" prefix.

### **Bus Numbering Convention**

Signals that are grouped in a bus will be labelled thus:

Bus\_name[most\_significant\_bit .. least\_significant\_bit]eg. D[31..0]

**Note** The PowerPC architecture defines the numbering of data and address buses in the reverse order to normal convention. Hence, D0 is the msb and D31 is the lsb of the data bus. Other devices in the ASIF use conventional numbering order; the transition from PowerPC numbering order to normal numbering order occurs at the external pins of the PowerPC processor.

### **Associated Documentation**

TB8100 Service Manual.

TB9100 Specifications Manual.

TB9100 Installation and Operation Manual.

TB9100 Customer Service Software User's Manuals and online Help.

TB9100 Calibration Kit User's Manual and online Help.

TB9100 Network Installation Guide.

Technical notes are published from time to time to describe applications for Tait products, to provide technical details not included in manuals, and to offer solutions for any problems that arise.

All available TB9100 product documentation is provided on the CD supplied with the base station<sup>1</sup>. Updates may also be published on the Tait Technical Support website (http://support.taitworld.com).

# **Publication Record**

| Issue | Publication Date | Description   |

|-------|------------------|---------------|

| 1     | January 2006     | First release |

# Glossary

| 1PPS       | One Pulse Per Second                                                                                                                                                               |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 100BaseT   | 100Mbps ethernet over a twisted pair network                                                                                                                                       |

| 10BaseT    | 10Mbps ethernet over a twisted pair network                                                                                                                                        |

| 2W         | Two wire, an audio interface with a single cable<br>pair shared for both transmit and receive signals                                                                              |

| 4W         | Four wire, an audio interface with separate cable pairs for transmit and receive signals                                                                                           |

| АРСО       | Association of Public Safety Communications<br>Officers, a US body of public safety<br>communications users (eg. Police, Fire) which<br>defines standards on behalf of its members |

| ASIF       | APCO SIF, the system interface from a base<br>station to an APCO network. Also known as<br>the network board.                                                                      |

| ATM        | Asynchronous Transfer Mode                                                                                                                                                         |

| BD         | Buffer Descriptor                                                                                                                                                                  |

| BDM        | Background Debug Mode, a method of debugging software on a RISC processor                                                                                                          |

| BGA        | Ball Grid Array, a type of integrated circuit package                                                                                                                              |

| Big Endian | A memory ordering scheme where the most-<br>significant byte of a word occupies a lower<br>memory address than the least-significant byte<br>c.f. Little Endian                    |

<sup>1.</sup> Technical notes are only available in PDF format from the Tait support website. Consult your nearest Tait Dealer or Customer Service Organization for more information.

| BRG     | Baud Rate Generator                                                                                     |

|---------|---------------------------------------------------------------------------------------------------------|

| BS      | Refers specifically to the Reciter control element of the base station                                  |

| СРМ     | Communications Processor Module, a RISC<br>processor dedicated to handling<br>communications interfaces |

| CSMA/CD | Carrier Sense Multiple Access with Collision<br>Detection                                               |

| CTS     | Clear to Send                                                                                           |

| DARAM   | Dual-Access RAM                                                                                         |

| DCE     | Data Communications Equipment                                                                           |

| DMA     | Direct Memory Access, a method of moving data to/from memory with hardware assistance                   |

| DRAM    | Dynamic Random Access Memory                                                                            |

| DSP     | Digital Signal Processor, a processor specialized for numerical processing                              |

| DSR     | Data Set Ready                                                                                          |

| DTE     | Data Terminal Equipment                                                                                 |

| DTLB    | Data Translation Lookaside Buffer                                                                       |

| DTR     | Data Terminal Ready                                                                                     |

| E&M     | Ear and Mouth, a simple DC signalling scheme used in telecom networks                                   |

| E2PROM  | Electrically Erasable Programmable Read Only<br>Memory                                                  |

| EDO     | Extended Data Out, a type of DRAM                                                                       |

| ЕНРІ    | Enhanced Host Port Interface, now renamed as<br>HPI                                                     |

| EMC     | Electromagnetic Compatibility                                                                           |

| EMIF    | External Memory Interface                                                                               |

| EPROM   | Erasable Programmable Read Only Memory                                                                  |

| ESD     | Electrostatic Discharge                                                                                 |

| FEC     | Fast Ethernet Controller                                                                                |

| FIFO    | First-In/First-Out, a variable length shift register that supports queuing of data streams              |

| FLASH   | A type of electrically erasable programmable<br>read-only memory. Usually not byte-erasable.            |

| HPI     | Host Port Interface, an interface between a DSP and its host processor                                  |

| GPCM    | General-purpose Chip-select Machine, a basic<br>user programmable memory controller                     |

| GPR     | General purpose register                                                                                |

| Harvard architecture | A type of computer architecture that utilizes<br>separate memory spaces for executable code<br>and data. cf. von Neumann architecture                         |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HW                   | Hardware                                                                                                                                                      |

| I <sup>2</sup> C     | Inter-Integrated Circuit, a serial<br>communications interface mainly intended for<br>interconnecting ICs contained within a single<br>PCB                    |

| IPN                  | Internal Part Number, TEL's internal part numbering system.                                                                                                   |

| ITLB                 | Instruction Translation Lookaside Buffer                                                                                                                      |

| IU                   | Integer Unit                                                                                                                                                  |

| JTAG                 | Joint Test Action Group, a test interface specification for PCB assembly testing                                                                              |

| Little Endian        | A memory ordering scheme where the least-<br>significant byte of a word occupies a higher<br>memory address than the most-significant byte<br>c.f. Big Endian |

| LRU                  | Least Recently Used, a method of updating cache memory contents                                                                                               |

| lsb                  | Least significant bit                                                                                                                                         |

| LSU                  | Load/Store Unit                                                                                                                                               |

| LVTTL                | Low Voltage TTL, logic specified for operation<br>at 3.3V supply and compatible with 5V TTL<br>family logic levels ie. VIH = $2.0$ V and<br>VIL= $0.8$ V      |

| MAC                  | Media access controller, an ethernet controller                                                                                                               |

| McBSP                | Multi-channel Buffered Serial Port                                                                                                                            |

| MII                  | Media Independent Interface, an interface for ethernet PHY devices                                                                                            |

| MIPs                 | Million Instructions Per Second                                                                                                                               |

| MMU                  | Memory Management Unit                                                                                                                                        |

| MOSFET               | Metal Oxide Semiconductor Field Effect<br>Transistor                                                                                                          |

| MPC                  | MPC859TPZ133 PowerQUICC<br>microprocessor                                                                                                                     |

| NMI                  | Non-maskable interrupt                                                                                                                                        |

| OTP                  | One Time Programmable, a non-volatile<br>memory device that cannot be erased and<br>reprogrammed after initial programming                                    |

| msb                  | Most significant bit                                                                                                                                          |

| PBGA                 | Plastic BGA                                                                                                                                                   |

| PCM                  | Pulse Code Modulation                                                                                                                                         |

| PCMCIA                                                                  | Personal Computer Memory Card<br>International Association                                                                                                                                                                                                                                                   |

|-------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PCM highway                                                             | A TDM bus typically used for interconnecting CODECs and DSPs                                                                                                                                                                                                                                                 |

| РНҮ                                                                     | Ethernet PHYsical interface                                                                                                                                                                                                                                                                                  |

| PIT                                                                     | Periodic Interrupt Timer                                                                                                                                                                                                                                                                                     |

| PLL                                                                     | Phase-Locked Loop                                                                                                                                                                                                                                                                                            |

| PowerPC <sup>TM</sup>                                                   | A microprocessor architecture defined by IBM and Motorola                                                                                                                                                                                                                                                    |

| PowerQUICC™                                                             | PowerPC Quad Integrated Communications<br>Controller, a PowerPC integrated with a<br>QUICC                                                                                                                                                                                                                   |

| рр                                                                      | Peak to Peak                                                                                                                                                                                                                                                                                                 |

| PPC                                                                     | PowerPC <sup>TM</sup>                                                                                                                                                                                                                                                                                        |

| ppm                                                                     | Parts Per Million                                                                                                                                                                                                                                                                                            |

| PSTN                                                                    | Public Switched Telephone Network                                                                                                                                                                                                                                                                            |

| QUICC™                                                                  | Quad Integrated Communications Controller, a version of a CPM                                                                                                                                                                                                                                                |

| Reciter                                                                 | Receiver/Exciter - the RF signal handling parts<br>of the base station excluding the power<br>amplifier                                                                                                                                                                                                      |

| RISC                                                                    | Reduced Instruction Set Computer, a general-<br>purpose processor                                                                                                                                                                                                                                            |

|                                                                         |                                                                                                                                                                                                                                                                                                              |

| RS-232                                                                  | A standard defining electrical parameters for serial interfaces                                                                                                                                                                                                                                              |

| RS-232<br>RSSI                                                          |                                                                                                                                                                                                                                                                                                              |

|                                                                         | serial interfaces                                                                                                                                                                                                                                                                                            |

| RSSI                                                                    | serial interfaces<br>Received Signal Strength Indication                                                                                                                                                                                                                                                     |

| RSSI<br>RTS                                                             | serial interfaces<br>Received Signal Strength Indication<br>Request To Send                                                                                                                                                                                                                                  |

| RSSI<br>RTS<br>Rx                                                       | serial interfaces<br>Received Signal Strength Indication<br>Request To Send<br>Receive                                                                                                                                                                                                                       |

| RSSI<br>RTS<br>Rx<br>RxD                                                | serial interfaces<br>Received Signal Strength Indication<br>Request To Send<br>Receive<br>Receive Data                                                                                                                                                                                                       |

| RSSI<br>RTS<br>Rx<br>RxD<br>SARAM                                       | serial interfaces<br>Received Signal Strength Indication<br>Request To Send<br>Receive<br>Receive Data<br>Single-Access RAM                                                                                                                                                                                  |

| RSSI<br>RTS<br>Rx<br>RxD<br>SARAM<br>SCC                                | serial interfaces<br>Received Signal Strength Indication<br>Request To Send<br>Receive<br>Receive Data<br>Single-Access RAM<br>Serial Communications Controller                                                                                                                                              |

| RSSI<br>RTS<br>Rx<br>RxD<br>SARAM<br>SCC<br>SDMA                        | serial interfaces<br>Received Signal Strength Indication<br>Request To Send<br>Receive<br>Receive Data<br>Single-Access RAM<br>Serial Communications Controller<br>Serial DMA<br>Synchronous Dynamic Random Access                                                                                           |

| RSSI<br>RTS<br>Rx<br>RxD<br>SARAM<br>SCC<br>SDMA<br>SDRAM               | serial interfaces<br>Received Signal Strength Indication<br>Request To Send<br>Receive<br>Receive Data<br>Single-Access RAM<br>Serial Communications Controller<br>Serial DMA<br>Synchronous Dynamic Random Access<br>Memory                                                                                 |

| RSSI<br>RTS<br>Rx<br>RxD<br>SARAM<br>SCC<br>SDMA<br>SDRAM               | serial interfaces<br>Received Signal Strength Indication<br>Request To Send<br>Receive<br>Receive Data<br>Single-Access RAM<br>Serial Communications Controller<br>Serial DMA<br>Synchronous Dynamic Random Access<br>Memory<br>System Interface<br>Synchronous Input/Output, a simplified                   |

| RSSI<br>RTS<br>Rx<br>RxD<br>SARAM<br>SCC<br>SDMA<br>SDRAM<br>SIF<br>SIO | serial interfaces<br>Received Signal Strength Indication<br>Request To Send<br>Receive<br>Receive Data<br>Single-Access RAM<br>Serial Communications Controller<br>Serial DMA<br>Synchronous Dynamic Random Access<br>Memory<br>System Interface<br>Synchronous Input/Output, a simplified<br>version of SPI |

| Software                 | When 'software' is not otherwise qualified, it<br>refers to the ASIF software that is the subject of<br>this document              |

|--------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| SPI                      | Serial Peripheral Interface, a simple serial communications interface mainly used for I/O expansion on microprocessors             |

| SPR                      | Special Purpose Register, a type of register used<br>for configuration and control of the PowerPC<br>CPU core                      |

| SRAM                     | Static Random Access Memory                                                                                                        |

| SW                       | Software                                                                                                                           |

| TAP                      | Test Access Port                                                                                                                   |

| TDM                      | Time Division Multiplex                                                                                                            |

| Telco                    | Telephone Company                                                                                                                  |

| TSA                      | Time Slot Assigner                                                                                                                 |

| TTL                      | Transistor-Transistor Logic, an early bipolar<br>logic family                                                                      |

| Tx                       | Transmit                                                                                                                           |

| TxD                      | Transmit Data                                                                                                                      |

| UART                     | Universal Asynchronous Receiver/Transmitter                                                                                        |

| UPM                      | Universal Programmable Machine, a type of user programmable memory controller                                                      |

| USART                    | Universal Synchronous/Asynchronous<br>Receiver/Transmitter                                                                         |

| UTOPIA                   | Universal Test & Operations PHY Interface for ATM                                                                                  |

| VCTCXO                   | Voltage-Controlled Temperature Compensated crystal Oscillator                                                                      |

| Vocoder                  | Voice coder, a program that encodes voice<br>signals into a digital representation, or vice<br>versa                               |

| von Neumann architecture | A type of computer architecture that combines<br>executable code and data into the same<br>memory space. cf. Harvard architecture. |

This section describes how to troubleshoot and replace a faulty reciter network board. Servicing procedures for the reciter digital board and the reciter RF board are covered in the TB8100 Service Manual.

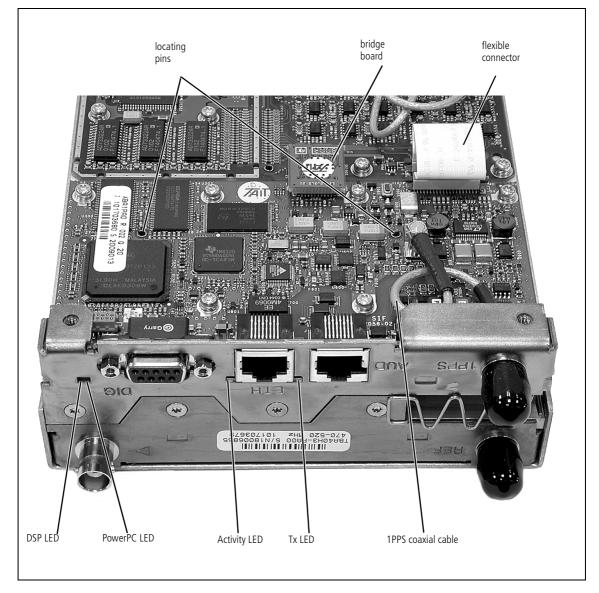

Figure 1.1 Network Board

1

# 1.1 Equipment Required

- Anti-static work environment

- PC with Ethernet cable.

- Torque screwdriver (4.5in-lbs) with Torx T-10 bit

- TB9100 subrack (PA not required)

- Power cable, PMU to reciter

- Ethernet switch or hub (if available)

# 1.2 Troubleshooting

Before replacing the network board, carry out the following tests on the reciter to exclude other causes and to verify that the fault actually lies in the network board hardware.

- 1. Connect the reciter to the subrack via the I<sup>2</sup>C bus and the DC power cable. Apply power. This checks whether the digital board is working and receiving communications from the network board.

- a. If no LEDs light on the control panel or rear panel, check that power is being supplied to the reciter.

- b. If the control panel power LED comes on first, followed by the others, the digital board firmware is working.

- c. If the control panel LEDs all remain on for more than 30 seconds, the digital board is not receiving communications from the net-work board.

- 2. Carry out a visual check of the LEDs on the rear of the reciter to check the network board's functional subsystems.

- a. If all LEDs are off, open the reciter and check the flexible connector (it supplies power to the network board). Replace if faulty (see step 5. on page 17).

- b. If the PowerPC LED is flashing quickly (2 Hz), the operating system kernel is running. If it is flashing slowly (0.5 Hz), only the bootloader is running. If the Power PC LED does not flash, check that there is power to the board. The Tx LED should flash once when power is connected. If it does, power is present, so the bootloader must be faulty (see step 7. on page 15).

- c. If the orange LED is flashing, the DSP software in the network board is executing code. If the LED doesn't flash, open the reciter and check that the bridge board is connecting properly.

- d. The green Ethernet LED should flash if the digital line is connected to an Ethernet switch. This indicates that the digital line is receiving activity pulse from the Ethernet switch.

- 3. Connect to the network board's serial port to test its functioning.

- a. Connect your PC to the 9-pin serial connector on the back of the reciter.

- b. Run a program such as HyperTerminal, Teraterm or minicom.

- c. Select the following port settings: 57600 baud, 8 bits, no parity, 1 stop bit, no flow control.

- d. Press the 'Enter' key. If a login prompt appears, the kernel is running. If the bootloader prompt (=>) appears, contact Tait for

assistance with re-loading the kernel and application software.

- e. Note down the reciter's IP address that is displayed at the login prompt and close the session.

- 4. Connect the PC to the network board over its digital Ethernet line.

- a. Using the IP address you noted down, ping the reciter from the Windows command prompt. If there is a response, the network board's Ethernet interface circuitry is functioning in both directions. If there is no response, replace the board.

- b. Attempt to connect the CSS to the reciter. If this is successful, the network board application is running. Check the Alarm Status screen for reciter alarms. Carry out the control panel LED diagnostic test.

- 5. If there is no obvious hardware fault, replace the current firmware and/or kernel to see if this fixes the problem.

- a. If possible, use the CSS to upload the firmware.

- b. Otherwise, follow TN-997 to replace the kernel and/or the firmware using telnet and a TFTP server.

- 6. Exclude the base station configuration as the source of problems by programming in a new configuration.

- a. In the CSS, connect to the reciter.

- b. Read the configuration and save it to file.

- c. Select File > New.

- d. Modify the new configuration as necessary.

- e. Program the new configuration into the reciter, leaving its current IP address and netmask.

- 7. Attempt to access the bootloader prompt. If this is unsuccessful, the bootloader is faulty. The reciter will need to be returned to Tait Electronics Limited for the bootloader to be repaired.

- 8. If the network board fails some or all of the above tests, replace it as described below.

### **1.3 Before You Start**

Make sure you have a backup of the current base station configuration. Obtain it from the customer or, if possible, use the CSS to connect to the reciter, read the configuration, and save it to a file.

# 1.4 Removing the Faulty Board

- 1. Remove the M3 Torx screws securing the cover on the digital side of the reciter. Lift off the cover. (The digital side is nearest to the 9-way D and RJ45 connectors.)

- 2. Remove the two M3 Torx screws that secure the rear panel on the digital side of the reciter.

- 3. Disconnect the coaxial cable from the network board and lift off the bridge board.

- 4. Disconnect the flexible connector by gently levering up the lugs on the ends of the latch. The flexible connector springs free.

- 5. Remove the eight M3 Torx screws that secure the network board to the heatsink.

- 6. Carefully lift the network board off the locating pins and remove it from the heatsink.

*Important* Flexing the board may damage the PCB tracking or break solder joints.

If the board is a snug fit on the locating pins, you may have to very gently lever the board with a screwdriver, beginning at the right-hand side (as viewed in Figure 1.1), to get it to lift.

# 1.5 Replacing the Board

**Important** Be very careful to keep the replacement board scrupulously clean. The board is densely populated and the smallest particle of conductive dust can cause a short.

Important Make sure the insulator sheet is correctly positioned and flat on the heatsink. Although this sheet is an electrical insulator, it is also thermally conductive and must allow the PCB to sit as flat as possible to provide effective heatsinking.

Operating the reciter without the insulator sheet in place will result in permanent damage to the digital or system interface PCBs.

- 1. Make sure that there is no debris on the underside of the network board.

- 2. Position the replacement network board over the locating pins and press it down over them so that it is firmly seated against the insulator sheet on the heatsink.

3. Replace the eight M3 Torx screws and tighten them to the correct torque.

*Important* Do not exceed 4.5in-lbs of torque; greater torque settings may damage the PCB. Inadequately tight screws can affect the EMC properties of the board.

- 4. Position the bridge board above the sockets and the right way round. Press it into place.

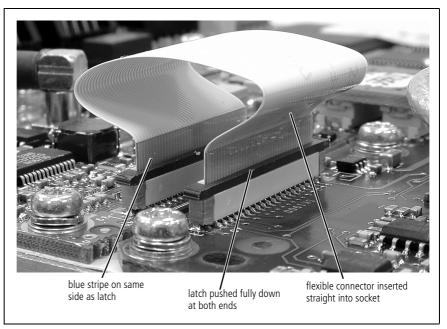

- 5. Carefully reconnect the flexible connector as shown in Figure 1.2. (If required, fit a new flexible cable. It must be correctly formed to prevent excessive stress on the cable or the connector.) Make sure that the cable is properly located before pressing the latch down.

Figure 1.2 Reconnecting the Flexible Connector

- 6. Reconnect the 1 PPS coaxial cable.

- 7. Replace the rear panel and the reciter cover. Tighten the Torx screws to the correct torque. Inadequately tight screws can affect the EMC properties of the board.

- 8. Return the faulty board to Tait.

# **1.6** Restoring the Configuration

- 1. Connect the CSS to the reciter using the correct IP address (network boards are given the IP address 192.168.1.2 in the factory.)

- 2. Restore the base station's configuration, overwriting the IP address.

- 3. Reset the reciter. On power-up, the reciter uses the new IP address.

- 4. Use the procedures in the Troubleshooting section above to verify correct operation of the network board.

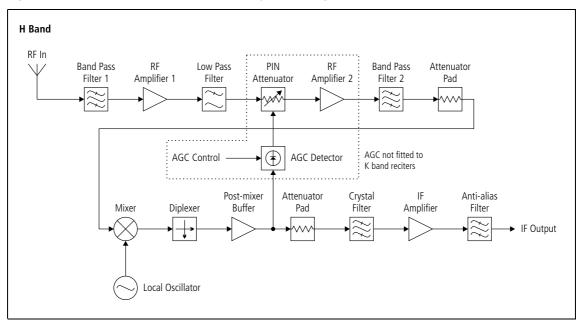

This chapter describes the circuitry used in VHF and UHF reciters. Much of this circuitry is common to both frequency bands, and is therefore covered by a single description in this chapter. Where the circuitry differs between VHF and UHF, separate descriptions are provided for each frequency band. In some cases the descriptions refer to specific VHF or UHF bands or sub-bands, and these are identified with the letters listed in the following table.

|     | Frequency<br>Identification | Frequency Band and Sub-band                                                                      |

|-----|-----------------------------|--------------------------------------------------------------------------------------------------|

| VHF | B band                      | B1 = 136MHz to 174MHz<br>B2 = 136MHz to 156MHz<br>B3 = 148MHz to 174MHz                          |

| UHF | H band                      | H0 = 400MHz to 520MHz<br>H1 = 400MHz to 440MHz<br>H2 = 440MHz to 480MHz<br>H3 = 470MHz to 520MHz |

Table 2.1 TB9100 frequency bands

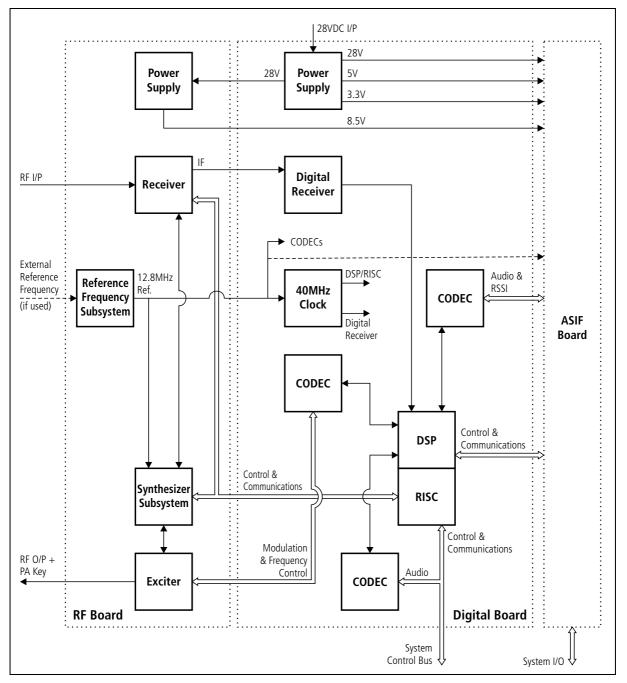

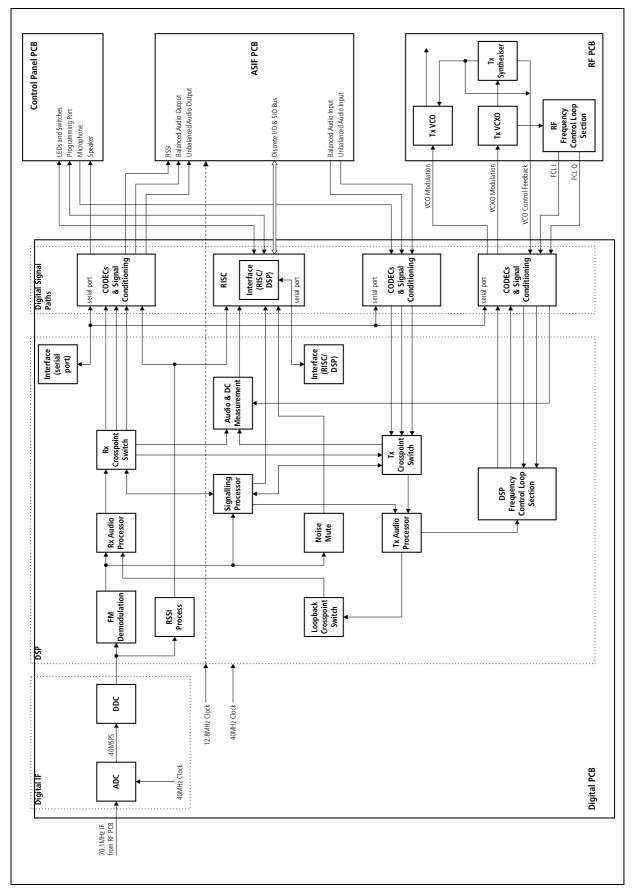

The reciter comprises three PCBs: an RF, a digital, and a network PCB. These PCBs are mounted on a central chassis/heatsink. Figure 2.1 on page 20 shows the configuration of the main circuit blocks, and the main inputs and outputs for power, RF and control signals. The locations of the main circuit blocks on the PCBs are shown in Figure 5.1 on page 36.

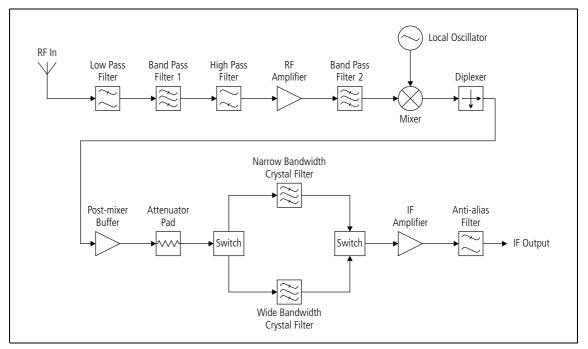

Refer to Figure 3.1 on page 24.

# 3.1 Digital IF

#### 3.1.1 VHF Reciter

The heart of the digital IF system is the 14-bit analog-to-digital converter (ADC). This is a high-speed device, with a multi-staged "pipeline" architecture, which is clocked and outputs samples at 40 MSPS (megasamples per second). The analog IF input of the ADC is a differential structure, and the output is via a 14-bit parallel bus.

The band-limited 16.9MHz IF signal is sampled by the ADC at 40MSPS. The sampling process results in images of the input signal appearing at other frequencies so that the ADC behaves in a similar fashion to a mixer. The digital output therefore contains the wanted signal and the images, which can be digitally processed to extract one of the many signals. The desired IF is at 16.9MHz.

The digital downconverter (DDC) digitally downconverts the 16.9MHz IF to baseband. This is achieved by digital mixing with a numerically controlled oscillator (NCO). The mixing process is done using in-phase and quadrature methods to achieve image rejection, and allows channel filtering to be applied before the signal is passed to the digital signal processor (DSP) for demodulation. The digital channel filtering also decimates the sample rate down to 50kSPS (kilosamples per second) for the DSP.

#### 3.1.2 UHF Reciter

The heart of the digital IF system is the 14-bit analog-to-digital converter (ADC). This is a high-speed device, with a multi-staged "pipeline" architecture, which is clocked and outputs samples at 40 MSPS (megasamples per second). The analog IF input of the ADC is a differential structure, and the output is via a 14-bit parallel bus.

The band-limited 70.1 MHz IF signal is sub-sampled by the ADC at 40 MSPS. The sub-sampling results in images of the input signal appearing at other frequencies so that the ADC behaves in a similar fashion to a mixer. The digital output therefore contains information in the form of images, which can be digitally processed to extract one of the many signals. The lowest frequency image for the 70.1 MHz IF and 40 MHz clock is at 9.9 MHz.

The digital downconverter (DDC) digitally downconverts the desired image (9.9 MHz) to baseband. This is achieved by digital mixing with a numerically controlled oscillator (NCO). The mixing process is done using in-phase and quadrature methods to achieve image rejection, and allows channel filtering to be applied before the signal is passed to the digital signal processor (DSP) for demodulation. The digital channel filtering also decimates the sample rate down to 50 kSPS (kilosamples per second) for the DSP.

## 3.2 Digital Signal Processor (DSP)

The DSP is responsible for software processing of digitized signals in the receiver and transmitter. The processing word width is 16-bit fixed point. There are 96 kilobytes of on-chip program memory, and 64 kilobytes of on-chip data memory. Although no external memory is used, the external memory interface is connected to the DDC for initialization and configuration.

#### 3.2.1 Transmit Functions

The DSP performs the following transmit functions:

- CTCSS and DCS sub-audible signal generation

- CWID generation

- pip tone generation

- audio filtering: including removal of sub-audible components, preemphasis and low pass filtering

- signal path switching

- signal level adjustment

- peak FM deviation limiting

- FM signal generation by controlling the dual point modulator

- calibration parameter estimation

- line level monitoring.

#### 3.2.2 Receive Functions

The DSP performs the following receive functions:

- detection of CTCSS and DCS signalling

- audio filtering: including removal of sub-audible components, deemphasis and low pass filtering

- signal path switching

- signal level adjustment

- FM demodulation of the base band signal

- RSSI measurement for monitoring and RSSI signal voltage output

- SINAD measurement

- measurement and detection for control of the audio mute

- calibration parameter estimation

- line level monitoring.

#### 3.2.3 Serial Ports

The DSP has three synchronous serial ports. Serial port 1 is connected to the DDC and receives base band samples. Serial port 2 is connected to the three CODECs (encoder/decoder). Serial port 3 is not used.

#### 3.2.4 CODECs

The three CODECs provide the audio frequency analog interface to the reciter. There are six analog input and six analog output paths. The sample rate on all paths is 25 kSPS and the sampling resolution is 16 bits.

The CODEC inputs are as follows:

- two input signals from the frequency control loop (FCL)

- balanced line input

- unbalanced line input

- microphone input

- synthesizer loop control voltage.

The CODEC outputs are as follows:

- VCO voltage control line

- VCXO voltage control line

- balanced line output

- unbalanced line output

- speaker output

- RSSI voltage indicator.

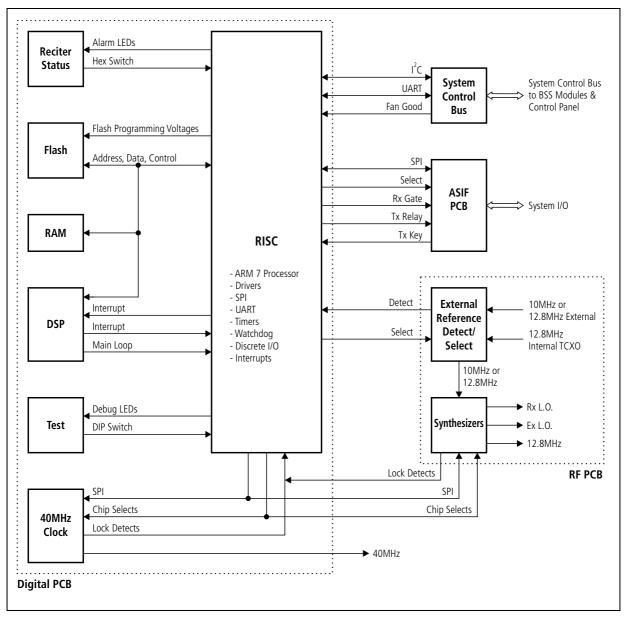

# 3.3 Reduced Instruction Set Computer (RISC)

Refer to Figure 3.2 on page 26.

#### 3.3.1 Hardware and I/O

The RISC processor engine is a Samsung S3C3410X processor with a 40MHz external clock. It has 4 megabytes of flash memory containing the following:

- bootloader

- application code

- DSP code

- non-volatile data

- 2 megabytes of RAM for run-time variables.

The discrete digital inputs and outputs are as follows:

- chip select signals to synthesizers

- out-of-lock signals from synthesizers

- external reference detection

- internal/external reference selection

- Rx Gate output

- Tx Relay output

- reciter hex switch

- reciter alarm LED

- DIP switch for manufacturing testing

- debug LEDs

- fan good input

- flash programming voltage control.

The RISC has the following serial interfaces:

- asynchronous serial port for communication with the CCS software and CCTM

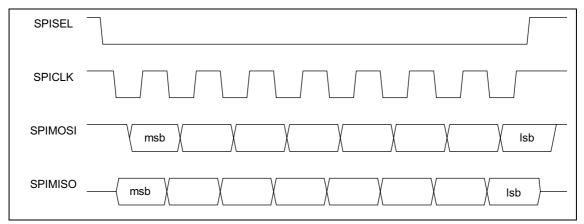

- serial peripheral interface (SPI) for programming the synthesizers

- SPI for communication with the network PCB

- I<sup>2</sup>C for communication with the control panel and other modules in the subrack.

#### 3.3.2 Responsibilities

The RISC communicates with the DSP's shared memory via a host port interface. It loads the DSP code and monitors and controls the following DSP operations:

- receive path

- transmit path

- crosspoint switches

- power supplies

- PA Key output.

The RISC controls the frequency generation subsystem. It detects an external reference source and selects internal or external reference. It also programs, and handles out-of-lock signals for, the following synthesizers:

- 12.8MHz external reference synthesizer

- 40MHz digital clock synthesizer

- receiver synthesizer

- exciter synthesizer.

The RISC communicates with the control panel via  $I^2C$  bus to:

- read the button states

- read the microphone PTT state

- control the LEDs

- turn the speaker amplifier on and off

- turn the microphone amplifier on and off.

The following signals go via the control panel for signal conditioning:

- CSS communication via the RS-232 interface

- fan-good indication (front panel fans).

Note that the volume control on the control panel is analog only and is not controlled by the RISC.

The RISC communicates with the other modules in the subrack via  $I^2C$  in order to:

- verify that they are present

- write configuration settings

- read their current status.

The RISC subsystem communicates with the network PCB via SPI to:

- set input and output gains

- mute and unmute outputs

- read digital inputs

- write digital outputs.

The Rx Gate and Tx Relay lines go via the network PCB for signal conditioning.

### 3.4 40 MHz Digital Clock

The 40 MHz synthesized digital clock is situated on the digital PCB. It is used to drive the entire digital circuitry.

The 40 MHz frequency synthesizer is implemented using an Integer\_Nbased phase locked loop (PLL) IC. The PLL is a negative feedback loop, which continuously monitors and maintains the 40MHz VCXO to a fixed frequency and constant phase relationship with respect to a 12.8MHz reference. The 40MHz VCXO oscillator is electrically tuned using two varactors. The oscillator output is buffered before being distributed to the digital circuitry.

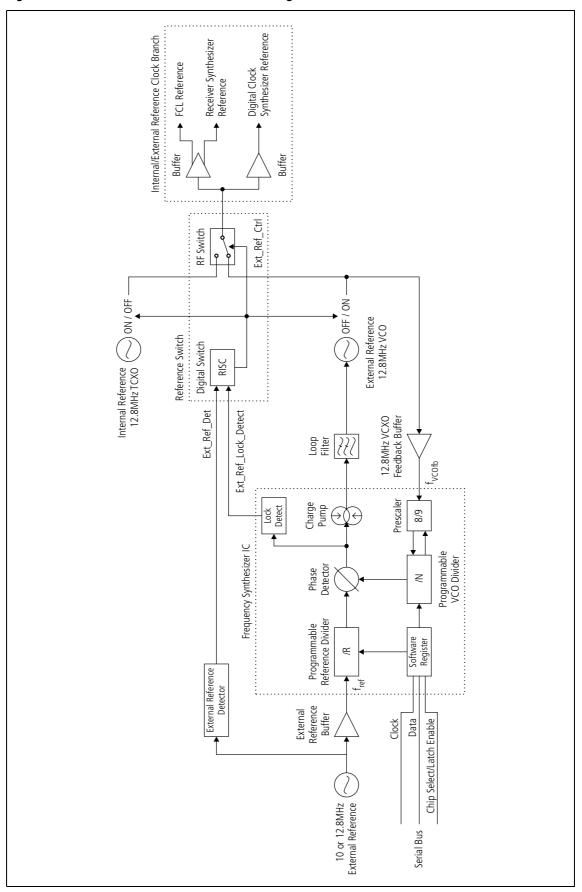

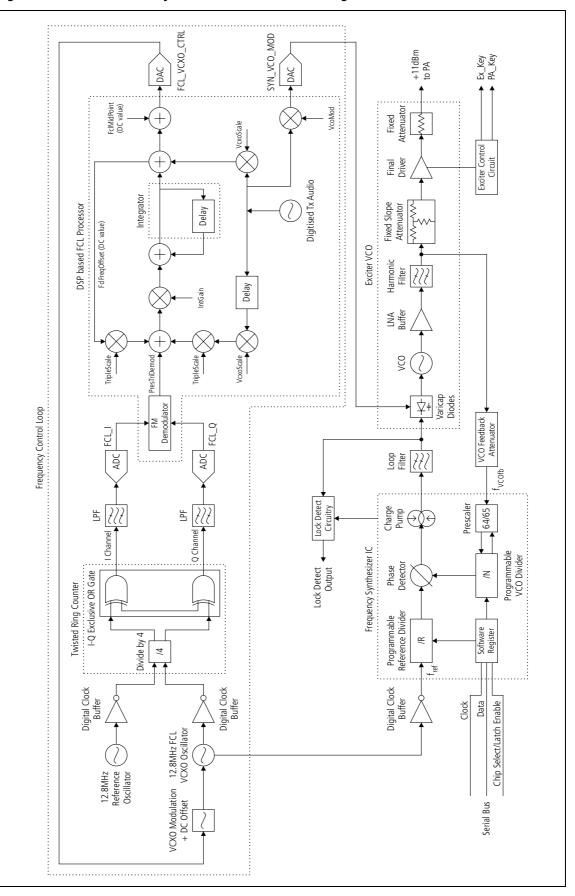

Refer to Figure 4.1 on page 31.

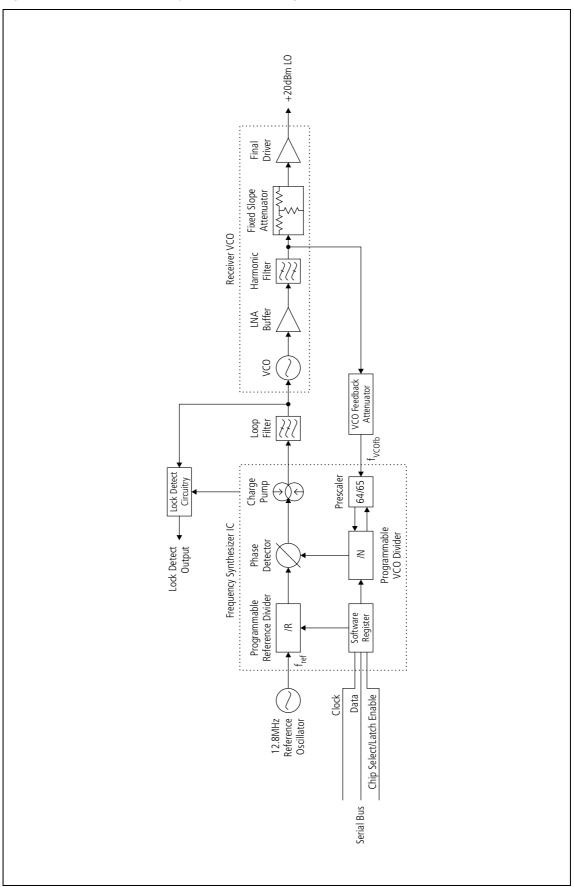

# 4.1 Synthesizer

The external reference synthesizer consists of a programmable frequency synthesizer IC, a 12.8MHz VCXO, and a stable 10MHz or 12.8MHz reference frequency supplied to the reciter externally via a BNC connector on the rear panel.

The synthesizer uses a phase-locked loop to lock the 12.8 MHz VCXO to the external reference frequency. The synthesizer IC receives the divider and control information from the RISC processor via a 3-wire serial bus (clock, data and enable). When the data bits are latched in, the synthesizer processes incoming signals from the 12.8 MHz VCXO feedback buffer ( $f_{vcxofb}$ ) and the external reference buffer ( $f_{ref}$ ).

A transistor is used as a unity gain 12.8MHz VCXO feedback buffer for the prescaler within the synthesizer IC.

The 10MHz or 12.8MHz externally supplied reference is detected, buffered and divided down to the 100kHz divider reference within the synthesizer IC. The same divider reference is maintained by dividing the 12.8MHz VCXO feedback buffered signal using the programmable dividers of the synthesizer IC. Phase lock is achieved when both divider references have the same phase and frequency content (i.e. their difference is zero or DC). This is achieved by the digital phase detector (part of the synthesizer IC), which compares both divider references and delivers an error signal. A  $\pm 1$  mA charge pump circuit (also part of the synthesizer IC) and the passive loop filter circuit convert this error signal to a DC voltage (0 to 3V) to tune the 12.8MHz VCXO for correction. A loop filter with a bandwidth of 180Hz further filters the VCO control line reference side bands and spurious signals.

• The VCXO frequency increases as the control line voltage increases.

## 4.2 VCXO

The VCXO is implemented by using a varactor to linearly tune a 12.8 MHz crystal unit over a specified frequency range. The frequency range provided will cover frequency drifts due to calibration, the temperature tolerance of

the crystal unit, and the frequency stability of the externally supplied reference.

### 4.3 Reference Switch

The reference switch consists of the external reference detector, the hardware switch, and the digital switch.

#### 4.3.1 External Reference Detector

A discrete NPN dual transistor pair is used as a low level signal detector. The Syn\_Ref\_Det signal has a high logic level when the externally supplied signal has the correct level.

#### 4.3.2 Hardware Switch

The hardware switch is implemented using a discrete dual transistor pair. When the switch is off (default), it powers up the internal reference 12.8MHz TCXO and shuts down the external reference 12.8MHz VCXO. When the switch is on, it powers up the external reference 12.8MHz VCXO and shuts down the internal reference 12.8MHz TCXO.

#### 4.3.3 Digital Switch

The digital switch is controlled by the RISC, which processes the Syn\_Ref\_Det and Lock Detect signals from the external reference synthesizer. The RISC controls the hardware switch using the Syn\_Ref\_Ctrl signal. The hardware switch is on if the Syn\_Ref\_Det **and** Lock Detect signals have a high logic level for a set time. In all other conditions the hardware switch is off.

#### 4.3.4 Internal/External Reference Clock Branch

A complementary emitter follower, using NPN/PNP dual transistors, forms two clock buffer branches which distribute the internal or external references to the rest of the system. The branches provide a reasonable drive level at low impedance.

Figure 4.1 Reciter External Reference Block Diagram

### 5.1 Top Level Block Diagram

A simplified block diagram of the ASIF is shown in Figure 5.1. The toplevel schematic sheet (226-02056-01 sheet 1) shows a more detailed view of the main circuit blocks together with their interconnections and external connections to/from the ASIF board.

There are seven main circuit blocks:

- RISC processor

- DSP

- I/O buffers

- ethernet interface

- audio and E&M interface

- clock oscillator

- power supply

The RISC processor block (see "Risc Processor" on page 38) is the heart of the ASIF, providing the main control functions and most of the peripheral interface functions. This block also contains the main memory for the ASIF (see "Memory" on page 61), all of which is interfaced to the RISC processor. From the RISC processor block various signals are routed to the reciter via connector J101 whilst other signals are routed through the I/O buffers, the ethernet interface and the audio and E&M interface blocks to connect to the outside world.

These interfaces provide signal formatting, signal level conversion, I/O protection, etc, for the logic level signals emanating from the RISC processor. The I/O buffers block (see "I/O Buffers" on page 71) mainly handles general-purpose digital I/O to/from the RISC processor along with level conversion for an RS-232 port. Also included in this block is an analog amplifier for amplifying/buffering the RSSI output. The interface acts as a conduit for the RSSI signal from the reciter, as the ASIF does not use this signal in any way.

The ethernet interface (see "Ethernet Interface" on page 74) contains an ethernet PHY chip together with line interface components. The PHY chip incorporates logic to format the ethernet signals from the RISC processor to a suitable format for line transmission. It also includes line drivers and receivers to convert the twisted pair ethernet signals to logic levels.

The audio and E&M interface (see "Audio and E&M Interface" on page 77) is jointly controlled by the RISC processor and the DSP. The E&M signalling is connected to the RISC processor. Audio data to/from the DSP

is converted to analog signals by a CODEC chip. However, the CODEC chip configuration is controlled by the RISC processor rather than the DSP.

The DSP block (see "DSP" on page 65) contains the DSP chip, which acts as a peripheral processor to the RISC processor. The RISC processor can communicate with the DSP through a host port interface, whereby the RISC processor can access the DSP's memory as though it existed in the RISC processor's memory space. The DSP block does not contain any memory external to the DSP chip itself.

Two high-speed serial ports provide I/O capabilities for the DSP; one connects to the CODEC in the audio interface, the other connects, via J102, to the DSP on the reciter board. The RISC processor can also connect to the reciter DSP through this same high speed serial port, but this interface is not presently used in the ASIF application.

The clock oscillator block contains a clock oscillator for the RISC processor and a clock buffer to buffer the clock from the reciter board before being fed to the DSP. The power supply block contains several power convertors that convert the incoming +28V supply to the various power supply voltages required by the ASIF circuitry. The power supply block also includes the power-on reset circuitry

#### 5.1.1 Connectors

On the rear panel of the ASIF there are three connectors for external I/O:

- DB9 connector, J103, connects to external digital I/O and a basic RS-232 serial port

- RJ45 connector, J104, connects the ethernet port

- RJ45 connector, J105, connects the 4W audio and E&M signalling port.

Although both J104 and J105 use the same type of connector, J105 is keyed to prevent its plug being accidentally inserted into J104. This prevents the potentially high voltages on the E&M lines from damaging the ethernet interface.

Along the top edge of the ASIF PCB there are two connectors for interfacing to the reciter:

- FFC connector J101 connects power and miscellaneous digital signals from the reciter along with serial ports from the reciter RISC

- PCB connector J102 connects signals through from the reciter DSP

Two further internal connectors are used for debug and program loading purposes:

- Micro-match connector J100 is used as the debug and program loading port for the RISC processor

- Micro-match connector J106 provides a JTAG interface to the DSP for software debug purposes

Connector J100 is fitted as standard as it is used for factory loading of the initial bootloader code. JTAG connector J106 is only fitted to prototype boards used for debugging of DSP code. It cannot be fitted to production boards as it is placed on the underside of the ASIF PCB; it is not possible to fit boards equipped with J106 on to the reciter heatsink.

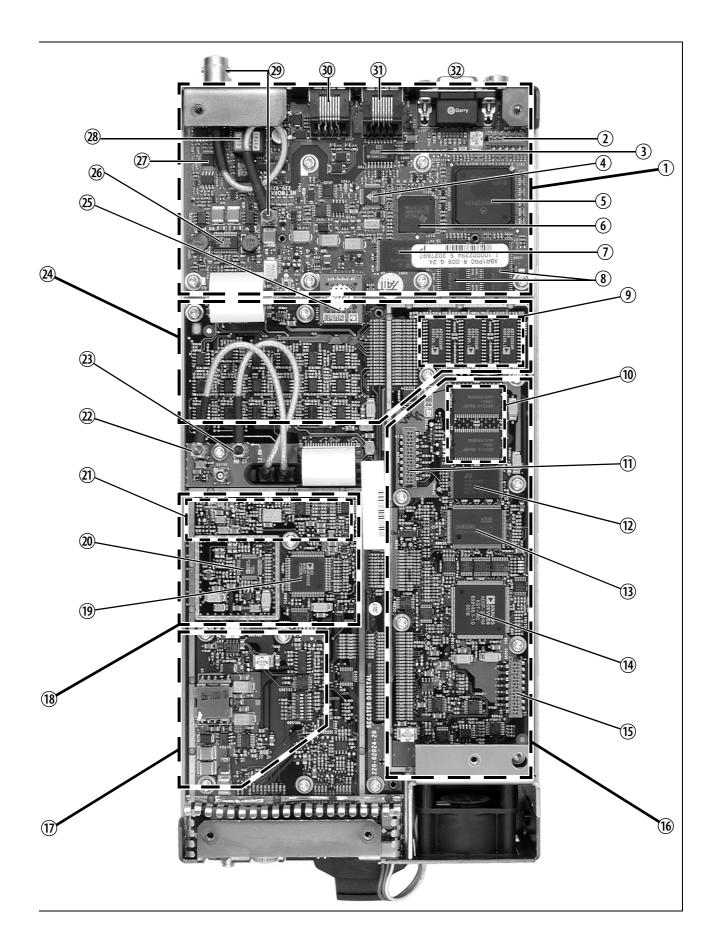

| 1          | ASIF PCB                               |

|------------|----------------------------------------|

| 2          | MPC859T JTAG connector (Power PC)      |

| 3          | Ethernet transformer                   |

| 4          | Ethernet PHI                           |

| (5)        | MPC859T (Power PC)                     |

| 6          | TMS320VC5510 DSP                       |

| $\bigcirc$ | flash memory                           |

| (8)        | RAM x 2                                |

| 9          | CODECs                                 |

| 10         | SRAM                                   |

| 1          | RISC JTAG connector (factory use only) |

| 12)        | flash memory                           |

| 13         | RISC                                   |

| (14)       | DSP                                    |

| (15)       | DSP JTAG connector (factory use only)  |

| (16)       | main digital system                    |

| 17         | power supply                           |

| 18         | digital IF and clock                   |

| (19)       | DDC                                    |

| 20         | ADC                                    |

| 21)        | 40MHz digital clock                    |

| 22         | 70.1 MHz IF and/or 16.9 MHz VHF        |

| 23         | 12.8MHz reference                      |

| 24)        | audio                                  |

| 25         | high speed data connector              |

| 26         | switching regulator                    |

| 27)        | analog line audio CODEC                |

| 28         | analog line isolating transformers     |

| 29         | 1 PPS sync                             |

| 30         | analog line RJ45 connector             |

| 31)        | Ethernet RJ45 connector                |

| 32)        | serial & digital I/O (DB9) connector   |

|            |                                        |

# 5.2 Risc Processor

#### 5.2.1 Risc Processor

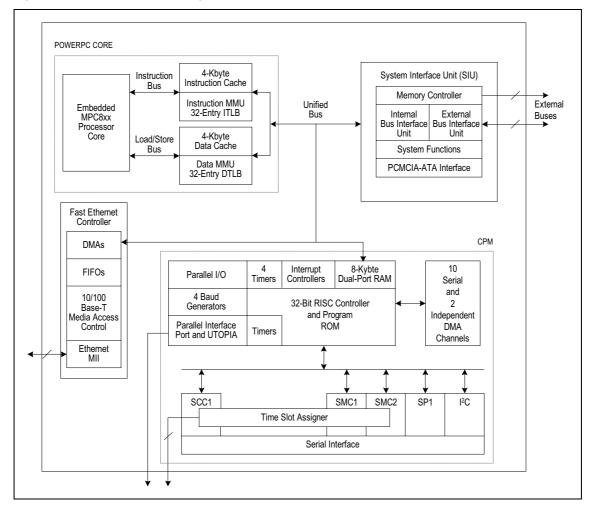

The main processor, U201, is a PowerQUICC MPC859TPZ133, hereafter abbreviated to MPC. This device consists of a PowerPC derived RISC processor in conjunction with a micro-coded RISC based Communications Processor Module (CPM). The RISC processor runs the main application program(s) under Linux while the CPM offloads the lower level processing of various serial communications protocols.

The MPC859T is a subset member of the MPC866 PowerQUICC communications processor family and has fewer communications interfaces compared to the full function MPC866 device ie. it provides only one serial communications controller (SCC), instead of the four fitted to the MPC866.

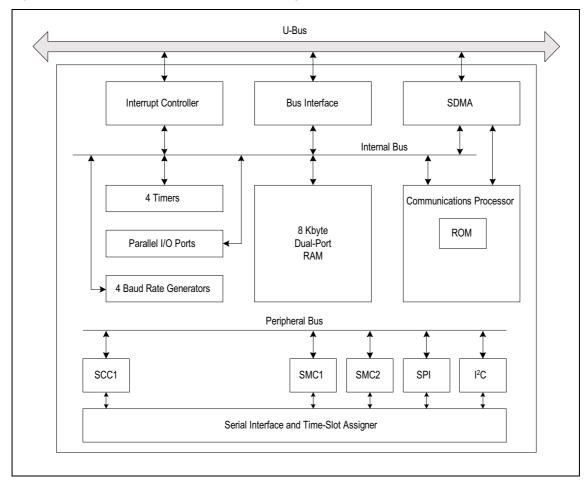

The block diagram (Figure 5.2) shows the internal structure; refer to the MPC866 data sheet (reference 1) and MPC866 user's manual (reference 2) for full details of the internal functions.

Figure 5.2 MPC859T Block Diagram

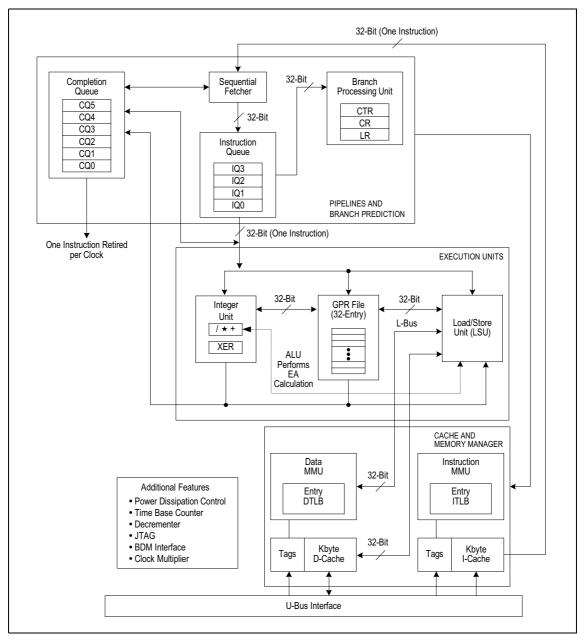

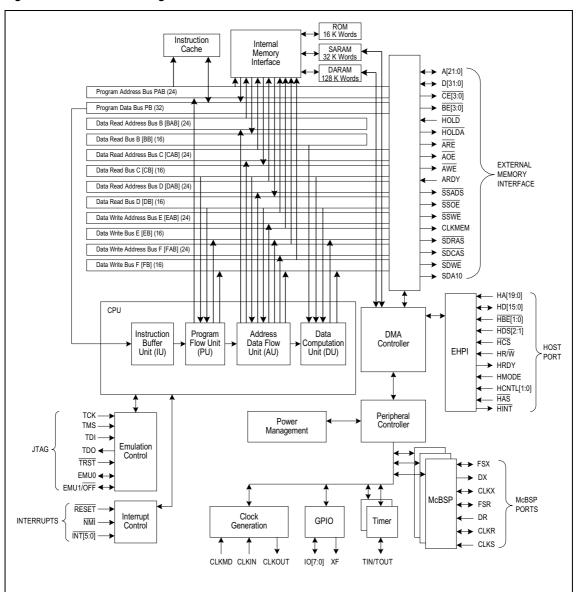

Figure 5.3 Processor Core Block Diagram

The RISC processor core is a PowerPC derivative implementing a full 32bit integer CPU architecture. Its RISC (reduced instruction set computer) architecture achieves a high level of performance through having a large number (32) of internal general-purpose registers and separate integer arithmetic and load/store (LSU) execution units, which allow several operations to occur simultaneously. The arithmetic unit performs all arithmetic and logical operations on data. The LSU handles data transfers both internally to the PowerPC and to external memory and peripherals.

The performance is further enhanced by pipelining instruction fetching and execution. Instructions are pre-fetched from memory and pre-decoded to

ensure that the execution units always have a continual flow of instructions. Static branch prediction minimizes disruptions in the instruction flow through the pipelines by pre-fetching instructions following on from a program branch.

A full description of the operation and instruction set of the RISC core is outside the scope of this document. It is recommended that the MPC866 user's manual (reference 2) be consulted for comprehensive coverage of the topic.

# Memory Caches and<br/>Memory ManagersOrdinarily, the fastest rate that the MPC can fetch data from external<br/>memory is one 32-bit instruction per two memory clock cycles. However,<br/>the CPU can execute two instructions per memory clock cycle since its<br/>internal clock is configured to be twice the memory clock (see "Clock<br/>Generation" on page 42 and "MPC Configuration" on page 45).<br/>Therefore, the CPU performance is restricted by the available transfer

bandwidth from its program memory.

To enable the CPU to run at full speed, internal cache memory, which enables fetching of data or instructions without wait states, is provided. The MPC859T includes separate instruction and data caches of 1kwords (4kbytes) each.

The CPU implements a Harvard architecture internally, ie. there are separate instruction and data caches, each with separate data and address buses. This allows data and instruction fetches from the caches to occur simultaneously. Although the internal structure of the instruction and data caches differs, they operate in an essentially similar fashion.

Considering instruction fetches only, when the CPU fetches an instruction word and that instruction is found within the instruction cache, then it can be retrieved without delay. Should the required instruction not be in cache then the cache issues a request to the SIU (see "System Interface Unit (SIU)" on page 42) to fetch that instruction from main memory. Actually, a total of four words is fetched in a burst fetch (see "SDRAM Burst Cycles" on page 64) since the cache memory is organized in lines of four words each, which are updated together.

If there is spare space in the cache, the new instruction data is stored in the cache. Otherwise, space must be cleared in the cache to enable the newly fetched data to be retained. To accomplish this, cache entries are examined to find the oldest entry using a least-recently-used (LRU) algorithm. The oldest cache entry thus found is discarded to make way for the new data.

The MPC provides memory management support for high-end operating systems through separate instruction and data memory managers. These translate the logical address from the RISC core into a real address used to access external memory and peripherals. Separate instruction and data memory managers support the Harvard architecture of the CPU but their outputs are combined into a single unified bus, ie. a von Neumann architecture, for external memory and peripheral accesses.

As well as address translation, the memory managers can apply protection attributes to areas of memory. The parameters for translation and protection are stored in tables in main memory. To speed up the translation process the most recently used parameters are stored in internal registers called Translation Lookaside Buffers; ITLB for the instruction memory manager and DTLB for the data memory manager.