# ADCs Approaching 100GSamples/s Ping Gui, Professor

Department of Electrical Engineering Southern Methodist University Dallas, TX, USA pgui@smu.edu

> Presented @ TWEPP 2017 UC Santa Cruz Sept. 11-15, 2017

TWEPP17

pgui@smu.edu

Application of high-speed high-sampling-rate ADCs

- The challenges and design techniques in high-speed ADC design

- Examples of State-of-the-art high-speed ADCs

## **The Demand for High-Speed ADCs**

- Applications

- High-bandwidth oscilloscopes

- 100/400Gb/s optical and backplane data links

- 5G Wireless communications

- Phased array systems for RADAR

- HEP experiments

- High sampling rate: GS/s to 100 GS/s

- Double (Nyquist rate) sampling (sampling rate being twice the bandwidth) allows for robust CDR, and equalization and spectrum engineering in DSP

- High bandwidth to accommodate high symbol rate

- ENOB: > 6 bit, SNDR > 37.8 dB

- Power consumption manageable

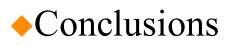

### PAM or QAM-based High-Speed Data Links

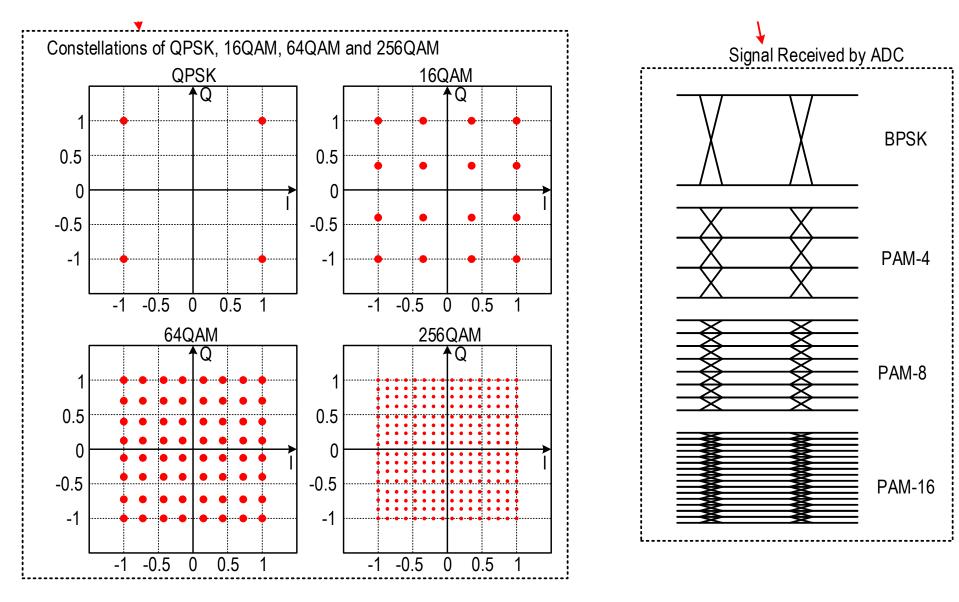

## **ADC/DAC Based Coherent Optical Transceiver**

[Image from Broadcom, ISSCC 2017]

## **Design Specifications and Challenges**

#### Analog-to-Digital Converter Requirements for 112 Gb/s Transmission

| Constellation | ADC<br>bandwidth | ADC<br>sampling rate | ADC<br>Effective number<br>of bits (ENOB) |

|---------------|------------------|----------------------|-------------------------------------------|

| 4-QAM         | 25GHz            | 50 Gsamples/s        | > 3.8                                     |

| 16-QAM        | 12.5GHz          | 25 Gsamples/s        | > 4.9                                     |

| 64-QAM        | 8.33 GHz         | 16.67 Gsamples/s     | > 5.7                                     |

| 256-QAM       | 6.25 GHz         | 12.5 Gsamples/s      | > 7.0                                     |

#### Analog-to-Digital Converter Requirements for 448 Gb/s Transmission

| Constellation | ADC<br>bandwidth | ADC<br>sampling rate | ADC<br>Effective number<br>of bits (ENOB) |

|---------------|------------------|----------------------|-------------------------------------------|

| 4-QAM         | 112GHz           | 224 Gsamples/s       | > 3.8                                     |

| 16-QAM        | 56GHz            | 112 Gsamples/s       | > 4.9                                     |

| 64-QAM        | 37 GHz           | 74 Gsamples/s        | > 5.7                                     |

| 256-QAM       | 28 GHz           | 56 Gsamples/s        | > 7.0                                     |

[Timo Pfau, Journal of Lightwave Technology, 2009]

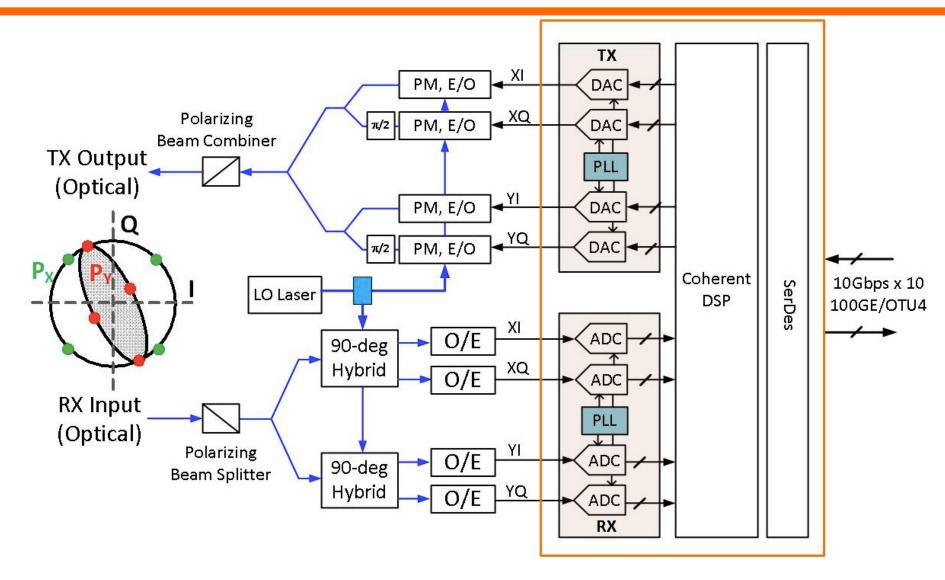

# How to Achieve such a High Sampling Rate

- Increasing  $f_s$  in a single ADC will hit a technological wall and make the power dissipation prohibitively high

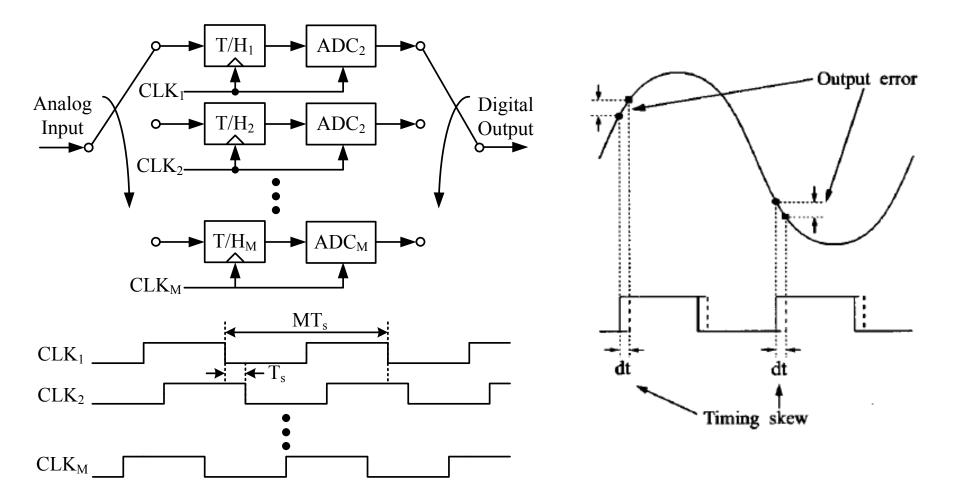

- Time-interleaved ADC is an effective method to increase sampling frequency  $f_s$ .

- Cycle through a set of *M* identical sub-ADCs

- Aggregate sample-rate is *M* times the sample-rate of the individual sub-ADCs

## **Introduction of Time-Interleaved ADCs**

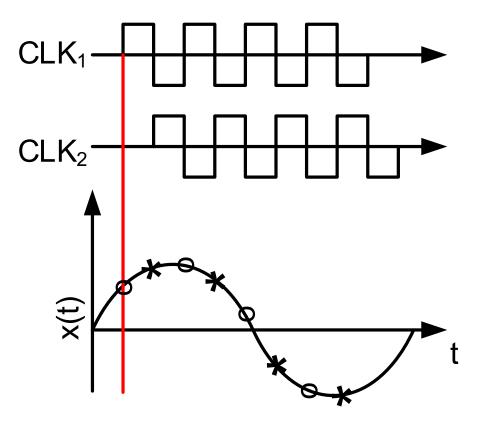

Scenario of first sub-ADC sampling the signal

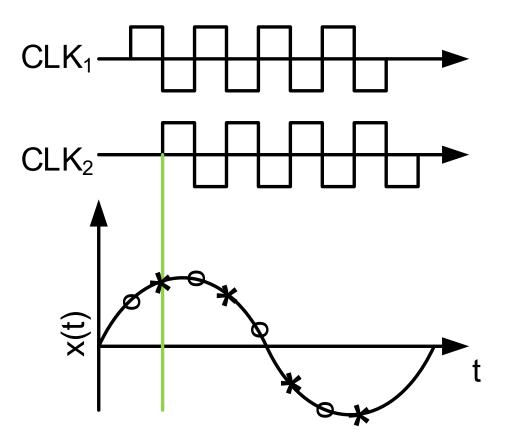

## **Introduction of Time-Interleaved ADCs**

Scenario of second sub-ADC sampling the signal

TWEPP17

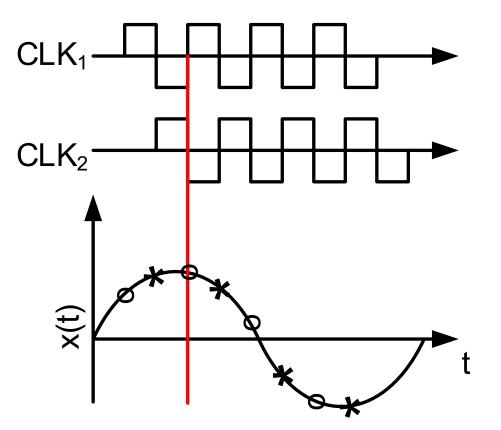

## **Introduction of Time-Interleaved ADCs**

And again, first sub-ADC samples the signal

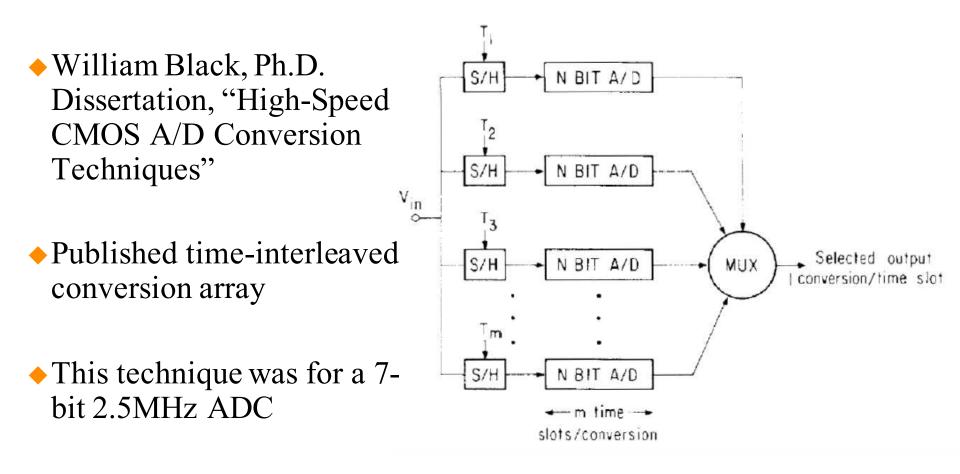

### Back in 1980s...

### Time-interleaved ADCs is still an active research area

## High-sampling rate ADCs

- Agilent 2003: 80-way interleaved 20 GS/s

- •Fujitsu 2009: 4-way interleaved 56 GS/s

- •Nortel 2010: 16-way interleaved 40 GS/s

- •IBM 2014: 64-way interleaved 90 GS/s

- •Broadcom 2017, 64-way interleaved 4 x 64GS/s

• • • • •

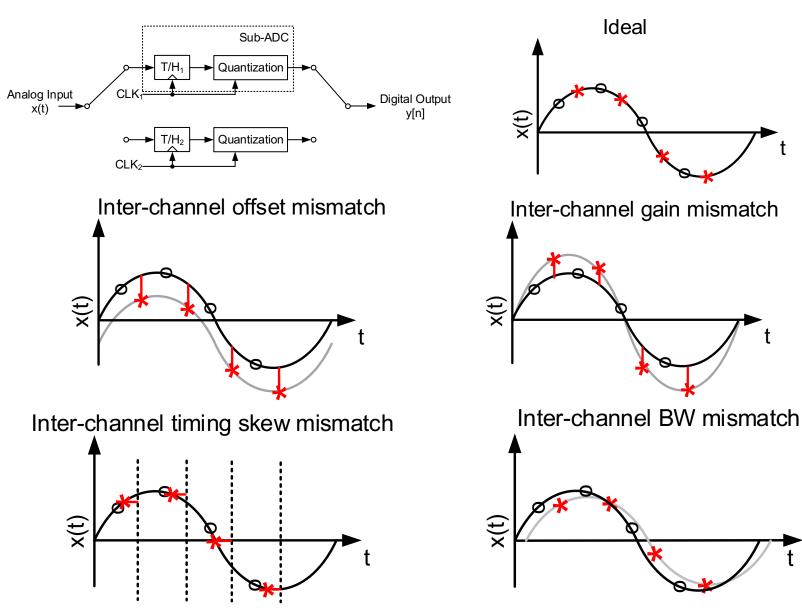

### **Inter-Channel Mismatches**

TWEPP17

pgui@smu.edu

Inter-channel mismatches calibration

Gain, Offset, Timing skew, Bandwidth, (nonlinearity)

High-speed front-end Track/Hold (T/H)

Low-power and high-speed of sub-ADC channels

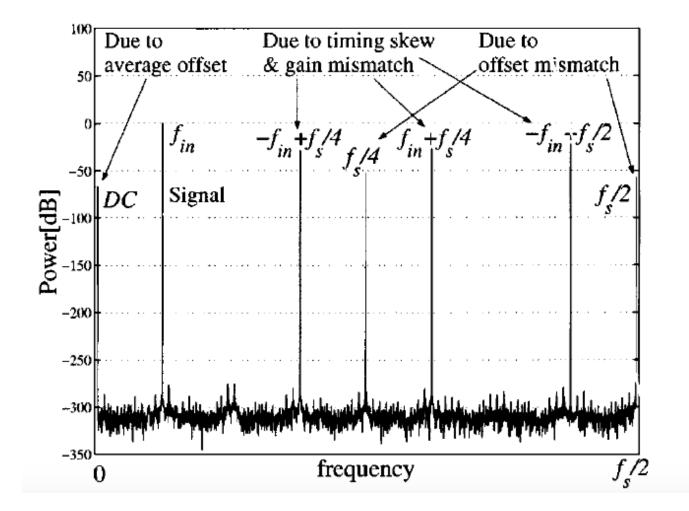

### Inter-channel Mismatches

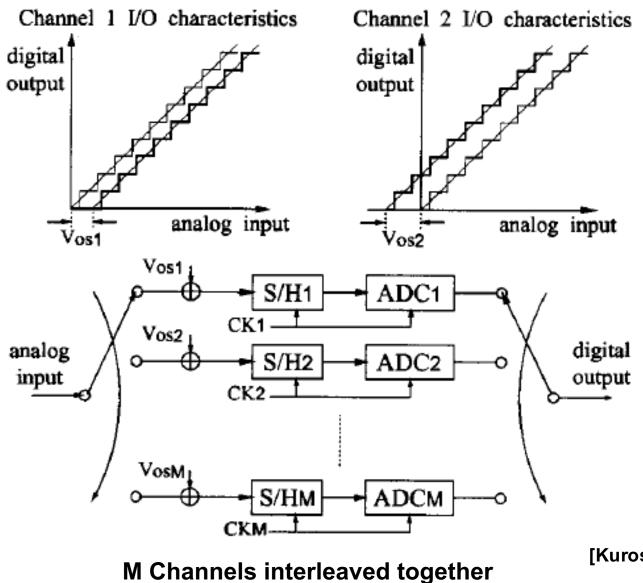

### **Offset Mismatch Effect**

[Kurosawa, TCAS-I 2001]

TWEPP17

pgui@smu.edu

### **Offset Mismatch Effect**

**Spurious tone frequencies:**

$$f_{noise} = k \times \frac{f_s}{M}$$

M = number of channels, e.g. 4 k = 1,2,3,...[Kurosawa, TCAS-I 2001]

#### TWEPP17

#### pgui@smu.edu

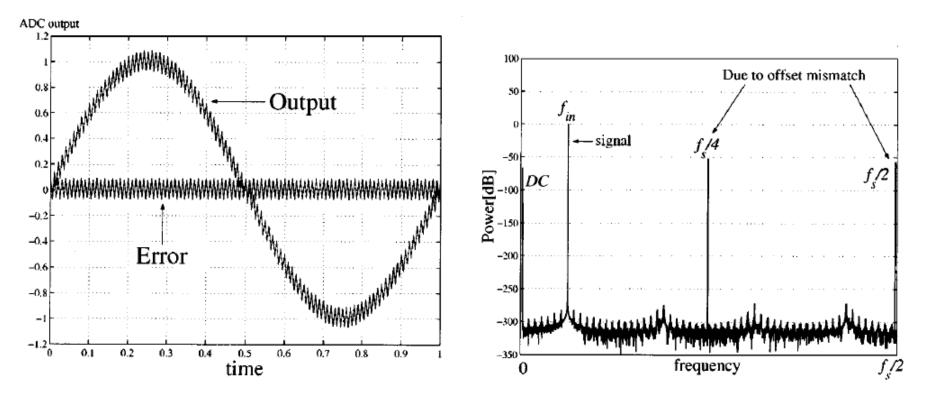

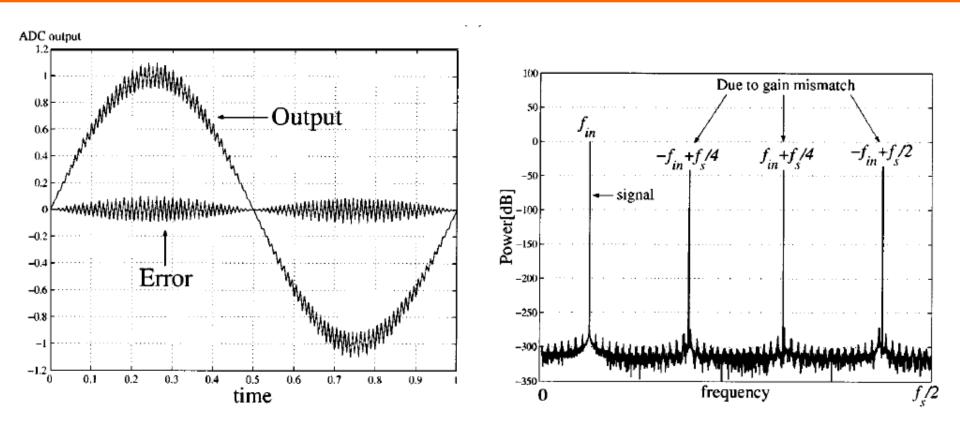

### **Gain Mismatch Effect**

### **Gain Mismatch Effect**

**Spurious tone frequencies:**

$$f_{noise} = \pm f_{in} + k \times \frac{f_s}{M}$$

TWEPP17

M = number of channels, e.g. 4

$$k = 1, 2, 3, \dots$$

[Kurosawa, TCAS-I 2001] pgui@smu.edu

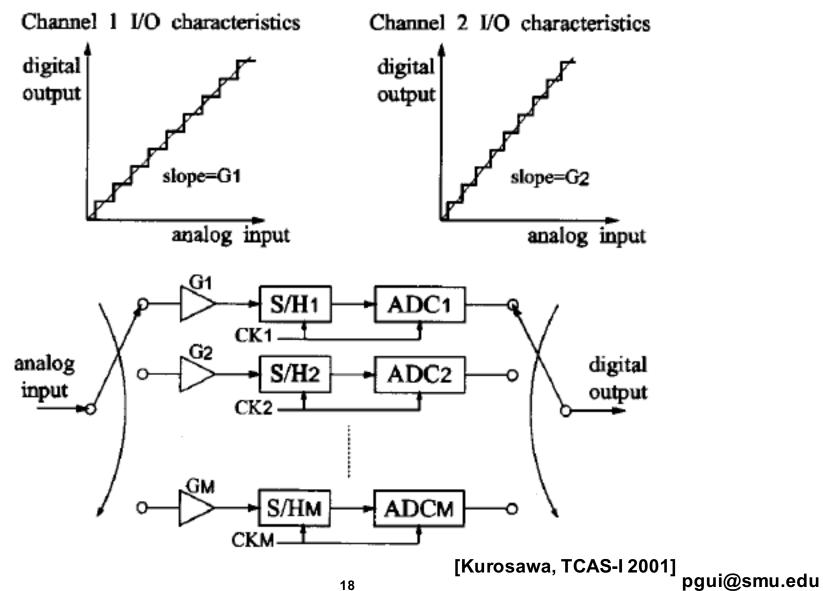

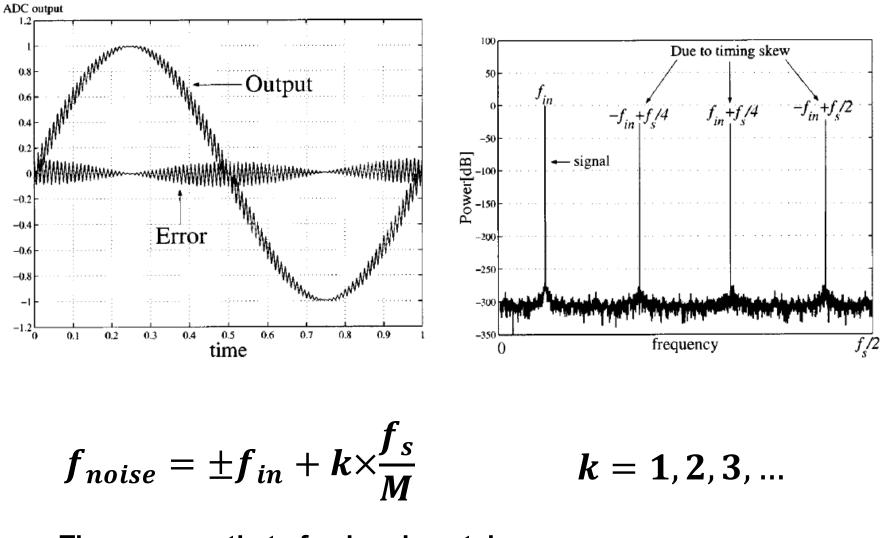

### **Timing Skew Error Effect**

TWEPP17

[Kurosawa, TCAS-I 2001] pgui@smu.edu

### **Timing Skew Error Effect**

The same as that of gain mismatches

**TWEPP17**

[Kurosawa, TCAS-I 2001] pgui@smu.edu

- The effect of BW mismatches are similar to that caused by the combination of

- Gain mismatch effects

- Timing skew (Phase) error effects

### **Aggregate Mismatches Effects**

All these will limit ADC performance

TWEPP17

Careful design and layout

Mismatches always exist due to PVT variations, clock distribution networks, stray capacitance, etc.

Calibration

Analog calibration

- Digital calibration

- Foreground calibration

- Background calibration (can track PVT variations)

Offset, Gain, Timing skew mismatches (analog and digital)

BW mismatches (digital domain)

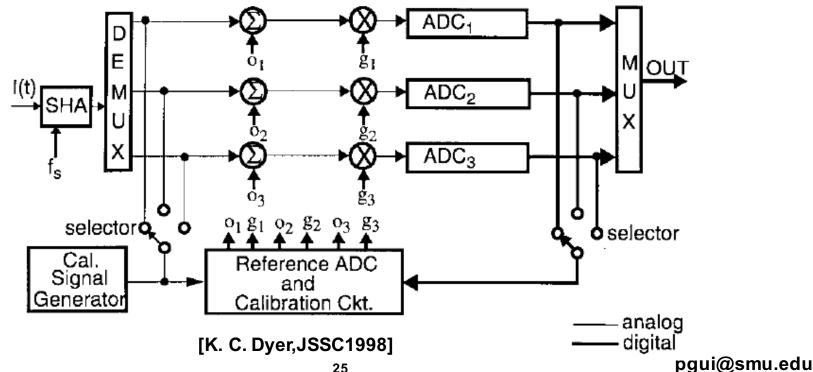

# **Analog Calibration for Gain/Offset Mismatches**

- A reference ADC is used to convert the same input

- Comparing selected ADC channel result with reference ADC result

- Estimate offset and gain mismatch by LMS algorithm

- Offset error can be calibrated by adjusting the comparator offset of each channel

- Gain error can be calibrated by adjusting the reference voltage

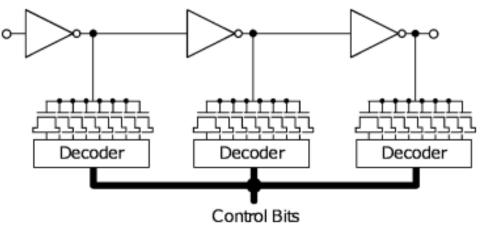

## **Analog Calibration for Timing Skew Mismatch**

• Digital controlled capacitor bank to control the delay

[M. E.-Chammas, JSSC2011]

Phase Interpolator or DLLs to produce clocks with different delays

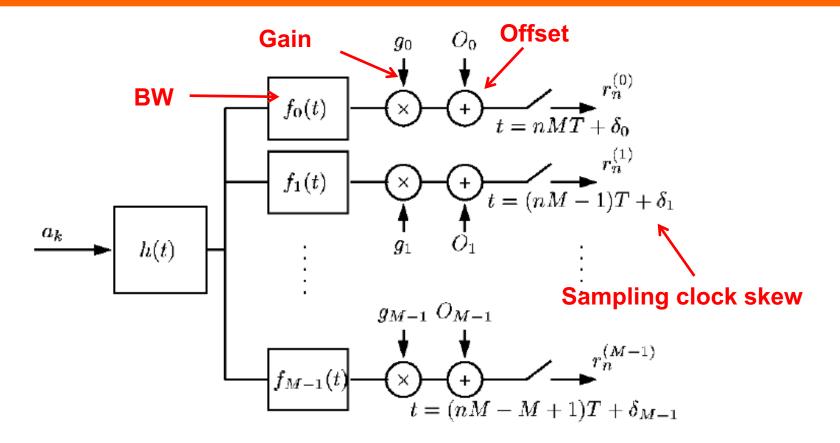

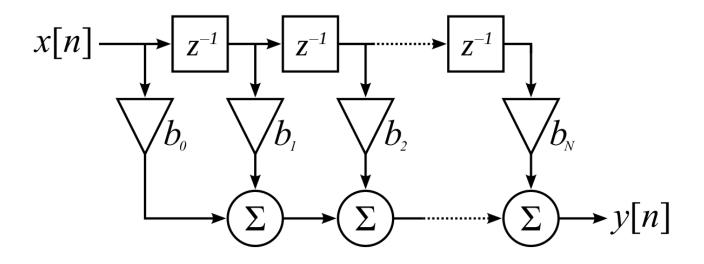

### **Digital Calibration for Inter-Channel Mismatches**

pgui@smu.edu

h(t): channel response at input, i.e. input buffer and etc. *f*<sub>0</sub>(t): frequency response of T/H *g*<sub>0</sub>: gain error; *O*<sub>0</sub>:offsets; δ<sub>0</sub>:sampling time error

TWEPP17

[Clariphy, ISCAS 2006]

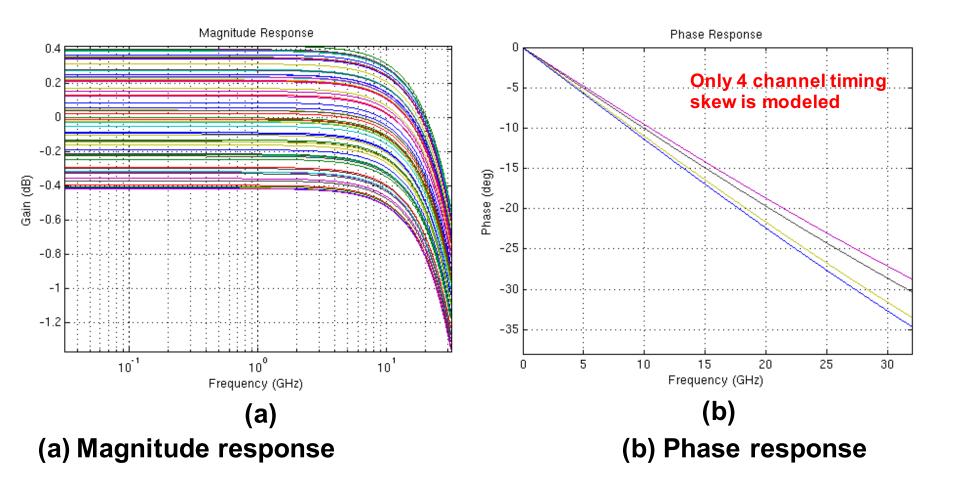

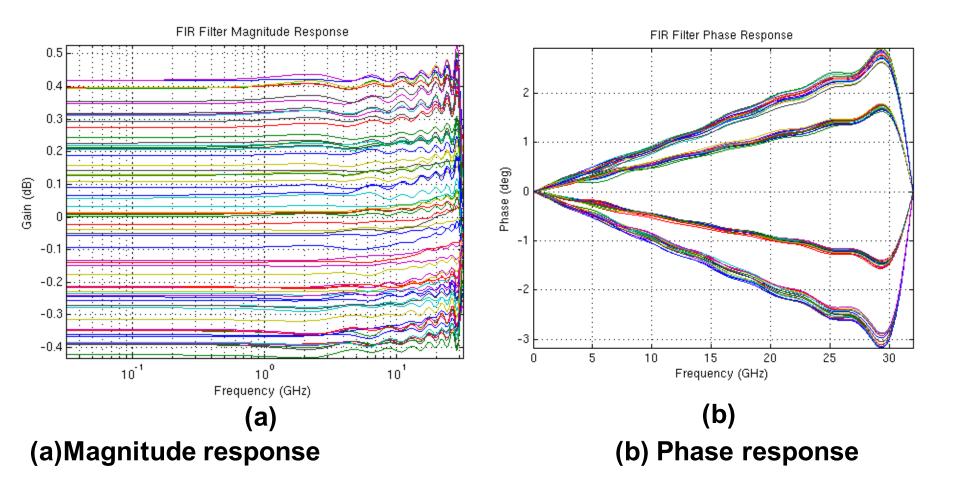

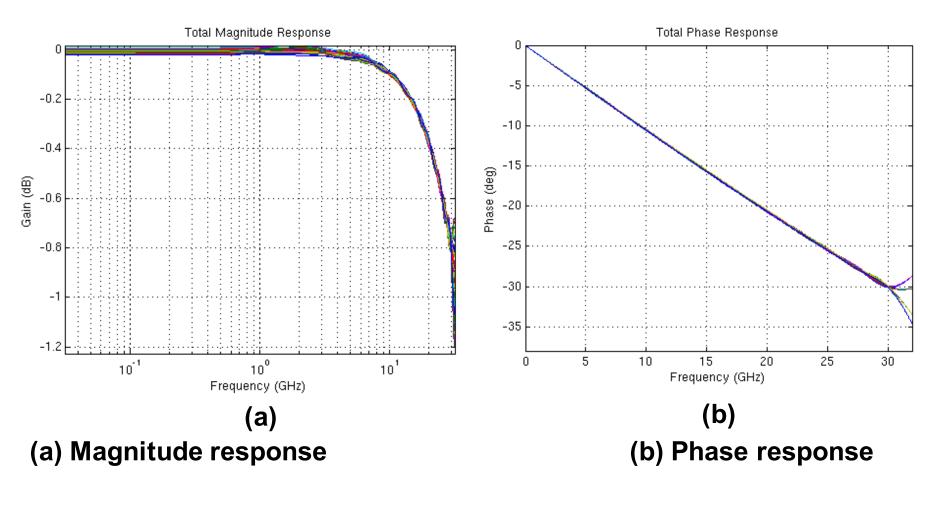

- Mismatches calibration can be formulated as equalization problem for M-input-M-output

- Offset, gain, timing skew, and bandwidth mismatches are compensated by FFE (FIR filters) or DFE

- Coefficients of FIR filters are estimated by collecting the conversion results of single-tone training signals of frequencies and best curve fitting.

FFE (FIR filters)

### Transfer function of M channels

### Transfer function Equalizer (FIR) of each channel

TWEPP17

## M-Channel + Equalizer

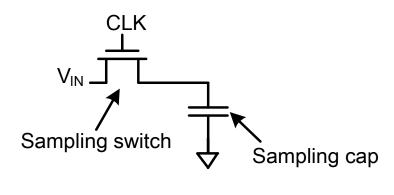

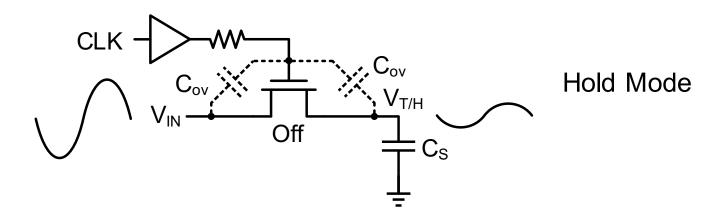

## Front-end High-Speed T/H

Front-end high-speed T/H

•Even with interleaving, the front-end T/Hs still need to operate at multi-GHz frequency

•Input bandwidth needs to be high

•Other T/H non-idealities

- kT/C noise

- Finite acquisition time (RC constant of the switches)

- Track mode nonlinearity,  $R=f(V_{in})$

- Signal dependent sampling instant

- Sampling aperture uncertainty

- Clock feedthrough and charge injection

• • • • • •

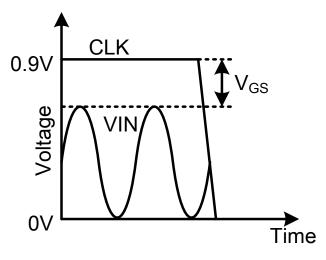

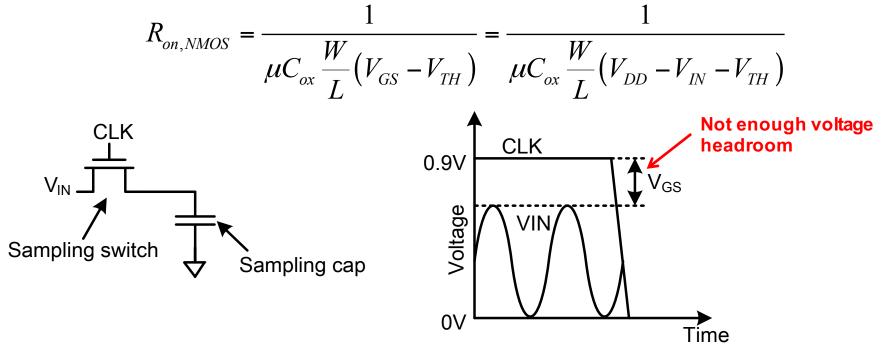

### **Track Mode Nonlinearity**

## $\bullet$ Problem: R<sub>on</sub> is modulated by V<sub>IN</sub>

$$R_{on,NMOS} = \frac{1}{\mu C_{ox} \frac{W}{L} (V_{GS} - V_{TH})} = \frac{1}{\mu C_{ox} \frac{W}{L} (V_{DD} - V_{IN} - V_{TH})}$$

TWEPP17

Output tracks well when input voltage level is low

It gets distorted when voltage is high due to increase in R<sub>on</sub>

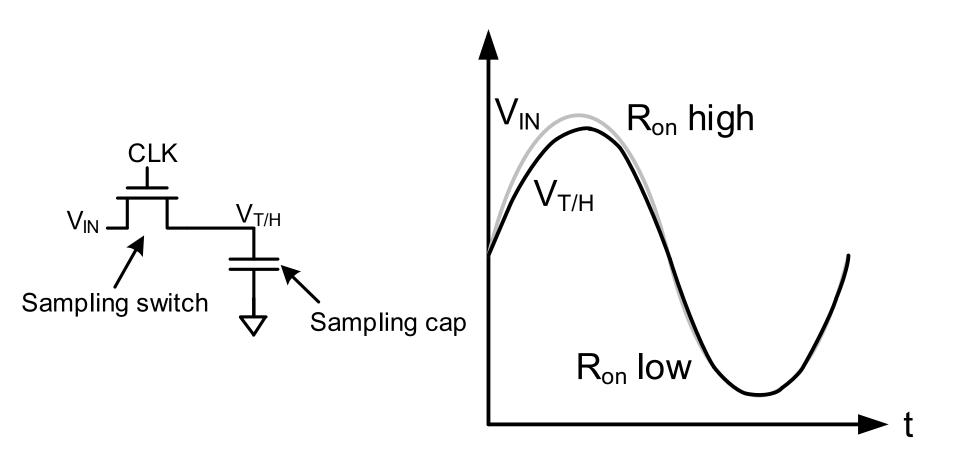

## **Clock Feedthrough and Charge Injection**

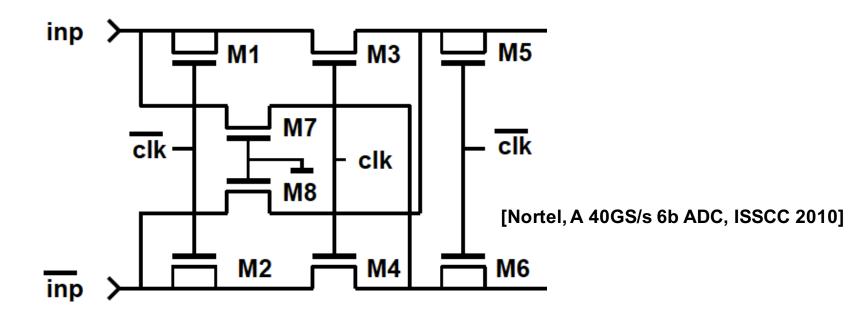

## A Basic Front-End T/H

- M3 & M4: sampling switch

- M1 & M2: clock feedthrough and charge injection cancellation

- M5 & M6: clock feedthrough and charge injection cancellation

- M7 & M8: signal feedthrough cancellation

- Differential structure to cancel HD2 and some offset

## **Front-End T/H: Achieving High BW**

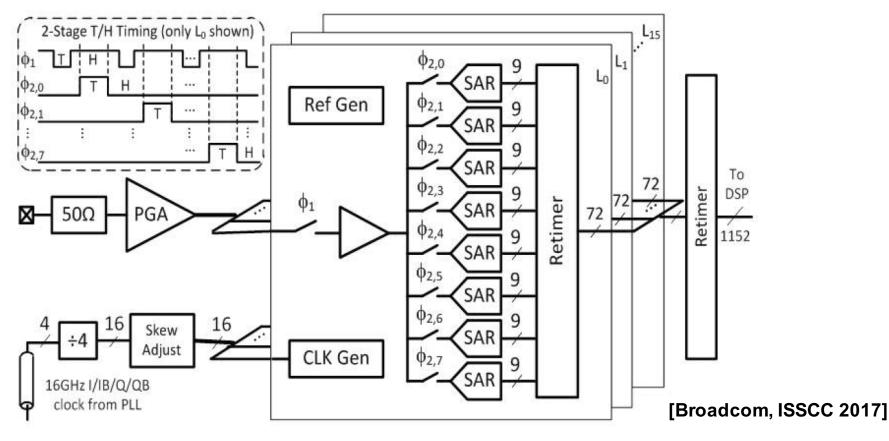

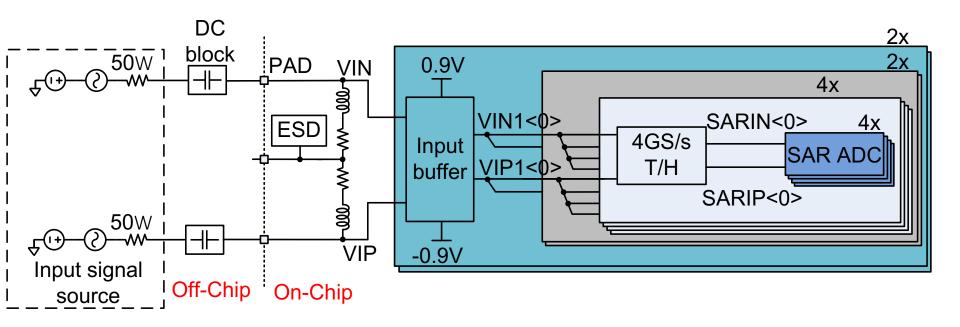

- Hierarchical sampling architecture for a high degree of interleaving

- BW limited by the heavy load from all of parallel sub-ADCs

- Large amount of power on distributing low jitter clocks to all parallel sampling switches

- Two-stage interleaving to improve the bandwidth and keep the jitter low

64 GS/s ADC in 2-stage (16 x 8) T.H with 128 unit-SARs

### High BW techniques:

- Parasitic capacitance of multi-GS/s T/H circuits used as sampling capacitor

- Input buffer to present low impedance to the sampling switches

- Inductive peaking added at the inputs to extend the bandwidth

- ESD-diodes at the common-mode node to reduce input parasitic capacitance

# **Challenge in Obtaining Good SNR**

- Not enough voltage headroom to turn on switch

- Limiting the input signal swing and affecting the SNR

- Large signal swing would cause large variations in the on-resistance of the switch, resulting in nonlinearity.

• Turned-on resistance can be expressed as

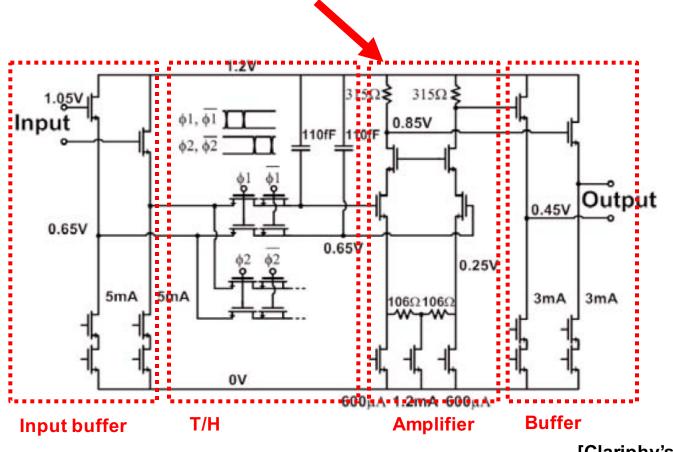

# Solution to the SNR Challenge

•Sampled signal is amplified before being sent to subchannel ADCs

[Clariphy's 20GS/s 6b ADC]

[Clariphy, a 50Gb/s DP-QPSK/BPSK transceiver, ISSCC 2012]

**TWEPP17**

# Sub-ADC Design

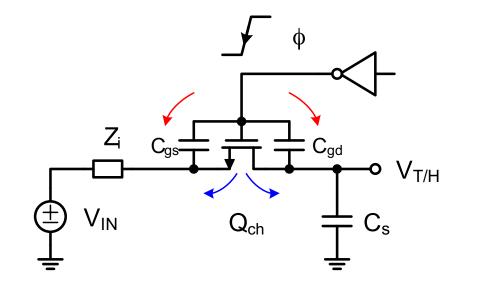

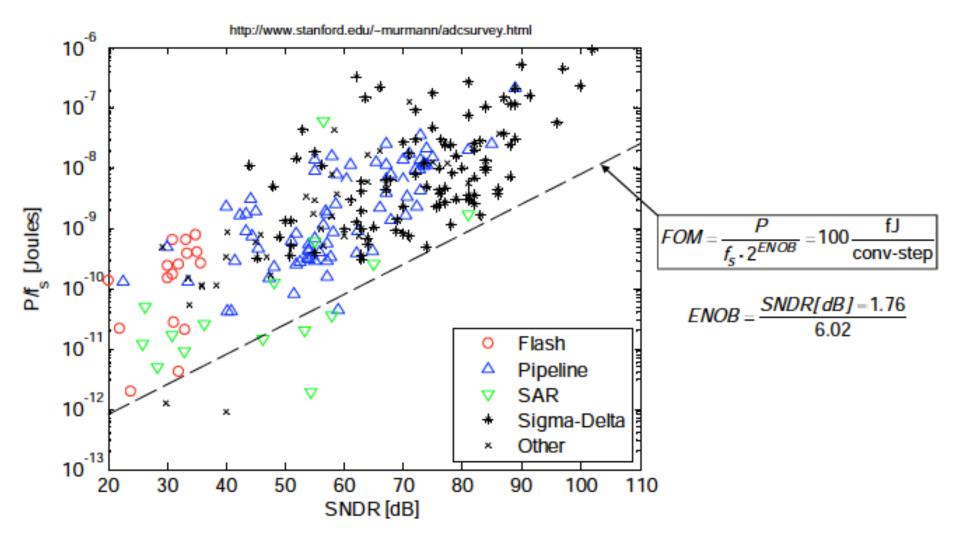

## **Sub-ADC** Architectures

[Image from B. Murmann notes]

Low power operation and small silicon area are the key factors since there are many channels of them

# SAR is the choice as sub-ADC

• Pros

Power efficient, no static current consumption

Compatible with technology scaling

•Can handle rail to rail signal swing, relaxing noise requirement.

Device nonlinearity is not of concern

Cons

Sequential operation tends to limit the conversion speed

• Capacitor and comparator mismatch could lead to distortion.

# Further improving the SAR speed

# Further optimizing the power dissipation of SAR

# Comparator offset calibration Optional for SAR ADCs with single comparator Most advanced design employs multiple comparators, then comparator offset calibration is necessary

# DAC capacitor calibration

• Low-power and high-speed operation requires capacitor to be small

• Capacitor mismatch arise due to small size

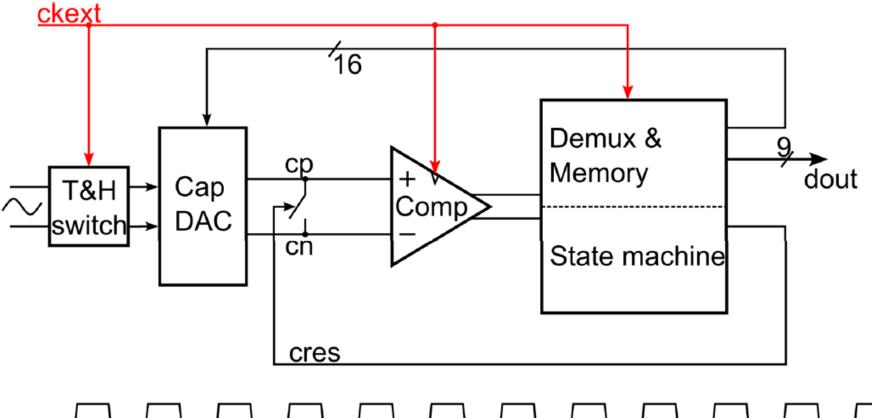

# **Conventional Synchronous SAR**

## ckext///1/2/3/4/5/6/7/8/9/cal/ |Track|

A high speed external clock, Fs\*(N+1), controls operation of every bit

The duration of every bit conversion is determined by the slowest bit

TWEPP17

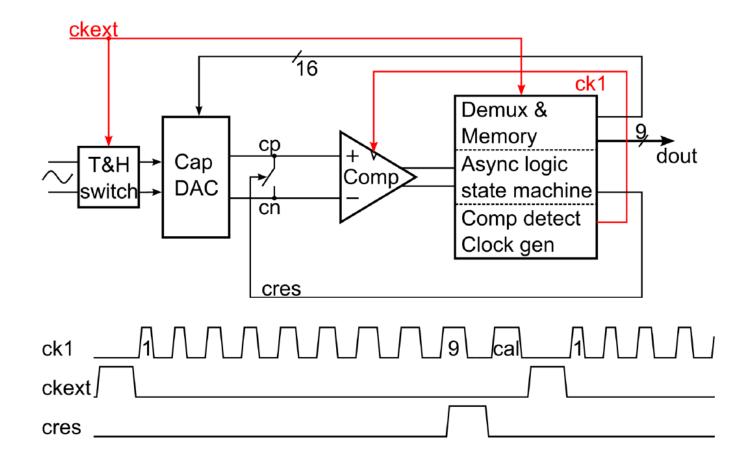

## **Asynchronous SAR**

- Improving speed and reducing power dissipation of clocks

- No external high-speed clock.

- The operation of every bit is determined by the completion of the previous bit

#### TWEPP17

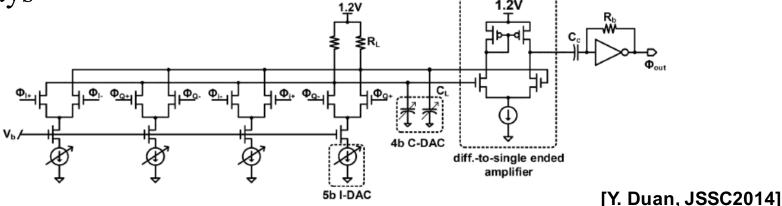

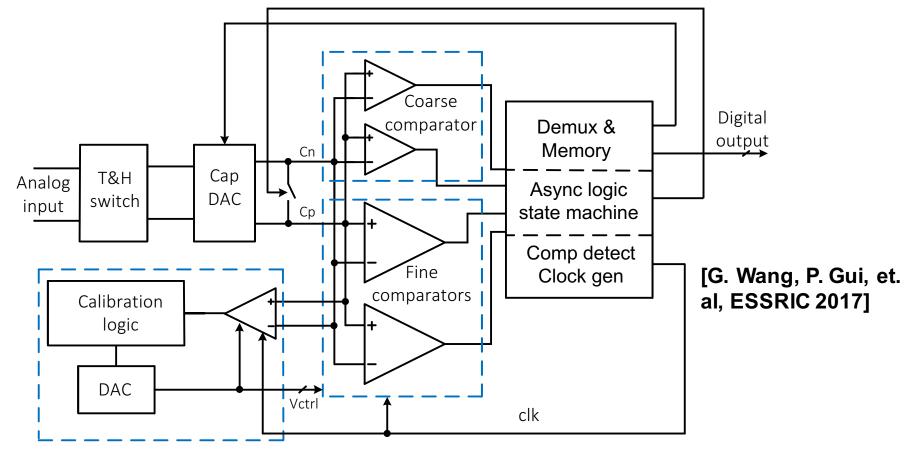

#### Asynchronous SAR with Improved Speed and Optimized Power

- Alternating comparators for speed improvement

- Coarse and fine comparators for power optimization

- Sub-binary DAC to improve error tolerance

- Offsets between the comparators are calibrated in background

TWEPP17 1G/s 8-bit 3.2mW/channel, 43.6db in SNDR, 6.95b ENOB

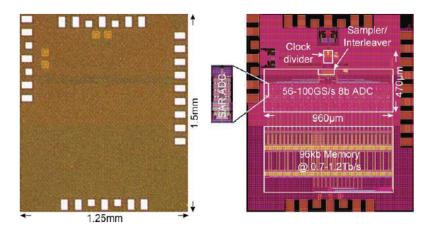

# IBM 90GS/S 8-bit ADC in 32nm SOI

- BW: 22GHz

- ◆ 5.7b ENOB@6.1GHz

- 5.2b ENOB@19.9GHz

- Power dissipation: 667mW

- ♦ 64 ADC channels operating at 1.4GS/s

[IBM, a 90GS/s 8b ADC, ISSCC 2014]

- Foreground analog calibration

- Offset mismatch

- Subtracted from digital conversion results

- Gain mismatch

- Tuning the associated reference voltage of sub-channel ADCs

- Timing skew mismatch

- Tuning the sampling clock skew

- Bandwidth mismatch is not calibrated.

**TWEPP17**

# UC Berkeley's 46GS/s 6-bit ADC in 28nm FDSOI

#### • BW: 23 GHz

- ◆ 4.2b ENOB @ low frequency

- ◆ 3.9b ENOB @ 23.5GHz

- Power dissipation: 381mW

- 72 ADC channels operating at 0.64GS/s

[UC Berkeley, VLSI 2015]

- Foreground inter-channel mismatch calibration

- Offset mismatch

- Adjusting comparator offset

- Gain mismatch

- Adjusting the reference voltage of sub-channel ADCs

- Timing skew mismatch

- Using variable delay lines

- Bandwidth mismatch not calibrated

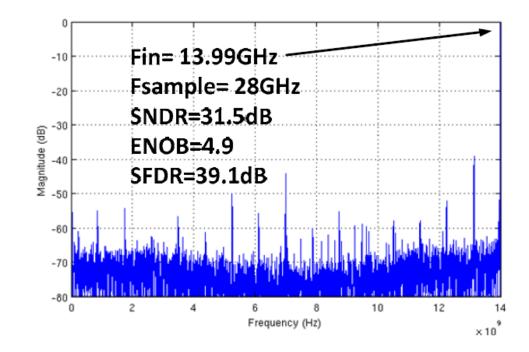

# Xilinx's 28 GS/s 8-bit ADC in 16nm FinFET

- BW: 14 GHz

- ◆ 5.5b ENOB @ 0.18GHz

- ◆ 4.9b ENOB @ 14GHz

- Power dissipation: 280mW

- 32 ADC channels operating at 0.875GS/s

[Xilinx, VLSI 2016]

- Background and foreground calibration

- On-chip calibration of timing skew, gain and offset

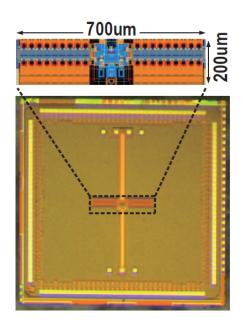

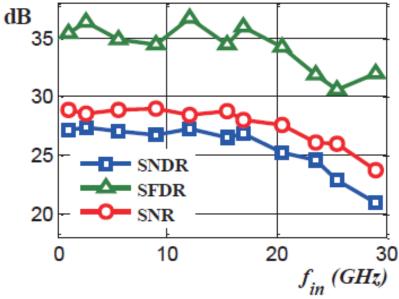

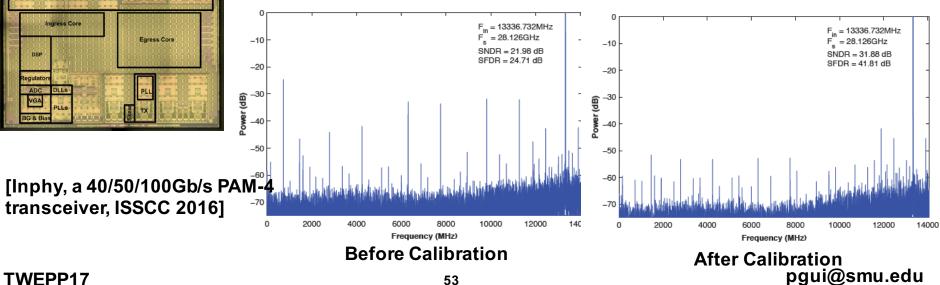

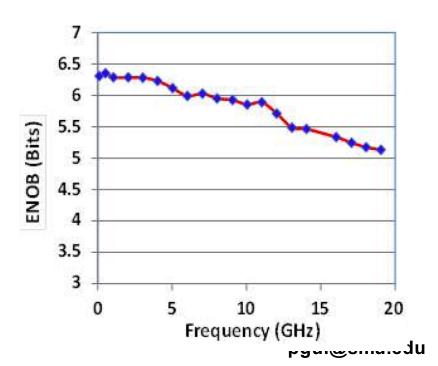

# Inphy 28 GS/s 8-bit ADC in 28nm CMOS

- ♦ BW: 18GHz

- ◆ 5.8b ENOB@1GHz

CAUI – 4 Host Interface

- 5.0b ENOB@13.3GHz

- Power dissipation:165mW

- 32 ADC channels each operating at 0.875GS/s

- Background & foreground calibration

- Offset mismatch

- Estimated by computing the average of single channel results and corrected in DSP

- Gain mismatch

- Envelop detection of the gain error and calibrated by tuning the gain of sub-channel ADCs

- Residual gain mismatch is corrected in DSP

- Timing skew mismatch

- Tuning the delay cell in side the CLK w/ 200fs res.

- Bandwidth mismatch corrected by FFE in DSP

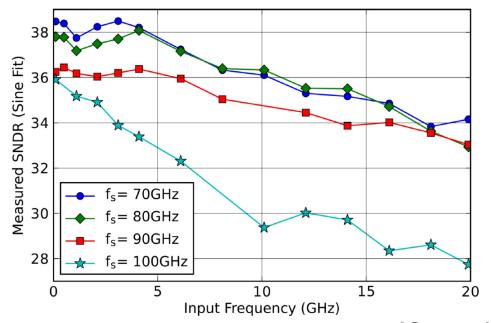

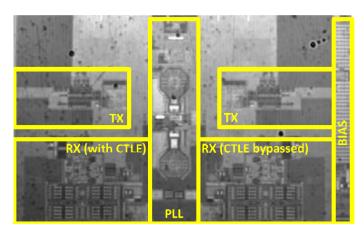

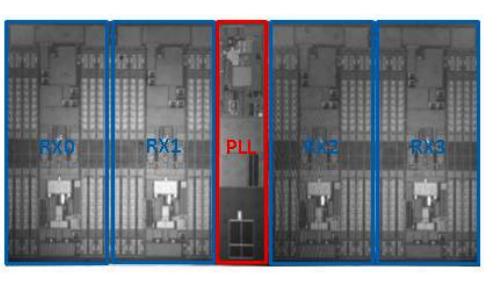

# Broadcom 4 x 64GS/s 8-bit ADC in 20nm CMOS

- ◆ 5.95b ENOB @ 8GHz,

- ◆ 5.3b ENOB @ 16GHz

- Power dissipation of each 64GS/s ADC : 950mW

- 128 ADC interleaved

- Each operating 500 MS/s

- Timing skew adjustment circuit with coarse and fine tuning

- On-chip calibration loops are used to cancel the gain, offset, and timing skew

- Foreground calibration of comparator offset

- Bandwidth mismatches not calibrated

[Broadcom, ISSCC 2017]

TWEPP17

# Conclusions

Time-interleaving is an effective way to design highsampling-rate ADCs

ADCs have been design in CMOS with sampling rate approaching 100GS/s

Analog and Digital Calibration for inter-channel mismatches calibration

• Front-end high-speed T/H

• Sub-ADCs operating at low power and GS/s

## Acknowledgement

# Thank You!

## Reference

- 1. S.-W. M. Chen and R. W. Brodersen, "A 6-bit 600-MS/s 5.3 mW asynchronous ADC in 0.13um CMOS", *IEEE J. Solid-State Circuits*, vol. 41, no. 12, pp. 2669-2680, 2006

- 2. T. Jiang, W. Liu, F. Y. Zhong, C. Zhong, K. Hu and P.Y. Chiang, "A single-channel, 1.25-GS/s, 6-bit, 6.08-mW asynchronous successiveapproximation ADC with improved feedback delay in 40-nm CMOS", *IEEE J. Solid-State Circuits*, vol. 47, no. 10, pp. 2444-2453, 2012

- 3. Ginsburg , B. P.; Chandrakasan, A. P. "500-MS/s 5-bit ADC in 65-nm CMOS With Split Capacitor Array DAC", *Solid-State Circuits, IEEE Journal of,* On page(s): 739 747 Volume: 42, Issue: 4, April 2007

- 4. C.-C. Liu, S.-J. Chang, G.-Y. Huang and Y.-Z. Lin, "A 10-bit 50-MS/s SAR ADC with a monotonic capacitor switching procedure", *IEEE J. Solid-State Circuits*, vol. 34, no. 5, pp. 731-740, 2010

- 5. Guerber, J.; Venkatram, H.; Gande, M.; Waters, A.; Moon, U. "A 10-b Ternary SAR ADC With Quantization Time Information Utilization", *Solid-State Circuits, IEEE Journal of*, On page(s): 2604 2613 Volume: 47, Issue: 11, Nov. 2012

- Kull, L.; Toifl, T.; Schmatz, M.; Francese, P.A.; Menolfi, C.; Brandli, M.; Kossel, M.; Morf, T.; Andersen, T.M.; Leblebici, Y. "A 3.1 mW 8b 1.2 GS/s Single-Channel Asynchronous SAR ADC With Alternate Comparators for Enhanced Speed in 32 nm Digital SOI CMOS", *Solid-State Circuits, IEEE Journal of*, On page(s): 3049 3058 Volume: 48, Issue: 12, Dec. 2013

- 7. M. Miyahara, Y. Asada, D. Paik and A. Matsuzawa, "A low-noise self-calibrating dynamic comparator for high-speed ADCs", *Proc. IEEE Asian Solid-State Circuits Conf.*, pp. 269-272, 2008

- 8. N. Le Dortz, "A 1.62 GS/s time-interleaved SAR ADC with digital background mismatch calibration achieving interleaving spurs below 70 dBFS", *IEEE ISSCC Dig. Tech. Papers*, pp. 386-388, 2014

- Schinkel, Daniel; Mensink, Eisse; Klumperink, Eric; van Tuijl, Ed; Nauta, Bram "A Double-Tail Latch-Type Voltage Sense Amplifier with 18ps Setup+Hold Time", Solid-State Circuits Conference, 2007. ISSCC 2007. Digest of Technical Papers. IEEE International, On page(s): 314-605

- 10. Choo, Kyojin D.; Bell, John; Flynn, Michael P "27.3 Area-efficient 1GS/s 6b SAR ADC with charge-injection-cell-based DAC", *Solid-State Circuits Conference (ISSCC)*, 2016 IEEE International, On page(s): 460-461

- 11. Hyeok-Ki Hong, Wan Kim, Hyun-Wook Kang, Sun-Jae Park, Michael Choi, Ho-Jin Park, Seung-Tak Ryu, "A Decision-Error-Tolerant 45 nm CMOS 7b 1 GS/s Nonbinary 2b/Cycle SAR ADC", *Solid-State Circuits IEEE Journal of*, vol. 50, pp. 543-555, 2015, ISSN 0018-9200.

- 12. Chi-Hang Chan, Yan Zhu, Iok-Meng Ho, Wai-Hong Zhang, Seng-Pan U, Rui Paulo Martins " A 5mW 7b 2.4GS/s 1-then-2b/cycle SAR ADC with Background Offset Calibration", *Solid-State Circuits Conference Digest of Technical Papers (ISSCC) 2017 IEEE International,* pp. 282-283, 2017, ISSN 2376-8606.

- 13. L. Kull, et al., ISSCC Tech. Dig., pp 378-380, 2014.

- 14. Y. Duan, et al., :A 6b 46GS/s ADC with >23GHz BW and Sparkle-Code Error Correction", IEEE VLSI Tech. Dig., pp 162-163, 2015.

- 15. Y. Frans et al., "A 56Gb/s PAM4 wireline transceiver using a 32-way time-interleaved SAR ADC in 16nm FinFET,"*IEEE Symp. VLSI Circuits*, June 2016.

- 16. M. Q. Le et al., "A background calibrated 28GS/s 8b interleaved SAR ADC in 28nm CMOS," *IEEE CICC*, Apr. 2017.

#### TWEPP17