# ECE 477 Final Report – Spring 2010 Team 6 – Digital Sound Projection

# **Team Members:**

| #1: Steve Anderson | Signature: | <b>Date:</b> 05/05/2010 |

|--------------------|------------|-------------------------|

| #2: Mike Goldfarb  | Signature: | <b>Date:</b> 05/05/2010 |

| #3: Shao-Fu Shih   | Signature: | <b>Date:</b> 05/05/2010 |

| #4: Josh Smith     | Signature: | <b>Date:</b> 05/05/2010 |

| CRITERION               | SCORE                  | MPY   | PTS |

|-------------------------|------------------------|-------|-----|

| Technical content       | 0 1 2 3 4 5 6 7 8 9 10 | 3     |     |

| Design documentation    | 0 1 2 3 4 5 6 7 8 9 10 | 3     |     |

| Technical writing style | 0 1 2 3 4 5 6 7 8 9 10 | 2     |     |

| Contributions           | 0 1 2 3 4 5 6 7 8 9 10 | 1     |     |

| Editing                 | 0 1 2 3 4 5 6 7 8 9 10 | 1     |     |

| Comments:               |                        | TOTAL |     |

|                         |                        |       |     |

|                         |                        |       |     |

# **TABLE OF CONTENTS**

| Abstract                                                    | 1          |

|-------------------------------------------------------------|------------|

| 1.0 Project Overview and Block Diagram                      | 2          |

| 2.0 Team Success Criteria and Fulfillment                   | 6          |

| 3.0 Constraint Analysis and Component Selection             | 7          |

| 4.0 Patent Liability Analysis                               | 12         |

| 5.0 Reliability and Safety Analysis                         | 17         |

| 6.0 Ethical and Environmental Impact Analysis               | 21         |

| 7.0 Packaging Design Considerations                         | 25         |

| 8.0 Schematic Design Considerations                         | 30         |

| 9.0 PCB Layout Design Considerations                        | 35         |

| 10.0 Software Design Considerations                         | 40         |

| 11.0 Version 2 Changes                                      | 54         |

| 12.0 Summary and Conclusions                                | 56         |

| 13.0 References                                             | 57         |

| Appendix A: Individual Contributions                        | A-1        |

| Appendix B: Packaging                                       | <b>B-1</b> |

| Appendix C: Schematic                                       | C-1        |

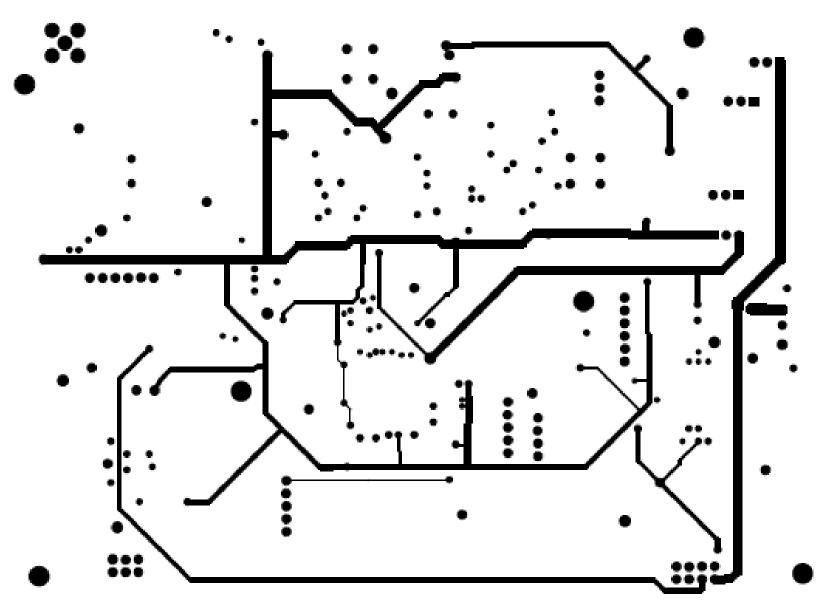

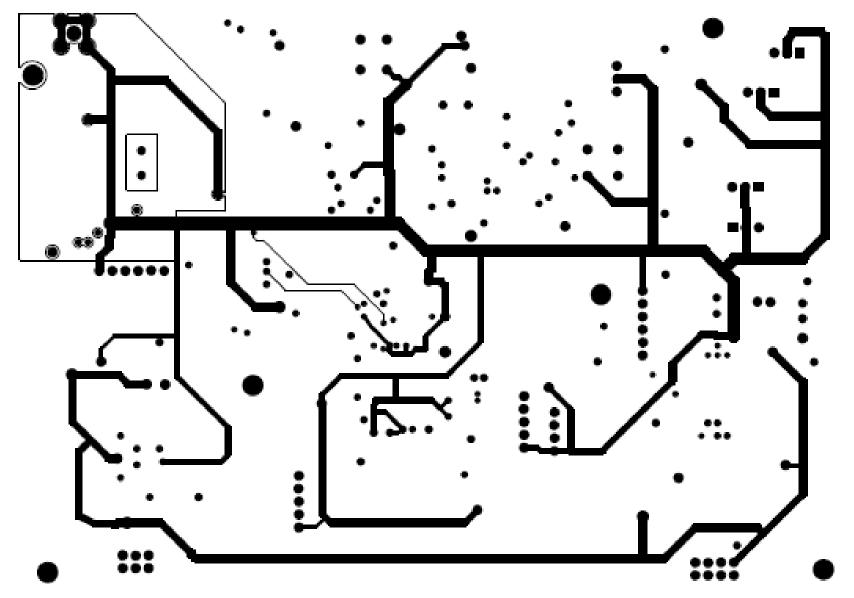

| Appendix D: PCB Layout Top and Bottom Copper                | D-1        |

| Appendix E: Parts List Spreadsheet                          | E-1        |

| Appendix F: FMECA Worksheet                                 | F-1        |

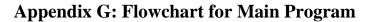

| Appendix G: Flowchart of Main Program                       | G-1        |

| Appendix H: Hierarchical Block Diagram of Code Organization | H-1        |

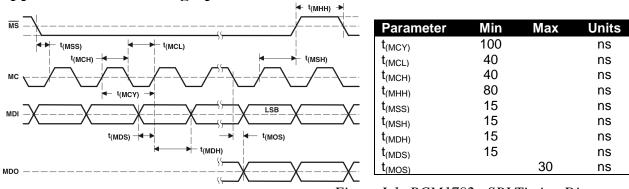

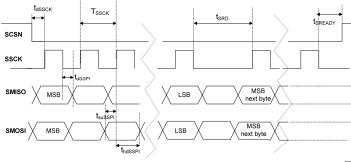

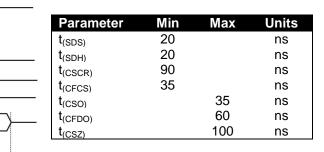

| Appendix I: SPI Timing Specifications and I2S Protocol      | I-1        |

# Abstract

Digital Sound Projection is a high quality audio transceiver for use in music or lecture hall venues and personal settings. A portable transmitter accepts a microphone or line input and transmits the audio signal wirelessly to the receiver base station. From the receiver the user can adjust audio characteristics with equalization controls or enhance vocal components with Digital Mute. An LCD interface simplifies the user controls for adjusting the different audio settings. An EQ screen allows the user to adjust the amplitudes of 11 frequency bands from 20Hz up to 24kHz. The digital mute function allows the user to enhance vocal harmonics in order to selectively amplify human voice.

# **1.0 Project Overview and Block Diagram**

# **1.1 Project Overview**

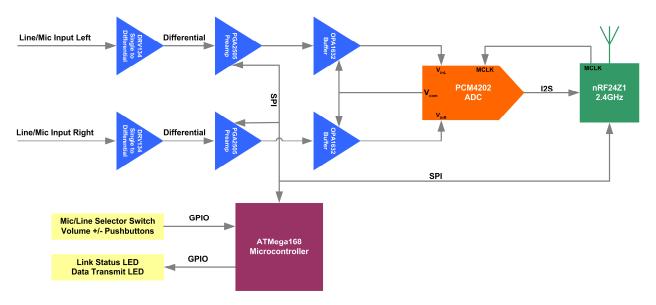

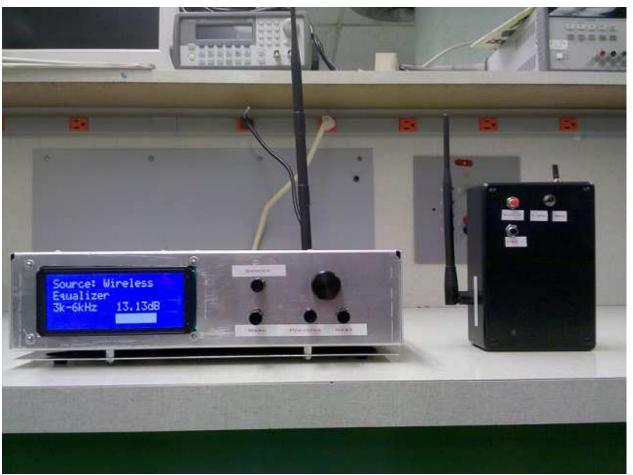

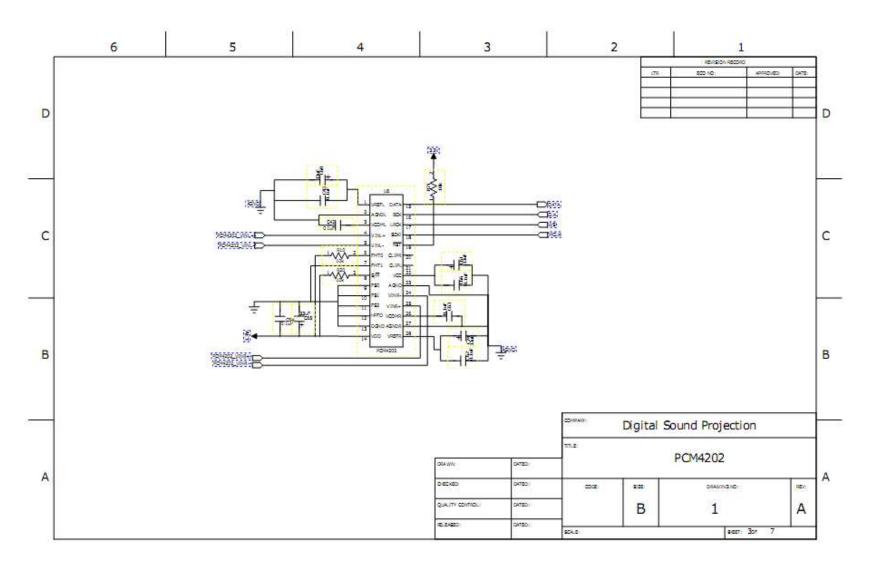

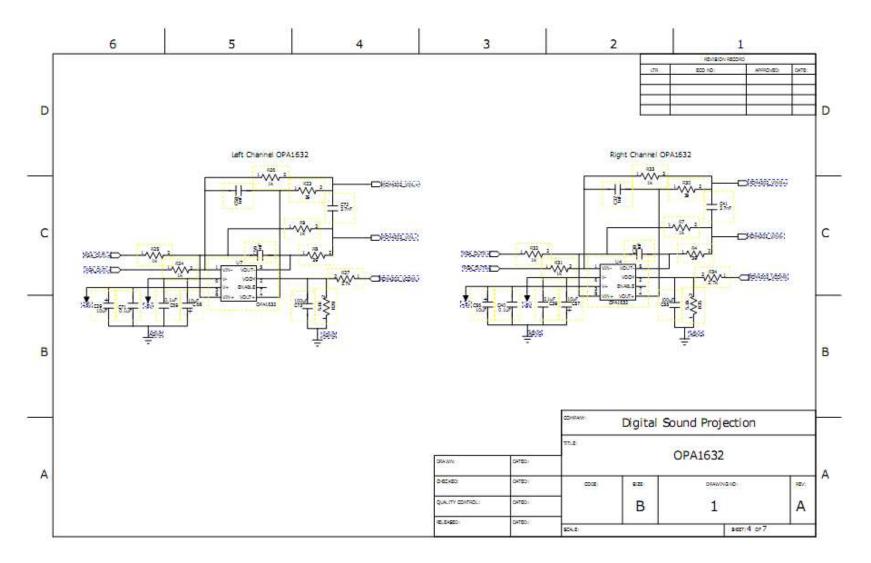

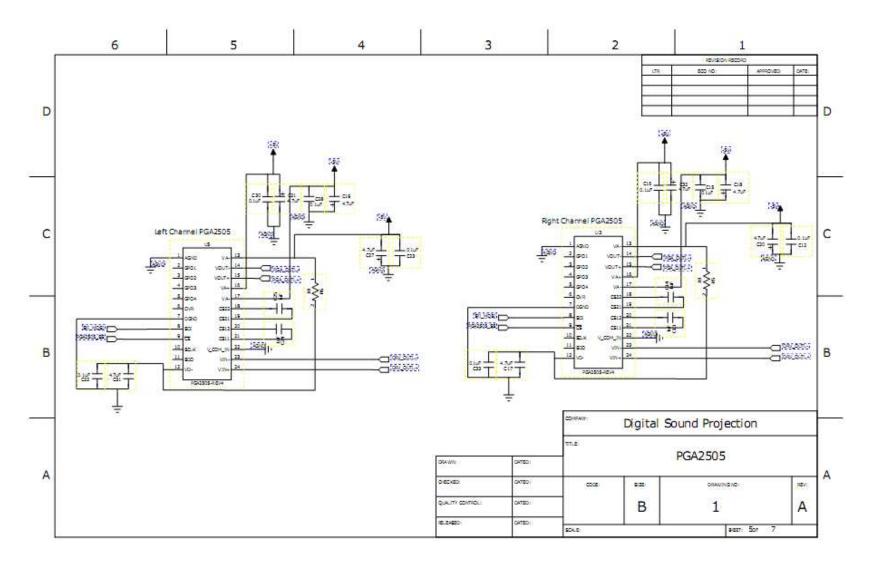

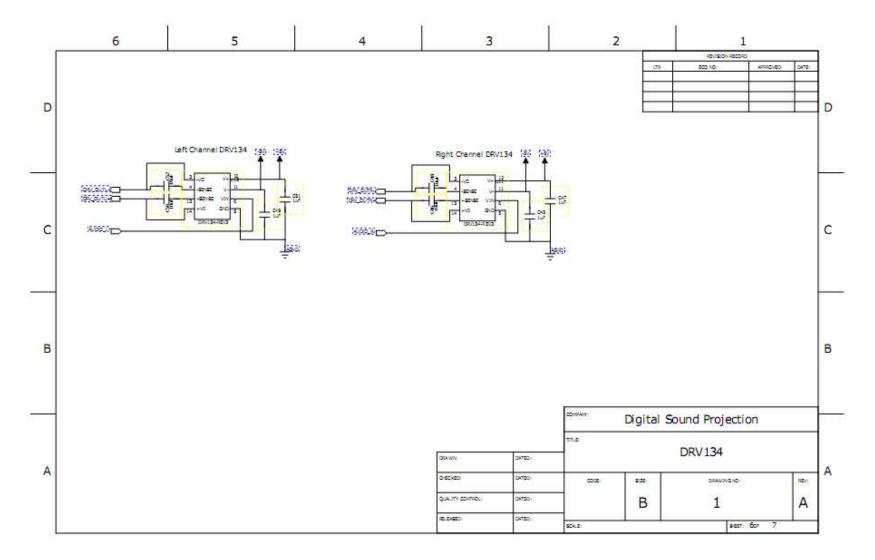

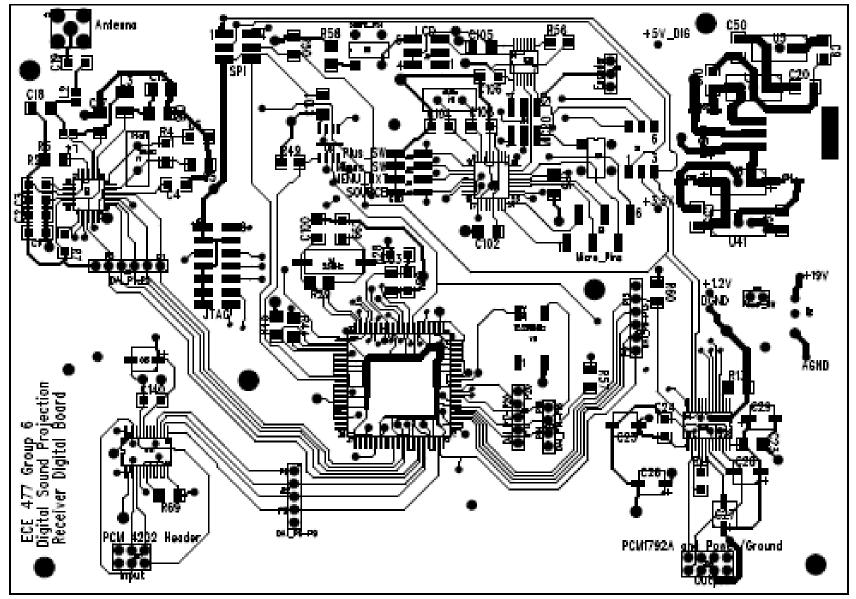

Digital Sound Projection consists of a transmitter and a receiver unit. The transmitter accepts an analog stereo line or microphone input. Each signal is converted into a differential signal through the DRV134, amplified using the PGA2505 microphone preamplifier, buffered with the OPA1611 op-amp, and finally converted into a digital signal by the PCM4202. The digital signal is then modulated by the nRF24Z1 transceiver and sent to the receiver via a 2.4GHz wireless channel.

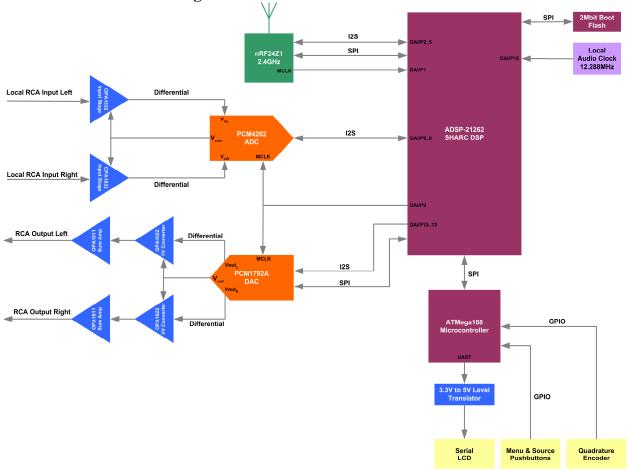

The receiver takes an input audio signal from either the transmitter or directly from an analog line-in. Equalizer effects are then applied digitally through the SHARC ADSP-21262 DSP chip. The user is capable of defining the EQ effects through an LCD user interface controlled by the ATmega168 microcontroller. The UI also enables the user to apply a voice enhancement algorithm implemented by the SHARC and select the input signal source. After signal processing, the digital audio signal is converted back to analog through the PCM1792A DAC and output to speakers.

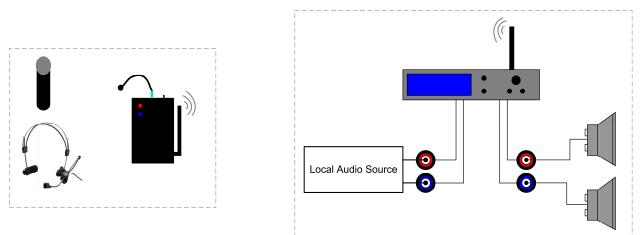

# **1.2** System Level Diagram

Figure 1-1: System Level Diagram

# 1.3 Transmitter Block Diagram

Figure 1-2: Transmitter Block Diagram

**1.4 Receiver Block Diagram**

Figure 1-3: Transmitter Block Diagram

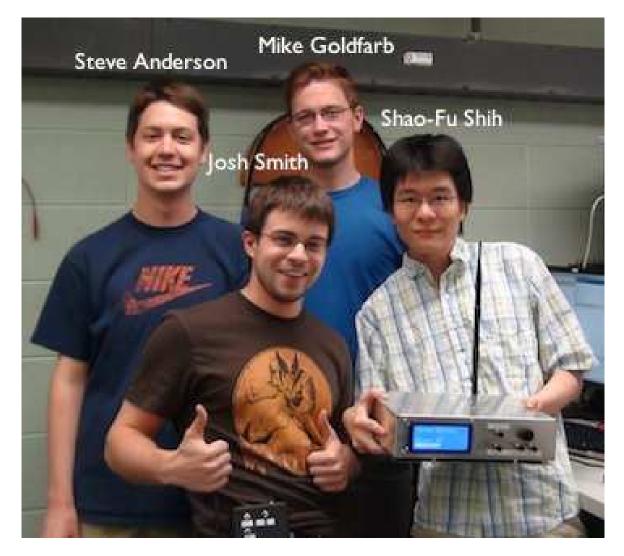

# **1.5** Photograph of Digital Sound Projection System

Figure 1-4: Digital Sound Projection

# 2.0 Team Success Criteria and Fulfillment

# 2.1 Project-Specific Success Criteria

- 1. An ability to wirelessly transmit and receive a digital audio signal.

- 2. An ability to display information to the user on an LCD about the status of the device.

- 3. An ability to apply digital mute to the audio signals based on a threshold.

- 4. An ability to allow the user to adjust EQ effects applied to audio signals.

- 5. An ability to control output volume wirelessly from the transmitter.

# 2.2 Assessment of PSSC Fulfillment

All PSSC's have been satisfied by the Digital Sound Projection design.

- 1. The unit successfully transmits a digital audio signal between the transmitter unit and receiver base.

- 2. The unit successfully displays information regarding the system to the user via an LCD interface. Separate menus are provided for the three major adjustable settings on the receiver: volume, EQ, digital mute. The rotary encoder and push buttons allow the user to manipulate settings on each screen of the user interface.

- 3. Digital mute based on a threshold is successfully implemented in Digital Sound Projection. A user can selectively boost or reduce harmonic components of human voice by setting the upper and lower frequency boundary and specifying a gain value.

- 4. The user can apply EQ effects to audio by adjusting the gain of 11 separate frequency bands.

- 5. The user can increase or decrease the output volume wirelessly from the transmitter using pushbutton controls.

# 3.0 Constraint Analysis and Component Selection

#### 3.1 Introduction

Processing digital audio in real-time is computationally expensive and requires a microprocessor that executes fast enough to maintain the necessary level of throughput without dropping audio samples or degrading audio quality. High quality analog to digital and digital to analog converters with high dynamic range and low harmonic distortion are necessary to ensure undistorted audio input and output. This section will address the constraints that must be met to produce a successful design along with the rationale for major component selection based upon the constraint analysis.

#### **3.2 Design Constraint Analysis**

In this section, the major design constraints will be addressed. As the most critical design challenges, computational, interfacing, and peripheral requirements will be emphasized. Important power, packaging, and cost constraints will also be covered.

#### **3.3** Computation Requirements

The device will require a high-performance digital signal processor to perform real-time digital audio processing. Equalizer effects and digital mute will be applied to large blocks of 2048 audio samples using the method of FFT convolution. FFT convolution takes advantage of the property that multiplication in the frequency domain is equivalent to convolution in time domain. Performing signal processing in the frequency domain is conceptually simple and provides greater software flexibility. The digital signal processor must compute the FFT, process frequency domain data, and compute the inverse FFT within the maximum amount of time required to collect the next set of audio samples. Audio will be sampled at a rate of 48kHz, limiting the maximum processing time to 42.7ms per 2048 sample block. After this amount of time passes the next sample block will have been filled, not processing this block in time would require the entire sample blocks to be skipped.

All signal processing algorithms will be carried out using 32-bit floating-point arithmetic. Floating-point representation is preferable because quantization noise is thousands of times smaller [1] when compared to fixed-point. The total amount of RAM required for storing and processing input samples, not including program space, (i.e. stack, heap, and program) is given by: M = 15 \* 32 \* N, where N is the number of sample points per block, and M is the number of bits required to perform the FFT convolution. The DSP requires at least 983,040 bits of data memory for a block size of 2048 floating point samples.

## **3.4 Interface Requirements**

General purpose I/O is split between user interface components and SPI chip selects signals for off-chip slave peripherals. The receiver's user interface contains a LCD, a rotary encoder, and several push buttons. A CFA634-TMC-KS serial character LCD requires a UART capable of a minimum 9600 baud with a TTL voltage swing of 0 to 5V [2]. A 3.3V to 5V level translator will be required to interface with the LCD data lines with microcontroller's UART pins. The EVEG rotary encoder requires two digital I/O pins for quadrature pulses. [12] Four to five push buttons will be used to select between several user interface displays and to move between on screen selections. The DSP requires four general-purpose I/O pins for SPI chip select signals used for off-chip slave peripherals.

#### **3.5 On-Chip Peripheral Requirements**

The transmitter's microcontroller is responsible for configuring the microphone pre-amp and wireless transmitter through a serial peripheral bus. A minimum of one SPI controller is required to initialize and control these components. A microcontroller also is used to control the user interface on the receiver. The user interface microcontroller requires at least one SPI peripheral to communicate with the DSP. Both the transmitter and receiver microcontrollers SPI peripherals must be capable of 1MHz clock speed and have configurable modes. Each microcontroller should also include an I2C capable interface to plan for unforeseen peripheral requirements or an additional SPI controller.

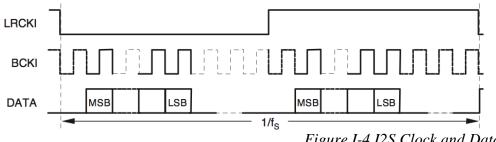

The DSP requires at most three I2S capable serial ports for interfacing with the wireless audio transceiver, an ADC, and a DAC. It may be possible to use two serial ports if the clock, frame sync and bit clock can be shared between the ADC and DAC. A dedicated serial port must be used to interface with the wireless audio transceiver due to the mismatch in data word sizes.

The DSP also requires at least one SPI controller to configure the DAC, wireless transceiver chip, and to communicate with the user interface microcontroller. The DSP SPI controller should also be capable of operating in either master or slave mode.

# 3.6 Off-Chip Peripheral Requirements

The device requires both analog to digital and digital to analog converters capable of 24-bit resolution at a sampling rate of 48kHz. The ADC and DAC must also implement the I2S serial audio interface to connect with the DSP and the wireless transceiver. To ensure the best possible audio signal quality the DAC and ADC should have a very high dynamic range and low total harmonic distortion. An external wireless transceiver is required to stream audio data from the ADC on the transmitter to the DSP on the receiver. The wireless transceiver should be capable of interfacing directly with the DSP and the ADC using I2S. Configuration of the ADC, DAC and wireless transceiver should be performed through a common peripheral bus such as SPI or I2C.

#### **3.7 Power Constraints**

The wireless transmitter should be battery powered with NiMH rechargeable batteries to enable the user to carry the device without additional wires that restrict movement. An estimated 200mA (based off datasheets) is required to power the transmitter components. On the receiver a +15V and -15V supply is required to power high quality operational amplifiers on the audio output stage.

#### 3.8 Packaging Constraints

The wireless transmitter is designed to be small and light enough to clip to a users belt or pocket. Care must be taken when considering antenna size and placement to ensure the best possible reception while not making the transmitter awkward to wear. Analog and digital components should be separated and possibly shielded on the PCB of both the receiver and transmitter to ensure minimal RF contamination of the analog audio signal.

#### **3.9** Cost Constraints

-9-

The device should be competitive with other wireless audio systems on the market while providing additional features not present in existing products. The freePORT Presentation Set, a wireless audio system with wireless microphone from Sennheiser, retails for \$375.95. [3] Another system, the Shure ULX Standard Series – Instrument System, also provides quality wireless audio transmission, for \$759.00. [4] Both of these products provide more wireless channels than our device will support, however, our device will provide additional audio capabilities without the need for additional audio processing hardware.

#### **3.10** Component Selection Rationale

Component selection is based on the constraints covered in the previous section with special consideration given to performance, ease of use, and interface flexibility. Two floating-point DSPs are compared: TMS320C6711D (TMS320) from Texas Instruments and ADSP-21262 from Analog Devices. The PCM4202 ADC and PCM1792A DAC from Texas Instruments are compared against the Analog Devices AD1936 audio codec. For wireless audio transmission, the nRF24Z1 wireless audio transceiver from Nordic Semiconductor is compared with the DARR80 digital baseband processor from STS.

The DSP that best meets the computational and interfacing constraints is the ADSP-21262 (SHARC) from Analog Devices. The SHARC is a high-performance (1200 MFLOPs), DSP supporting 32-bit floating-point and 32-bit fixed-point computation with two independent computational units. An I/O processor provides 22 separate DMA channels, a dedicated SPI port, six serial ports and configurable general-purpose I/O pins. The I/O processor includes a software programmable signal routing unit (SRU) that allows any I/O processor port to be connected to any of the 20 external processor pins. [5] The TMS320 is a 32-bit floating point, high-performance (1500 MFLOPs) DSP with 512Kbits of RAM, and eight independent computational units. The TMS320 includes 16 independent DMA channels, two multi-purpose serial ports, and five general-purpose I/O pins. The SHARC meets all computational, memory, and interfacing requirements and includes several desirable features not present in the TMS320. While comparable to the SHARC in computational speed, the TMS320 lacks the I/O flexibility provided by the SHARC's signal routing unit. The SHARC also includes a larger amount on on-chip RAM, avoiding the need to interface to slower external memory.

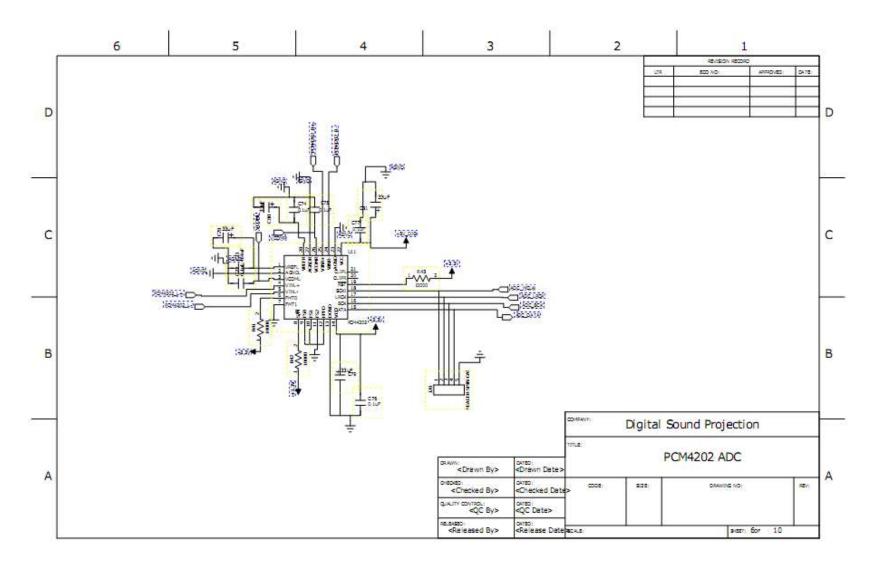

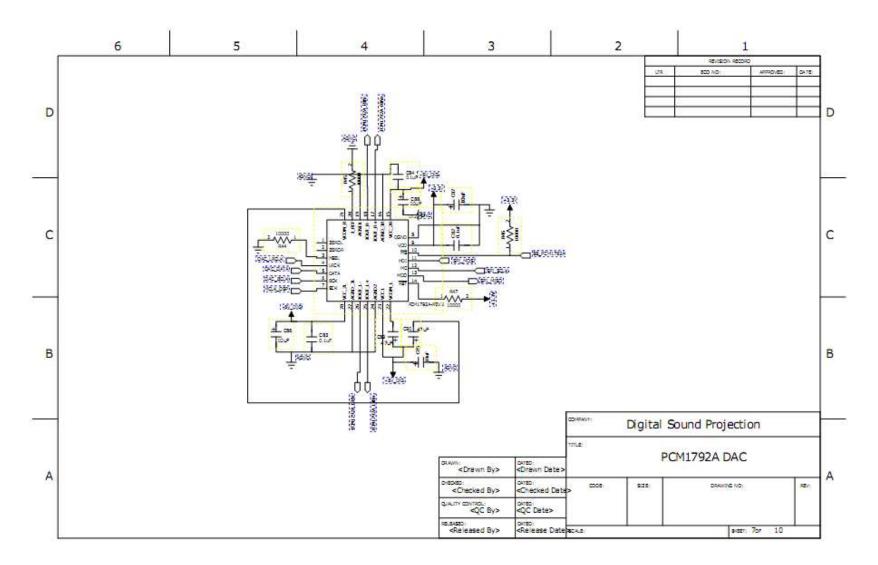

High quality ADC and DAC channels with high dynamic range and low total harmonic distortion (THD) are essential for ensuring high quality audio. The AD1936 audio codec from Analog Devices provides four ADC channels with a dynamic range of 109dB and -98dB THD. Eight DAC channels with 107dB dynamic range and -98dB THD are packaged with the DAC channels for an all-in-one chip solution. [7] While the AD1936 performs well, most of the DAC and ADC channels would be unused, especially on the transmitter where only two ADC channels are required. The PCM4202 from Texas Instruments is a two channel ADC with 118dB dynamic range and -105dB THD. [8] The PCM4202 has higher performance characteristics and fewer channels which better meets the interfacing requirements of both the receiver and transmitter. The PCM1792A two-channel DAC from Texas Instruments has a 127dB dynamic range and -108dB THD [9] also outperforms the AD1936 and better meets the interfacing requirements of the receiver.

The wireless audio transceiver must be capable of interfacing directly with the DSP and ADC peripherals using an I2S audio serial interface. A glueless digital audio interface is required to maintain the necessary throughput of high quality audio. The nRF24Z1 from Nordic Semiconductor transmits 16-bit CD quality audio on the 2.4GHz ISM radio band. Audio data is transferred into and out of the nRF24Z1 using an I2S audio interface. [10] The DARR80 from STS implements all of the features found in the nRFZ241 but includes support for up to eight audio channels. Unlike the nRF24Z1, the DARR80 requires an external 802.11 frontend radio and only supports I2C bus for configuration and initialization. [11] The nRF24Z1 was selected due to the availability of documentation, smaller pin count, an on-chip radio interface, and its inclusion of an SPI port for configuration.

# 3.11 Summary

In this section, several major components were selected based on key design constraints. The ADSP-21262 digital signal processor was chosen for its 2Mbit and I/O flexibility. Separate high-performance DACs and ADCs from Texas Instruments were selected over a single integrated audio codec because of their superior performance characteristics and lower channel count. Lastly, the nRF24Z1 wireless audio transceiver provides the necessary audio interfacing and RF stack in a single-chip package.

# 4.0 Patent Liability Analysis

#### 4.1 Introduction

Digital Sound Projection (DSP) is a wireless audio system for a microphone or direct line input. The user then is able to modify the audio signal on the receiver by adjusting the Equalization (EQ) effects shown on an LCD screen. After these effects have been applied by a digital signal processor, the signal is then sent to speakers through a 2 channel stereo output. Two of the main functions for DSP are the wireless transmission of the input microphone signal from the transmitter to the receiver and the ability for the user to apply EQ effects on the received signal to their preference. DSP's design, specifically the two prior functions listed, must be designed in a manner as to not infringe on any prior patents or product designs.

## 4.2 Results of Patent and Product Search

The patent database was searched in order to analyze the patent liability associated with Digital Sound Projection's major functions. In addition to the patent search, products that perform similar functions were investigated in order to determine if any ideas or designs were infringed upon in DSP's design. Some of the major functions that DSP performs that are of concern involve the implementation of the wireless system and the signal processing done on the input signal in order to improve quality.

The first patent that was investigated for the design of a wireless audio system is Patent 7,680,465. [1] This patent was filed on July 31, 2006, and involves a wireless audio device and improving the sound quality based on user-specific audio parameters. This audio device receives its input from a wireless source, and then allows the user to adjust the gain of individual frequency bands and does this processing using a digital signal processor. It then outputs the audio signal directly to speakers or transmits it wirelessly to another device. The patent covers basically any wireless scheme and allows for an operating frequency range of any MHz or GHz as shown in the detailed description section of the patent.

Another product that shared similar functionality as the DSP is the Shure line of wireless microphone systems. [2] An example device shows that Shure has designed a body pack that receives a microphone input and outputs at a specific frequency to a tuned receiver that outputs to some speakers or another audio device. This devices' wireless operation frequency is around

700 MHz and is tuned/selected based on the user's input from the base receiver and transmitter. The transmitters have automatic frequency selection and offer the choice of using a microphone input or a direct line input.

Technical-pro also has a product that performs a similar function as Digital Sound Projection. [3] The RX-B32 is a home audio receiver that has the capability of accepting 3 RCA inputs and 2 microphone inputs. The receiver also has built-in antennas that receive AM and FM radio. This receiver has the ability to choose whether to use the microphone input or the RCA inputs and allows the user to input some parameters in order to improve the quality of the input signal to their preference. The output is then sent to 2 main speakers or through surround sound if selected by the user.

#### 4.3 Analysis of Patent Liability

Digital Sound Projection has many similarities with other products and existing patents. [1] For example, Patent 7,680,465 and Digital Sound Projection both accept an audio signal from an RF source and allow for the user to input different audio parameters into the system to generate a user-specific audio signal. For both products this involves determining the coefficients for different frequency bands and using these coefficients to adjust the signal in a digital signal processor. Both systems then output this new audio signal to speakers. Also, each device uses a controller to manage the user input along with the rest of the system on the receiver. The patent uses a description of a general "controller" managing the devices in the system, but DSP specifically uses the ATmega168 microcontroller to manage the user input and ICs on the transmitter and receiver. Digital Signal Projection is similar enough to the patent's design that it could potentially infringe under the doctrine of equivalents. DSP performs the same overall functions, but it would depend on how the software is structured in the design within the patent. The patent does not list how it performs the user specific input on the audio source using the processor. However, DSP analyzes the incoming audio signal by taking the FFT and then uses the amplitude coefficients for the frequency bands to perform the Equalization effects on the audio signal. Another difference may apply with the circuitry involved in outputting the signal from the digital signal processor to the speakers. Again the patent does not explain how it is done, but for DSP the data output from the processor passes through a digital to analog converter and then through a IV-conversion stage to produce a 2-channel stereo output.

The designs in Patent 7,680,465 and that of DSP also receive the inputs to their systems from a wireless RF source. [1] The patent is designed to accept an audio input from any wireless link; specifically it will be able to operate in the 2.4 GHz frequency range. DSP, on the other hand, only is designed to receive its input from the matching wireless transmitter. This RF signal also is transmitted in the 2.4 GHz range, but the nRF24Z1 uses a frequency shifting algorithm in order to find an unused frequency for transmission in the 2.4-2.45 GHz range, and the patent does not describe the wireless modulation scheme that is implemented in their design. The wireless transceiver used in DSP is designed specifically for transmitting/receiving high fidelity audio signals where the patent does not make this distinction.

The Shure wireless microphone systems are other products that perform the same general function as Digital Sound Projection. For both systems, a user connects either a microphone or a direct audio line into the transmitter, and then the signal transmits wirelessly to the base receiver. The major differences in operation occur in the receiver. [2] The Shure systems receive the signal from the transmitter and then output the signal to the speakers, whereas DSP allows the user to modify the signal before outputting to the speakers. For Shure's design, the only major UI on the receiver involves selecting the frequency of operation for the wireless transmission. There are enough differences in the receiver portion of the designs after the signal is received that there is no possibility that DSP infringes on Shure's designs. The potential for infringement comes from the transmitter and the wireless transmission. The Shure system transmits at around 700 MHz whereas DSP transmits at 2.4 GHz. Again, DSP's wireless transmitting a signal through RF is non-trivial enough that DSP's design would not be infringing on Shure's wireless designs. There is also no specific software being written in DSP's transmission that would potentially infringe on Shure's designs.

Technical-Pro's RX-B32 audio receiver is another product that performs the same overall function as the Digital Sound Projection. [3] Both receivers can accept either a microphone input or a stereo (RCA) input. Each product then allows the user to change the settings of the audio signal given some parameters and then outputs the signal to speakers. However, the purpose of the UI is different for both devices. The RX-B32 has a limited interface of only being able to adjust bass, treble, echo, and volume; whereas the DSP design allows for adjustments of the amplitude for different frequency bands and allows for an overall volume modification and

mute, with these adjustments output on an LCD screen. The RX-B32 also allows for AM/FM radio from the antenna input. DSP allows for a wireless input as well, but it is from the matching transmitter of the receiver that accepts a microphone or line input. Even though these two products achieve the same general function of improving an audio signal based on a user's input, there are enough differences so that DSP does not infringe on the RX-B32's design.

# 4.4 Action Recommended

Even though Patent 7,680,465 covers many of the same functions and ideas in Digital Sound Projection's design, the specific claims of the patent are obvious enough for DSP to not infringe on the patent's design. The patent does not explain how any of the claims are implemented or even give any idea of what kind of algorithm or software is used. Because of the generality of the claims, DSP would not have any significant potential for infringing under the doctrine of equivalents. However, if a lawyer interpreted that the design of DSP was actually infringing on this patent, then DSP would most likely have to pay a licensing fee in order to produce the wireless system.

Shure's wireless microphone systems were also a potential for infringement; however, the receivers of the Shure's systems and DSP are significantly different and the audio signal passes through more user influence in DSP before outputting to the speakers. The potential of infringement would occur with the transmitters. However, since the transmitter's hardware can be considered "obvious", there are enough differences in the wireless scheme that no actions need to be taken with DSP's design in order to avoid infringing on Shure's wireless systems. DSP's design was also very similar to Technical-Pro's RX-B32 receiver involving the user interface to adjust the audio signal to the user's specifications before being output to speakers. However, the kind of functions that DSP uses are significantly different than the RX-B32 and the source of the wireless input is also notably different. With these differences in design, DSP does not have the potential for infringing upon the design of the RX-B32 and no action needs to be taken to change the design of DSP.

# 4.5 Summary

Two products and one patent were analyzed in order to determine the possibility of infringement if Digital Sound Projection were to be produced and sold. Patent 7,680,465 described a wireless system that receives an audio signal and allows the user to adjust the amplitude of different frequency bands. One company's products, the Shure wireless microphone systems, are products that perform the same function of transmitting a microphone input to a base receiver and outputting the signal to speakers. However, the Shure wireless systems do not allow the user to adjust the audio signal to the user's preferences before outputting to the speakers. The Technical-Pro RX-B32 receiver is another product that does the same function as DSP's receiver unit by accepting an audio signal and allowing the user to change some settings to their preference and outputs the adjusted signal. These products and the patent all share some similarities with the design of Digital Sound Projection, although the main similarities are considered "obvious" designs and do not risk any infringement of ideas. DSP also applies enough differences in execution of the design that the potential for infringement, both literal and under the doctrine of equivalents, does not exist and no other actions need to be taken.

# 5.0 Reliability and Safety Analysis

#### 5.1 Introduction

In the case of device failure, because the transmitter board contains only one microcontroller and three other digital components, it is unlikely a safety critical event will arise. The receiver consists of a set of digital and analog boards. In the case of device failure on the analog board, one of the critical safety issues is if the two 1mF power supply filter capacitors malfunction. A critical safety issue on the receiver station can be a failure of the 5V/4A switching power supply module. A malfunction will damage all the digital components on the digital board. To prevent the user from being harmed when critical failure occurs, the receiver is packaged with an aluminum casing. Other non-critical failures such as digital components malfunctioning or analog components decaying over time will only create inconvenience without resulting physical harm to the user.

# 5.2 Reliability Analysis

The failure rate of Digital Sound Projection is most likely to be determined by the digital signal processor, SHARC ADSP-21262, since it has the most die complexity and current load. The SHARC DSP performs 32-bit computations on the digital audio signal and routes the input and output signals for DAC and ADC. The SHARC draws around 800mA of current under full load which is relatively high in comparison to all other components on the board. The next set of digital components expected to fail after the ADSP-21262 are the PCM4202, the PCM1792A, and the ATmega168. The PCM4202 is chosen because it continuously converts the analog input signal to an I2S output signal with 24-bit precision. This operation involves a series of logic gate switching and draws approximately 20mA from Vdd and 65mA from Vcc. The PCM1792A is chosen because it continuously converts the I2S input signal from the SHARC into differential current outputs. This operation involves an internal voltage to current converter in addition to the 24-bit digital to analog conversion and draws approximately 10mA from Vdd and 65mA from Vcc. The ATmega168 is expected to fail because it holds the input values for various audio effects that are constantly scanned by the SHARC and is responsible for generating the user interface on the LCD display module when the device is turned on.

The Military Handbook for Reliability Prediction of Electronic Equipment predict the expected amount of device failures in 10<sup>6</sup> hours can be calculated as  $\lambda_P = (C1^*\pi_T + C2^*\pi_E)^*\pi_Q^*\pi_L$  for microcircuits, gate/logic arrays, and digital processors where C1 is the die complexity,  $\pi_T$  is the temperature coefficient, C2 is the packaging failure rate,  $\pi_E$  is the environment factor,  $\pi_Q$  is the fabrication quality factor, and  $\pi_L$  is the manufacture learning factor.

| Parameter name     | Description               | Value              | Comments                                        |  |

|--------------------|---------------------------|--------------------|-------------------------------------------------|--|

|                    |                           |                    |                                                 |  |

| C1                 | Die complexity            | 0.560              | 32-bit MOS micro                                |  |

| $\pi_{\mathrm{T}}$ | Temperature coeff.        | 0.630              | $T_j = T_C + (\theta_{JC} * P) = 69.90^\circ C$ |  |

|                    |                           |                    | $T_c = 30$ $\theta_{JC} = 27.9$ P = 1.27        |  |

| C2                 | Package Failure Rate      | 0.060              | $N_p = 144$ Hermetic SMT                        |  |

| $\pi_{ m E}$       | <b>Environment Factor</b> | 2.0                | Ground Fixed                                    |  |

| $\pi_{ m Q}$       | Quality Factors           | 1.0                | Commercial Product                              |  |

| $\pi_{ m L}$       | Learning Factor           | 1.0                | In production for more than                     |  |

|                    |                           |                    | 2 years                                         |  |

| Entire Design      |                           | $\lambda_P = .484$ | MTTF $\cong$ 235.9 years                        |  |

Table 5-1: ADSP-21262 MTTF Calculation Chart

| Parameter name     | Description               | Value               | Comments                                         |

|--------------------|---------------------------|---------------------|--------------------------------------------------|

|                    |                           |                     |                                                  |

| C1                 | Die complexity            | 0.140               | 8-bit MOS micro                                  |

| $\pi_{\mathrm{T}}$ | Temperature coeff.        | 0.140               | $T_j = T_C + (\theta_{JC} * P) = 32.5^{\circ} C$ |

|                    |                           |                     | $T_c = 30  \theta_{JC} = 25 P = .10$             |

| C2                 | Package Failure Rate      | 0.012               | $N_p = 32$ Hermetic SMT                          |

| $\pi_{\rm E}$      | <b>Environment Factor</b> | 2.0                 | Ground Fixed                                     |

| $\pi_Q$            | Quality Factors           | 1.0                 | Commercial Product                               |

| $\pi_{\rm L}$      | Learning Factor           | 1.0                 | In production for more than                      |

|                    |                           |                     | 2 years                                          |

| Entire Design      |                           | $\lambda_P = .0374$ | MTTF $\cong$ 4397 years                          |

| Parameter name       | Description               | Value               | Comments                                         |

|----------------------|---------------------------|---------------------|--------------------------------------------------|

|                      |                           |                     |                                                  |

| C1                   | Die complexity            | 0.160               | 10001-30000 gates                                |

| $\pi_{\mathrm{T}}$   | Temperature coeff.        | 0.431               | $T_j = T_C + (\theta_{JC} * P) = 60.8^{\circ} C$ |

|                      |                           |                     | $T_c = 30  \theta_{JC} = 100 P = .308$           |

| C2                   | Package Failure Rate      | 0.013               | $N_p = 28$ Non-hermetic SMT                      |

| $\pi_{ m E}$         | <b>Environment Factor</b> | 2.0                 | Ground Fixed                                     |

| $\pi_{ m Q}$         | Quality Factors           | 1.0                 | Commercial Product                               |

| $\pi_{ m L}$         | Learning Factor           | 1.0                 | In production for more than                      |

|                      |                           |                     | 2 years                                          |

| <b>Entire Design</b> |                           | $\lambda_P = .0950$ | MTTF $\cong$ 1202 years                          |

| Table 5-3.        | PCM4202  | MTTF   | Calculation | Chart |

|-------------------|----------|--------|-------------|-------|

| <i>Tuble 3-5.</i> | 1 CM4202 | IVIIII | Culculation | Churi |

| Parameter name     | Description          | Value               | Comments                                              |  |

|--------------------|----------------------|---------------------|-------------------------------------------------------|--|

|                    |                      |                     |                                                       |  |

| C1                 | Die complexity       | 0.080               | 3001 – 10000 Gates                                    |  |

| $\pi_{\mathrm{T}}$ | Temperature coeff.   | 0.293               | $T_{j} = T_{C} + (\theta_{JC} * P) = 50.50^{\circ} C$ |  |

|                    |                      |                     | $T_c = 30  \theta_{JC} = 100 \text{ P} = .205$        |  |

| C2                 | Package Failure Rate | 0.013               | $N_p = 28$ Non-hermetic SMT                           |  |

| $\pi_{\rm E}$      | Environment Factor   | 2.0                 | Ground Fixed                                          |  |

| $\pi_{Q}$          | Quality Factors      | 10                  | Commercial Product                                    |  |

| $\pi_{L}$          | Learning Factor      | 1.0                 | In production for more than                           |  |

|                    |                      |                     | 2 years                                               |  |

| Entire Design      |                      | $\lambda_P = .0494$ | MTTF $\cong$ 2309 years                               |  |

| Table 5-4: | <i>PCM1792A</i> | MTTF | Calculation | Chart |

|------------|-----------------|------|-------------|-------|

|------------|-----------------|------|-------------|-------|

In summary, the Digital Sound Projection has a relatively low failure rate and all of the digital components have  $\lambda_P < 1$ . One critical factor of the failure rate is the thermal dissipation of surface mount ICs. To further improve the MTTF rate, additional heatsinks can be attached to reduce the thermal junction coefficient. Applying extra cooling fans to reduce the ambient casing temperature is also a possible solution to extend the MTTF.

# 5.3 Failure Mode, Effects, and Criticality Analysis

The Digital Sound Projection consists of one transmitter unit and one receiver unit. The following two subsections will discuss each individual subsystem for both the transmitter and the receiver. In Appendix F of the report, there is a FMECA table that includes the criticality of each failure for each subsystem for both the transmitter and the receiver.

The criticality levels are stated as High, Medium, and Low. A High criticality failure is a failure that could physically harm the user. For this kind of failure, the failure rate  $\lambda_P$  must be below 10<sup>-9</sup> failures/hour. A Medium criticality failure is a failure that can cause the Digital Sound Projection unit to malfunction. These failures are less dangerous to users but the failure rate should be lower than 10<sup>-6</sup> failures/10<sup>6</sup> hours. A Low criticality failure is a failure that affects the Digital Sound Projection's overall performance. These failures should not stop the functionality of the Digital Sound Projection but should be limited to 10<sup>-5</sup> failures/10<sup>6</sup> hours.

# 5.4 FMECA on the Transmitter Board

The transmitter board can be divided into five individual functional subsystems. These blocks include NiMH battery packs connected with linear voltage regulators, analog inputs, the PCM4202 ADC, the nRF24Z1 wireless transmitter with antenna, and the ATmega168 microcontroller with device status indicators.

# 5.5 FMECA on the Receiver Board

The Receiver board can be divided into six individual functional subsystems. These blocks include digital/analog power supply modules with noise filters, analog inputs and outputs, the PCM4202 ADC and the PCM1792A DAC, the nRF24Z1 wireless receiver with antenna, the ATmega168 microcontroller with LCD display module, and the SHARC DSP with JTAG interface.

#### 5.6 Summary

Digital Sound Projection is a relatively safe and reliable product based on the failure rate calculations. In the event of critical failures, the aluminum casing would provide protection from physical harm; however, there is no failure protection in the circuitry. Therefore, if any of the digital components are damaged, the Digital Sound Projection will most likely stop functioning. In addition, heatsinks and current limiters could be implemented to improve the MTTF rate.

# 6.0 Ethical and Environmental Impact Analysis

# 6.1 Introduction

Ethical and environmental issues with respect to the transmitter include frequency sniffing, proper battery and circuit board disposal, and user warning labels. Finally, the receiver takes the digital signal from the transmitter and performs user defined equalizer effects through the use of the SHARC digital signal processor. Ethical and environmental concerns include shock hazard user warnings, harmful materials disposal, and noise pollution.

# 6.2 Ethical Impact Analysis

# 6.2.1 Transmitter Analysis

The ethical challenges facing the transmitter design include operating conditions, user warnings, and possibly adding safety mechanisms. First, the transmitter design must be tested in a suite of different operating conditions. As DSP is meant to be used in lectures, speeches, and/or concert settings, there is the possibility of outdoor use. To ensure the DSP functions as marketed, the system will be tested for both indoor and outdoor operating conditions. Testing will include the standard "shake and bake" consisting of extreme temperature change and vibration testing. Products akin to the Thermotron Accelerated Stress Test (AST) Chamber will be used for this process [1]. Also, Radio Frequency (RF) and Electromagnetic Compatibility (EMC) Testing will be completed to ensure no FCC regulations are broken and background noise, especially in the outdoor application, does not negatively affect the system. Lastly, spill testing will be performed on the transmitter to ensure working condition in the case of a rain storm in an outdoor setting.

Secondly, while nickel metal hydride (NiMH) is not technically dangerous, it is a skin irritant and can be dangerous if ingested or comes into contact with the eye [2]. As NiMH rechargeable batteries are used in the transmitter, a warning label will be located inside the package to warn the user of dangers associated with the battery packs. The warning label will be placed next to the battery connections giving the user an easily visible caution not to use the batteries in any configuration that may cause a rupture. No other warning labels are necessary for the transmitter as there are no shock hazards or high temperatures associated with the transmitter circuit board. Lastly, there is a possible ethical issue of frequency sniffing and subsequent remote recording of the audio signals transmitted by DSP. These illegal recordings could lead to pirated live music tracks; however, this occurrence is very unlikely. The Nordic nRF24Z1 Transceiver used in the DSP design utilizes frequency hopping in the range of 2.4 to 2.45GHz [3] making it exceedingly difficult to successfully lock onto and demodulate the transmitted signal.

#### 6.2.2 Receiver Analysis

Like the transmitter, the receiver unit will be placed through a suite of tests. The receiver circuit boards will be placed through temperature change and vibration testing [1] identical to the transmitter circuit board. The receiver will also be tested for RF, EMC, and spill tested in case the receiver station is exposed to rain.

Next, the receiver requires two warning labels to be placed on the rear face of the unit. The first label will be a generic electric shock warning to caution the user from tampering with the wall socket and power input to the receiver base. Also, a warning label cautioning against operating the receiver with the cover off will be placed on the rear face of the unit. Chance of shock hazards and potential hearing loss caused by capacitor explosions are drastically reduced with a closed package; therefore, it is important to caution the user from operating the unit with no cover.

In the user documentation, volume control warnings will be placed to caution the user from operating the system at an extremely high volume. This will help prevent hearing loss to the user or any passerby in close proximity to the speakers connected to DSP. Also, all warnings provided on the receiver unit itself will be reiterated in the user documentation.

Lastly, there are a few safety mechanisms that could be added to the receiver station. A surge protector in the form of a circuit breaker could be added to the receiver power input to protect the circuit board and capacitors. This would prevent any chance, with the exception of a short circuit, of electrical shock or capacitor explosions that could potentially harm the user if operated with an open case. With regards to the receiver packaging, the prototype will be placed in a simple aluminum sheet metal box. To decrease the chance of the unit falling off a shelf and onto the user, the package could be changed to a securable rack mount.

# 6.3 Environmental Impact Analysis

# 6.3.1 Transmitter Analysis

First, while NiMH rechargeable batteries do not pose a serious environmental problem, recycling is the best course of action. Documentation in the user manual will urge the user to properly dispose of the battery packs and point them to the United States Environmental Protection Agency (EPA) battery informational page [4] which contains resources for proper battery disposal. Also, the current circuit board design contains lead. To reduce the chance of environmental lead contamination, the circuit board must be disposed of properly upon design obsolescence or circuit board failure. The EPA provides guidelines on proper disposal and recycling locations for consumer electronics [5]. The EPA also suggests using the Earth911 website to conveniently search for recycling centers for both batteries and consumer electronics on a zip code basis [6]. Both the EPA and Earth911 websites will be cited in user documentation to ensure proper disposal of both the rechargeable NiMH batteries and transmitter circuit board.

Secondly, the manufacturing process could be improved to reduce the environmental impact of DSP. A printed circuit board (PCB) manufacturer with Restriction of the Use of Certain Hazardous Substances (RoHS) compliance [7] would be chosen to ensure no lead or other environmentally harmful materials are present in the circuit board. Advanced Circuits, the PCB manufacturer used for DSP, is one such manufacturer capable of producing a RoHS compliant circuit board [8]. Although a majority of components on the circuit board are currently RoHS compliant, RoHS compliant equivalent parts would be chosen to replace the current components containing lead. Lead-free solder will also be used to ensure a RoHS compliant design. Lastly, copper pours could be added to the transmitter circuit board design to reduce the amount of copper wasted in the etching process. This, in turn, will reduce the amount of etchant waste that must be disposed of.

#### 6.3.2 Receiver Analysis

Like the transmitter circuit board, both receiver PCB's contain lead. Components containing lead must also be replaced by RoHS compliant parts to reduce any possible contamination to the environment. In addition to the circuit boards, a liquid crystal display (LCD) is used to display the equalizer effects user interface. LCD's are known to contain environmentally harmful

materials; however, a RoHS compliant LCD from CystalFontz was chosen for the DSP design reducing the environmental impact of the design. The user documentation will, however, still urge the user to recycle the LCD with the receiver unit. The same informational resources as mentioned for the transmitter PCB and batteries in Section 3.1 will be utilized in the user documentation.

Power consumption is also an environmental concern with the receiver unit as it uses significantly more power than the transmitter. The receiver requires several different voltage levels:  $\pm 15V$ , 5V, 3.3V, and 1.2V. A power supply providing 19V was chosen to achieve each required voltage level. The lower level voltages are supplied through linear regulators for the  $\pm 15V$  and a power module supplying 5V to the remaining linear regulators. While there is inherent wasted power, the power module, whom draws the most current, is 83% efficient.

Lastly, there is the environmental problem of noise pollution. In the outdoor setting, noise pollution may be a viable issue if DSP is used to play music or lectures at extremely high volume levels. Again, this could not only damage the user's hearing, but also passerby's hearing in the process. This could also lead to public nuisance reports requiring police intervention. Documentation will be added to ensure the user is aware of this environmental issue and warns against playing audio signals at extreme levels. The extreme solution would be to digitally limit the volume levels output by the receiver unit; however, the signal output by DSP could then be amplified by the user making this solution ineffective. The best course of action is to document the potential for noise pollution to ensure the user is aware of this issue.

#### 6.4 Summary

All in all, the DSP design has possible ethical and environmental issues. Ethical issues associated with the design including frequency sniffing, safety issues, and design functionality will be addressed through frequency hopping, user warnings and cautions, and a suite of testing, respectively. Noise pollution and proper battery and electronics disposal are potential environmental issues of the design; however, user documentation warning against operating at high volume levels and providing information resources for environmentally friendly disposal will reduce the environmental impact of the design.

# 7.0 Packaging Design Considerations

## 7.1 Introduction

The transmitter packaging constraints include size, ergonomic shape, and interfacing capabilities. The package must be small and light enough to clip onto the user's belt or fit in a pocket. The transmitter must be ergonomically designed as not to create discomfort for the user. Openings in the package will be required for a microphone connector, user interface (UI), and antenna.

At the receiving end, interfacing capabilities, UI considerations, and electromagnetic interference (EMI) shielding are all potential packaging issues. The receiver base must have openings for an antenna, external power source, audio output, and analog input connectors. Package openings will also be required for the UI's LCD, rotary encoder, and push buttons to display and change EQ levels and other pertinent information. EMI shielding is also a packaging constraint as to minimize exterior noise influx and radiation within the circuit.

# 7.2 Commercial Product Packaging

Although there were no package designs exactly like DSP's, several professional wireless audio systems exist with similar packages. This analysis will focus on two professional wireless audio systems, the Shure ULX Wireless System [1] and the Sennheiser freePORT Presentation Set [2], and how they are both similar and different to DSP's packaging scheme.

# 7.2.1 Shure ULX Wireless System

Figure 7-1: Shure ULX Wireless System Packaging [1]

The Shure ULX Wireless System comes in a package consisting of two separate devices. A transmitter, either the ULX1 Body-Pack Transmitter or ULX2 Hand-Held Microphone Transmitter, complimented by the ULXS4 Standard Diversity Receiver comprises the system packaging. Please note the transmitter packaging analysis will focus on the ULX1 as it closely fits the design for the DSP transmitter.

First, the transmitter package of the ULX1 is compromised of a plastic injection mold with seamless openings for antenna, audio input connector, and user interface components. A metal clip is provided on the reverse side for placement on a user's belt [1]. The package is compact and ergonomically shaped for comfort when worn by the user. All connectors and LED indicators are conveniently located on top of the unit [1]. A display and push buttons located on the ULX1's face enable the user to easily switch frequency bands [1]. Overall, the packaging design is excellent providing both user comfort and easy access to all functions. The packaging design of the DSP transmitter will be similar to that of the ULX1. The package will be small, light weight, include a metal clip, and provide easy access to connectors and buttons. Unlike the ULX1, however, the DSP package requires no considerations for a UI display.

Next, the receiving ULXS4 station package consists of a sheet metal box providing space for the UI and antennas. The package is compact and provides the user with an ability to turn the power on or off, adjust the frequency band, and volume level [1]. Connector jacks and antennas are conveniently located in the rear of the unit [1]. Like the ULXS4, the receiver's LCD UI will be placed on the front of the unit; however, as DSP's UI is more robust, more real estate is required necessitating a larger package. Also, similar to the ULXS4, the DSP receiver's connector jacks and antennas will be located at the rear face as to avoid physically interfering with the UI.

# 7.2.2 Sennheiser freePORT Presentation Set

Figure 7-2: Sennheiser freePORT Presentation Set Packaging [2]

The Sennheiser freePORT Presentation Set has a similar packaging scheme to that of DSP's. The package includes a compact transmitter unit and a sleek receiver box. First, the transmitter box is small, light weight at three ounces without batteries [2], and has a simple power button. Located on the front face is a power button and simple sliding plastic piece to protect the battery bay [2]. The top face includes the antenna and microphone input connector [2]. The Sennheiser transmitter package is a very close fit to DSP's. The design fits the size and ergonomic constraints of the DSP packaging. The only planned difference for the DSP design will be the volume control interface.

Secondly, the Sennheiser receiver package is a sleek, metal enclosure. The front face includes two antennas, LED's indicating system status, and a dial to switch frequency bands. Power and audio connectors are located in the rear of the unit [2]. The antenna located in the front of the unit do not pose any issues for the Sennheiser design [2]; however, in DSP's case, the antenna must be located in the rear of the unit as the antenna would physically impede the user from interacting with the LCD and push button interface located on top of the unit.

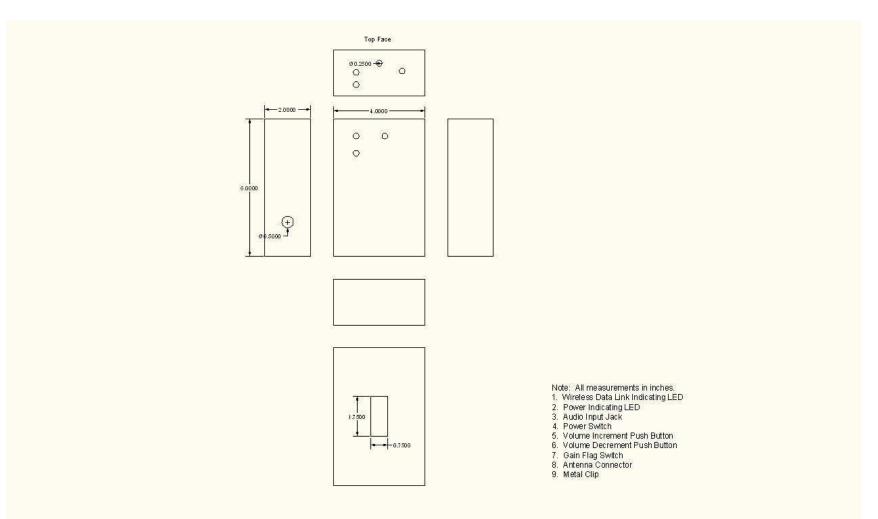

# 7.3 Project Packaging Specifications

The packaging will consist of a separate transmitter and receiver base. The transmitter package will be small, light weight, and ergonomically shaped as the user will wear the transmitter on his/her belt. A RadioShack ABS, plastic injection molded,  $6 \ge 4 \ge 2$  inch project enclosure will be used to encase the design [3]. To minimize packaging envelope size, the antenna will be located on the left side of the transmitter. Power and wireless data link LED indicators, microphone input connector, and power switch will be placed on top of the unit for

easy viewing and access, respectively. Volume control push buttons and gain flag switch will be located on the front face to allow the user to adjust volume or adjust the gain of the transmitter while wearing the device.

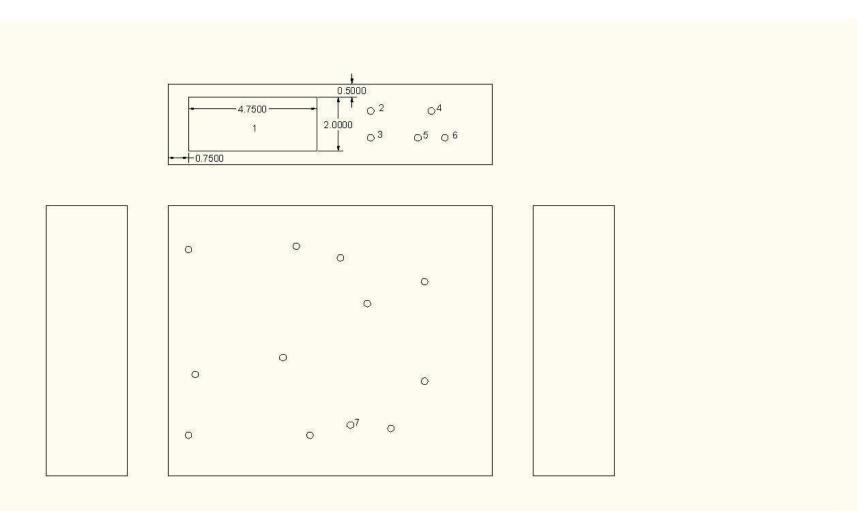

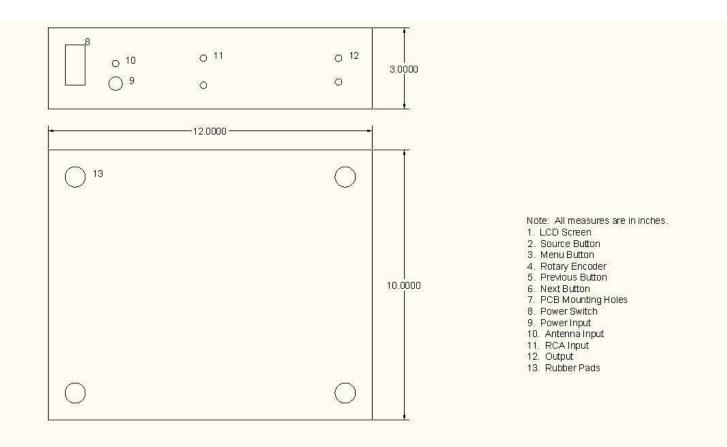

Next, the receiver base must be large enough to accommodate the LCD, rotary encoder, and push button user interface, and satisfy the EMI shielding constraint. The package will be the Bud Industries 12 x 10 x 3" aluminum sheet metal enclosure [4]. For easy accessibility, the user interface will be located on the front of the unit. The power input, audio input, and antenna will all be located in the rear of the unit as not to impede access to the UI. Four rubber pads will be added to the bottom of the unit to decrease the chance of the unit slipping off of a surface. Also, the aluminum case will effectively shield the circuit from electromagnetic interference. Copper tape will be used to fill gaps at connecting interfaces to completely EMI shield the system if necessary. Refer to Appendix B for detailed CAD drawings of packaging design and Appendix B for materials, tooling, weight, and unit cost details.

# 7.4 PCB Footprint Layout

For the components selected in the Design Constraints Analysis, most had either only one or a few footprints available. For the components with multiple footprints, two major characteristics were considered, overall footprint area and lead or pad solderability. Using these criteria, it was determined that PDIP packages were to be avoided as the through-hole leads effectively double the footprint of the chip. Next, extremely small packages such as QFN were avoided as soldering these components is difficult with the exception of the nRF24Z1 transceiver chip as QFN was the only available package. SOIC and TQFP were the packages of choice as they provide small footprints and reasonable solderability.

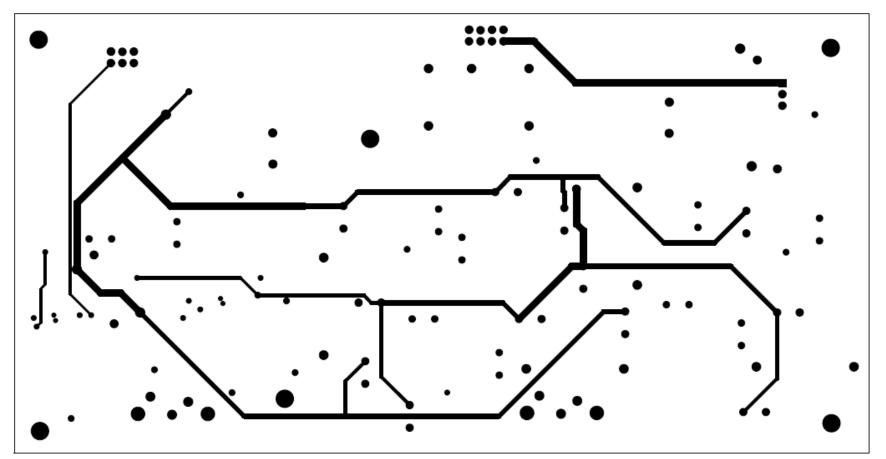

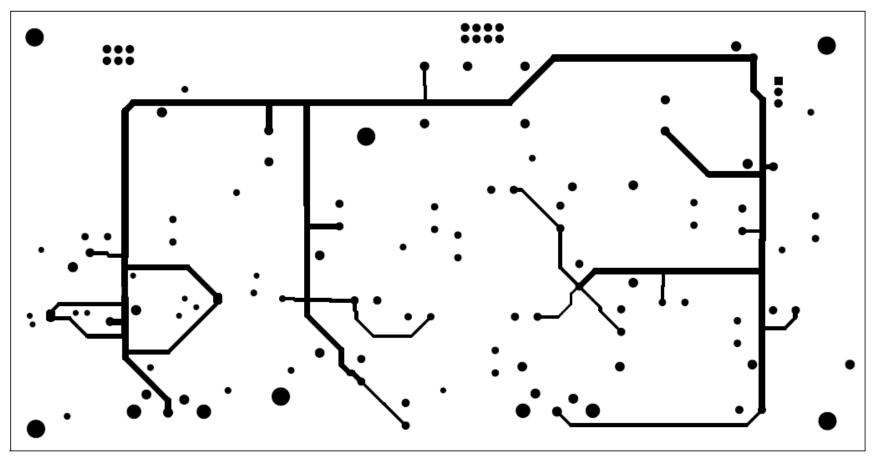

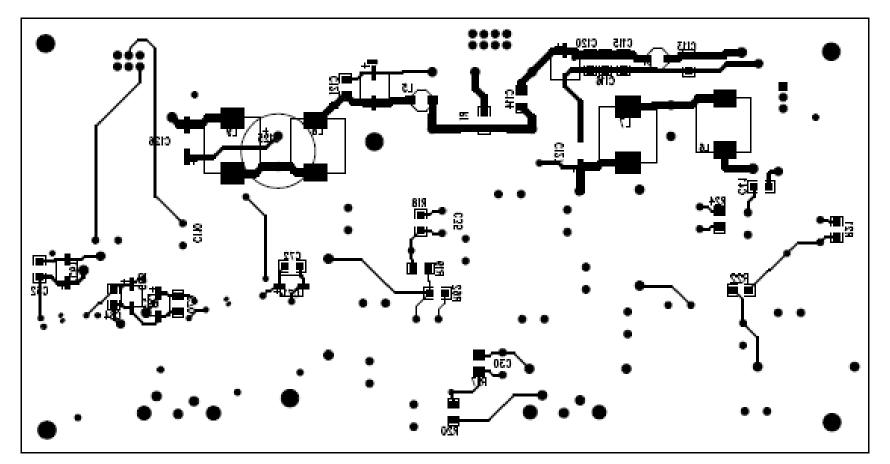

Next, the PCB dimension estimates will be 5 x 3", 7.446 x 3.833", and 6.499 x 4.555" for the transmitter board, receiver analog board, and receiver digital board respectively. For the transmitter, all active components fit on one side of the board leaving space for passive components and UI push button connectors. For the receiver, all active components easily fit onto the analog and digital circuit boards. This layout effectively isolates the analog and digital circuitry and allows for easy routing.

# 7.5 Summary

Overall, the packaging design will be very similar to that of the Shure and Sennheiser commercial systems. The ABS transmitter package will be small at  $3 \ge 2 \ge 1$  inch, lightweight, and user friendly. The aluminum receiver package will be large enough to accommodate the UI at 7.4  $\ge 4.75 \ge 3.2$  inches, provide EMI shielding, and provide easy access to the UI on the top face. The transmitter and receiver PCB layouts at 2.8  $\ge 1.8$  inches and 7.0  $\ge 4.2$  inches, respectively, are large enough for all active components and will fit within the chosen package designs.

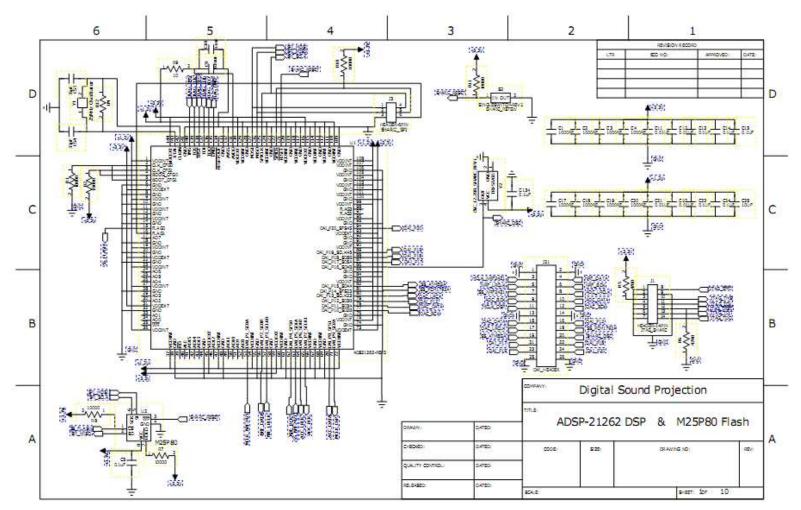

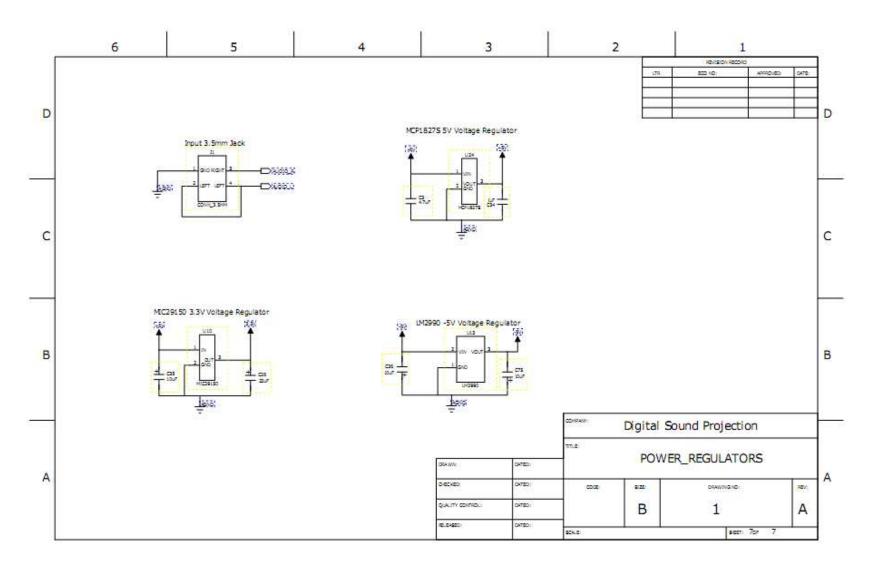

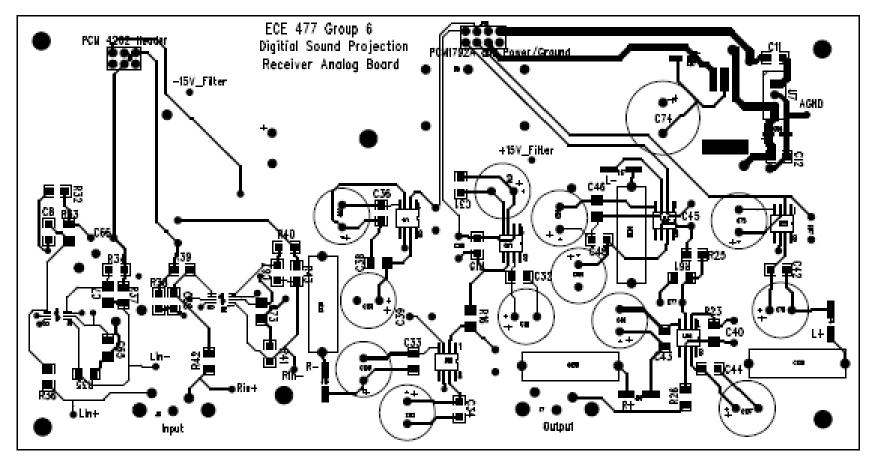

# 8.0 Schematic Design Considerations

#### 8.1 Introduction

Digital Sound Projection consists of a transmitter and a receiver base station for transmitting digital audio through the air. Since the transmitter is battery based, there will be a tradeoff between SNR and power consumption. The receiver station was designed to either receive the digital audio wirelessly or to accept analog input from the analog to digital converter. The base station will then perform an N point Fast Fourier Transformation (FFT) to get a rough estimation of the frequency domain. By adjusting the frequency bands, users will be able to apply EQ effects by interacting with a user interface. After all the computations are done, the digital signal processor will then send the reconstructed digital audio signal to the digital to analog converter. On the PCB, left and right channels are laid out separately to reduce the effect of inter-channel contamination. The digital circuitry is also separated from analog components to reduce electromagnetic interference effects.

# 8.2 Theory of Operation

The transmitter contains three major subsections which include the microphone input, unit control, and wireless transmitter. The microphone input section uses a pair of Texas Instruments PGA2505s, one for each channel. The PGA2505 has a serial control interface, gain up to one thousand, and accepts small differential signal inputs. The PGA2505 output is set to a voltage swing of 0 to 5V on  $V_{out+}$  and  $V_{out-}$  with a common reference voltage ( $V_{com}$ ) equal to 2.5V. The PGA2505 common voltage reference is set to match the PCM4202 ADC reference voltage ( $V_{ref}$ ). To further process the input, the signal is passed to the PCM4202 that quantizes the analog input into I2S output with 48kHz/24bit bit rate.

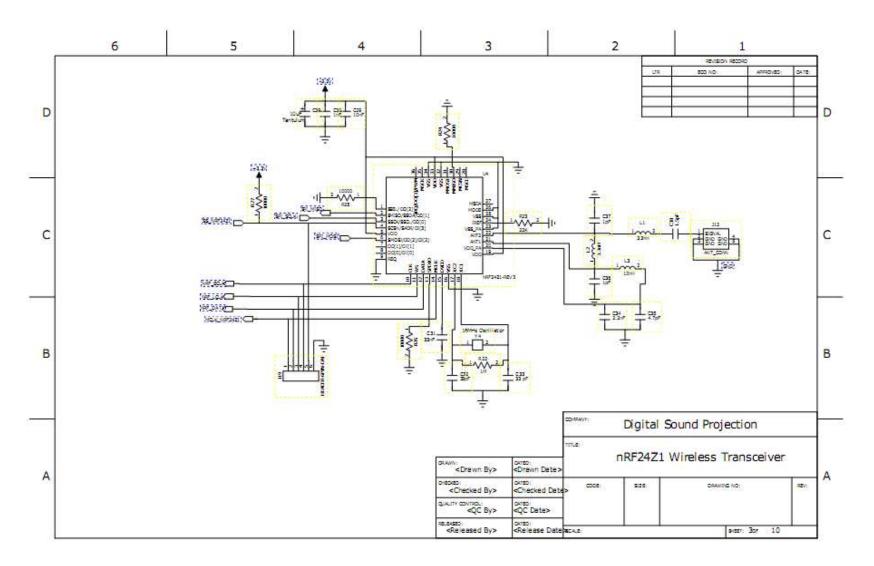

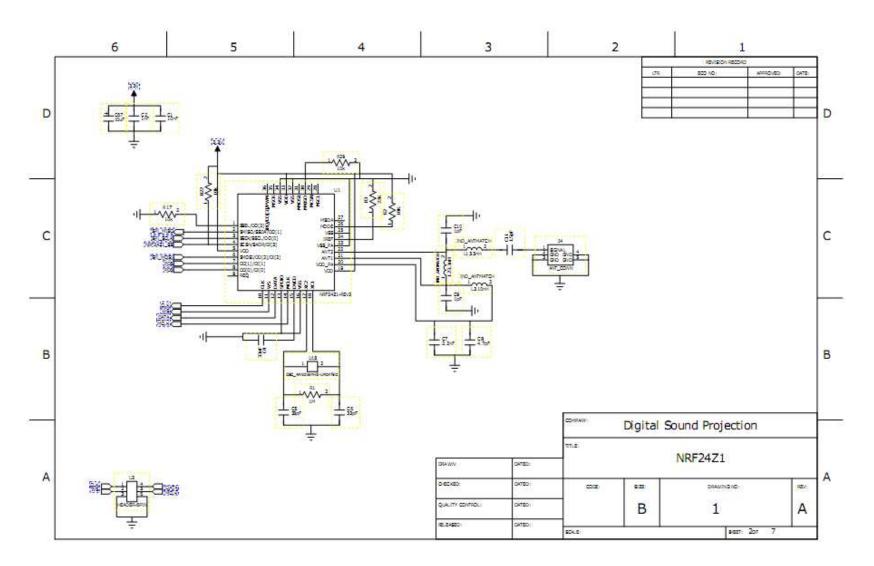

The Nordic Semiconductor nRF24Z1 wireless transceiver receives I2S input from the PCM4202 and performs bit truncation to compress the input down to 16-bit. The nRF24Z1 also provides channel coding to guarantee quality of service between transmitter and receiver; it generates protection codes and a CRC checksum to correctly receive data. To modulate the digital audio for transmission, the nRF24Z1 passes data to a Gaussian filter and then multiplies its output with 38 different carrier frequencies between 2.4GHz to 2.45GHz simultaneously to select an optimal transmission frequency. In order to transmit at 2.4GHz, a high frequency

capacitor is used between antenna ground and digital ground to prevent interference. A 12.288MHz is used to drive the I2S clocks between the nRF24Z1, PCM1792a DAC and PCM4202 ADC.

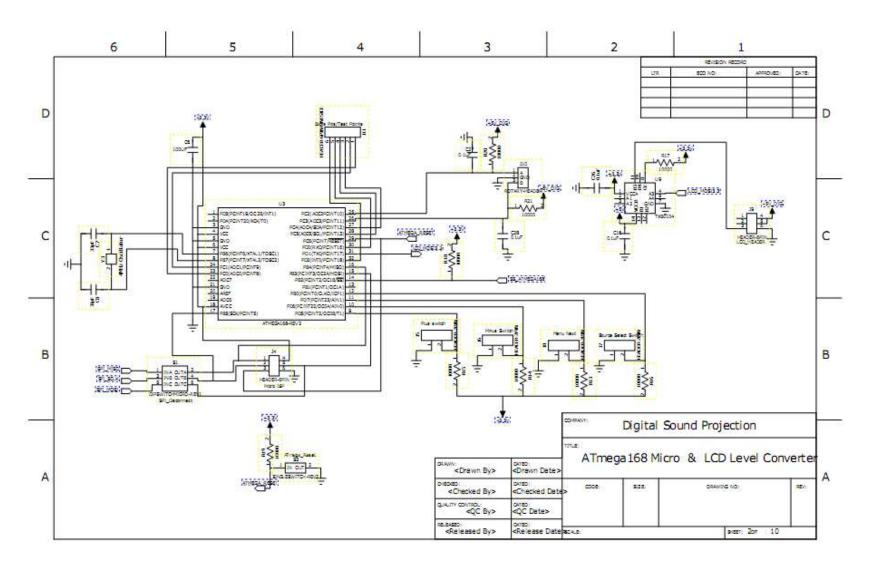

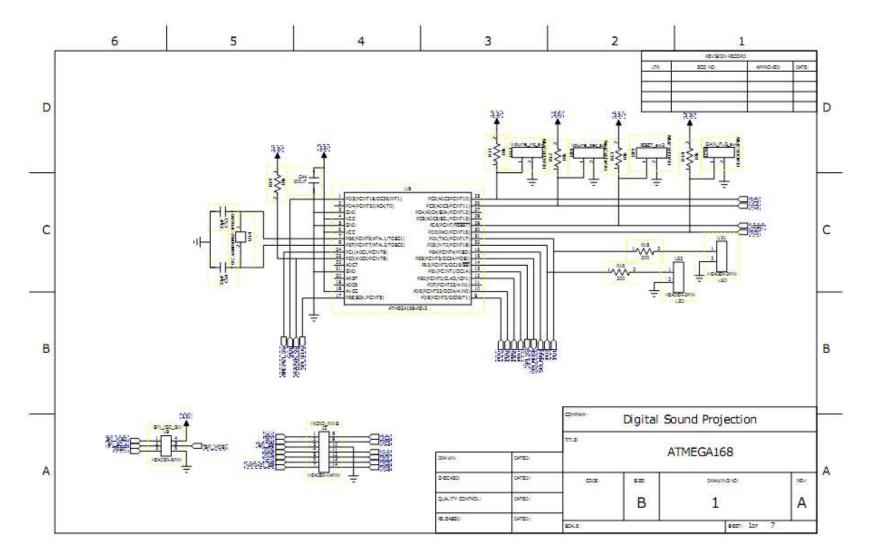

An ATmega168 microcontroller handles the control of the user interface on the transmitter and receiver. The clock speed of 4MHz for is sufficient to operate the user interface and control the nRF24Z1. The microcontroller debounces external pushbutton inputs and decodes the quadrate encoder signals.

On the transmitter, the analog output is driven between +5V and -5V and the digital components operate at 3.3V. All of the above voltages are generated from two 6V battery packs and regulated separately by low drop-off linear voltage regulators.

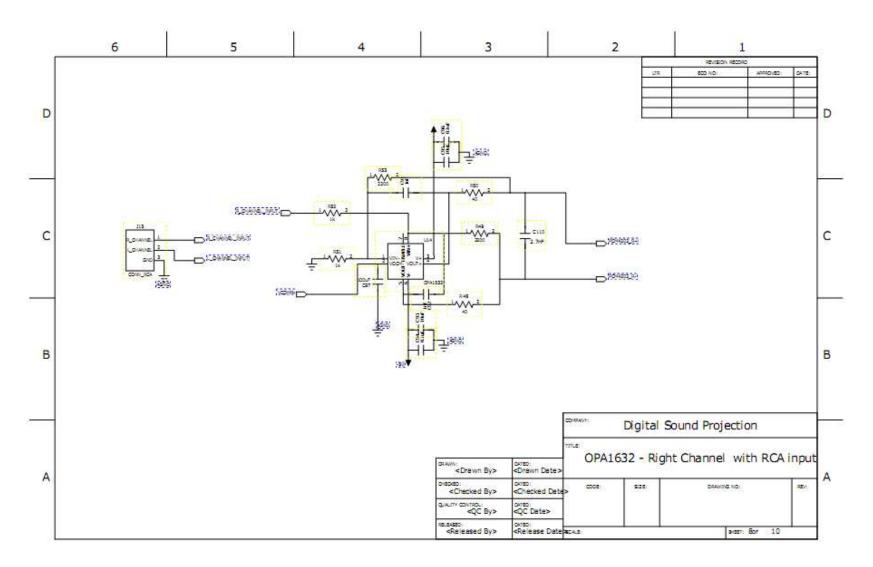

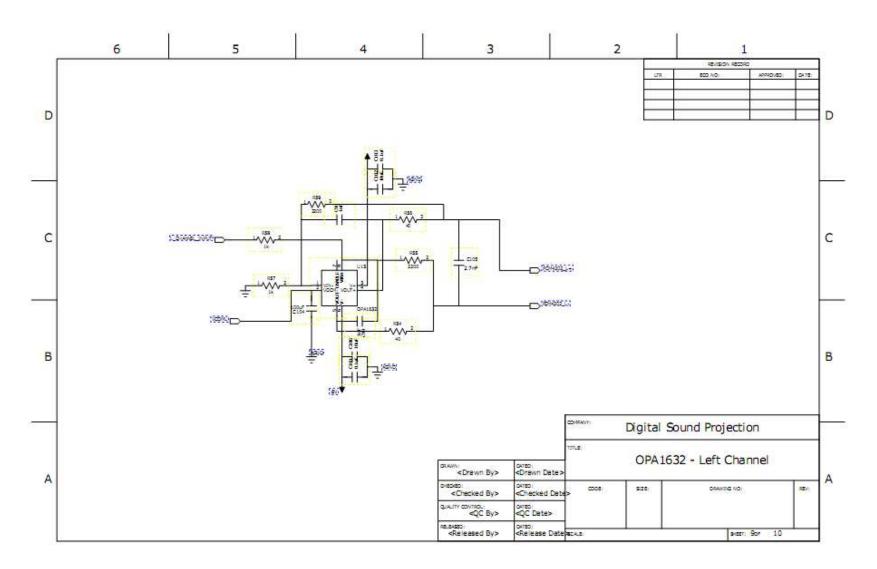

On the receiver, inputs can come from either the wireless input or analog line-in from the RCA stereo jack. The nRF24Z1 receives digital audio from an antenna and the chip then utilizes a Phase Lock Loop (PLL) with self-clock regeneration to decode Gaussian Phase Shift Keying (GPSK) back to I2S with additional checksum and error corrections. From the RCA analog line-in port, the analog audio is first converted into differential pair with 2.5V DC offset by OPA1632 then is sent to PCM4202 to quantize the 0V<Vin<5V analog signal to an I2S digital audio signal. Since mic-in is not implemented, a PGA2505 is not necessary on receiver side.

The I2S signal from either the wireless or line-in input is then sent to Analog Devices' SHARC ADSP-21262 for EQ and digital mute processing. The SHARC takes the I2S input and saves the sample points into two separate N (N = 1024 or 2048) real number floating point buffers with a fill time of 20ms or 40ms, respectively, for the left and right channels. Since the user will be able to adjust the input signal's behavior in the frequency domain, a Short Time Fourier Transformation (STFT) is needed to convert time domain into frequency domain. An optimized FFT function provided by the Virtual DSP library from Analog Device is used. In order to FFT each individual channel, one complex N point and one real N point buffer is allocated; N twiddle coefficients (complex points) are generated and saved into memory. After the FFT calculation and frequency convolutions (EQ effects and other frequency based operations), an inverse FFT (IFFT) of length N is used to convert the frequency domain back to time domain in order to reconstruct the digitized signal. The entire computation should not exceed the time required to build N samples input buffers based on the 200MHz clock frequency of the SHARC, which is insignificant compared to the 20ms to 40ms required sampling time.

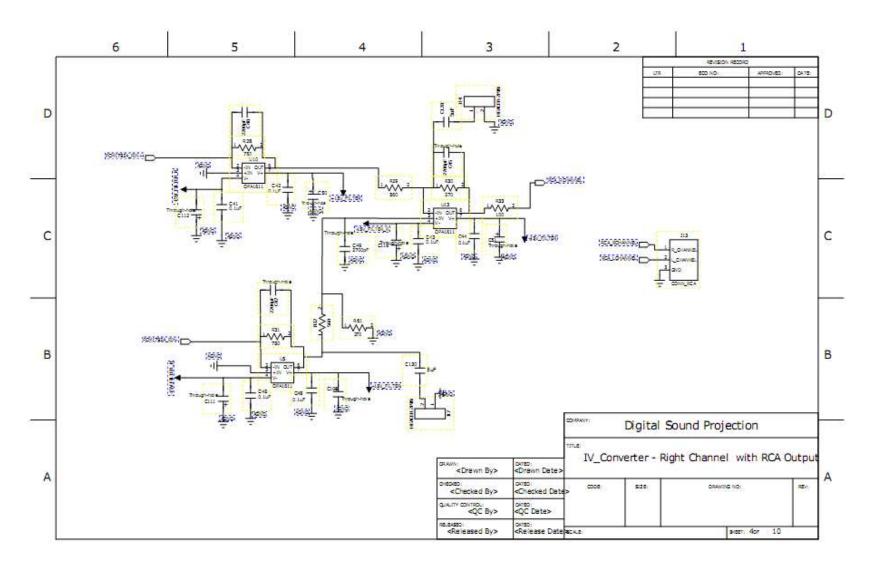

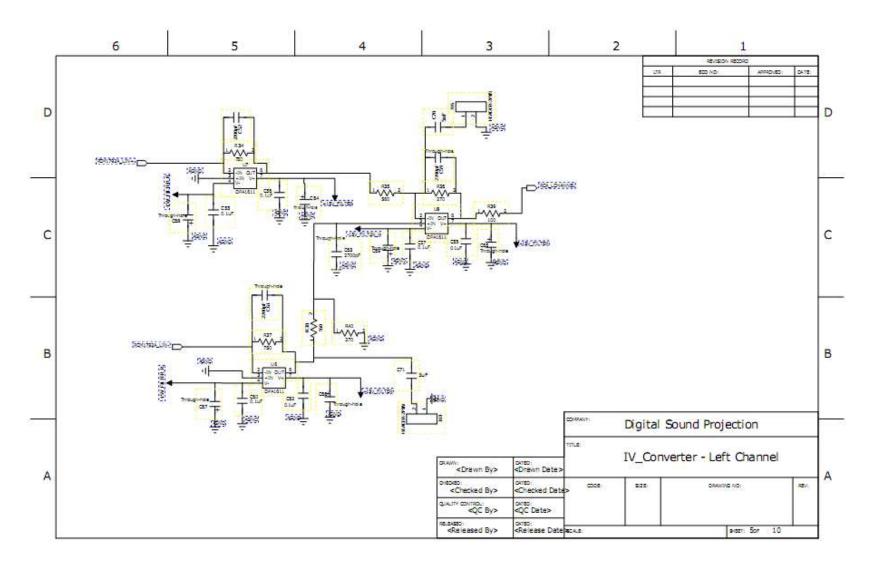

The PCM1792A reconstructs the processed digital audio sent from the SHARC to analog current driven differential outputs, Iout+ and Iout-. A set of bi-amp I/V current integrators are implemented to convert Iout to Vout with Vavg of 2V and Vpp of 4V. To generate RCA output, another bi-amp configuration is used to combine differential output into singled RCA output.

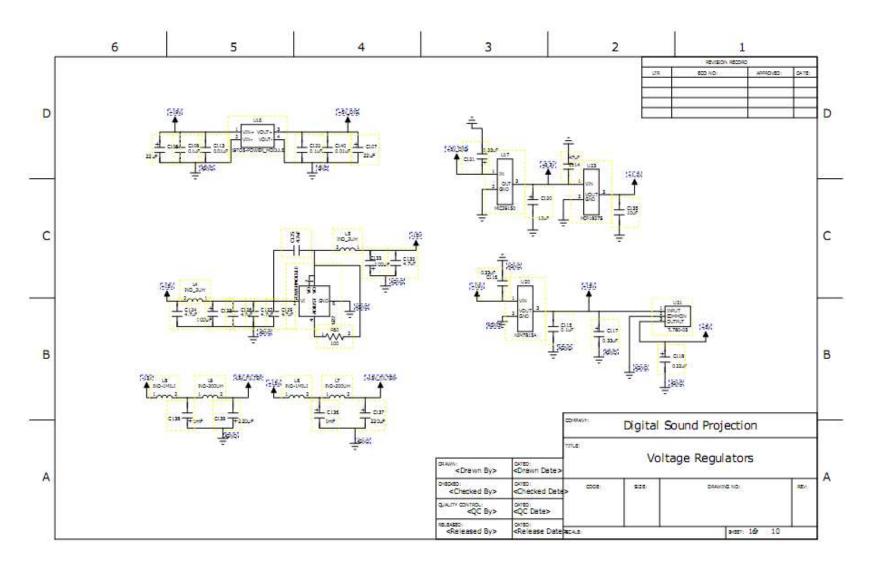

The receiver uses a 19V, 3.15A wall wart with one +19V to +5V power module for the digital board power and +15V to -15V power module for the analog board negative supply reel. The +15V and -15V on the analog board are first filtered with two LC filters in series (Fc<sub>1</sub> = 400Hz and Fc<sub>2</sub> = 2000Hz then filtered again by bypass and decouple capacitors to ensure the clearness of the power supply for OPA1611 op-amps, +5V for Vcc on PCM1792 and PCM4202, and +3.3 for Vdd on our digital devices. The SHARC requires 1.2V supply for its internal core voltage which will be generated from a +3.3V to +1.2Vlinear voltage regulator to prevent overheating.

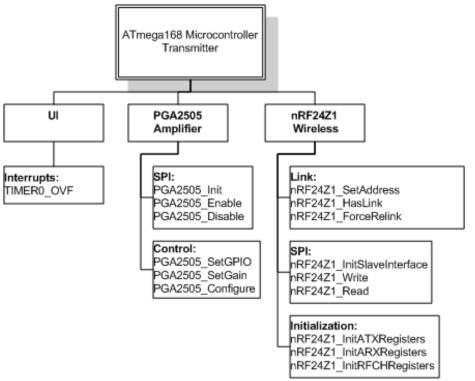

# 8.3 Hardware Design Narrative

On the transmitter, three pins on ATmega168 microcontroller will be utilized for SPI: serial clock, master out slave in, and slave devices master in slave out. Two additional pins are used to select between the PGA2505 and nRF24Z1. To give user control of output volume on the receiver from the transmitter, two pins are used for reading from push buttons. Also there will be two additional pins on the ATmega168 to read the user input regarding analog input gain selection. On ATmega168, all the unused pins are tied to ground through resistors to avoid EMI effects.

The PGA2505 communicates with the ATmega168 using SPI to adjust gain between 0dB to 60dB. In order to generate 0-5V differential output for the PCM4202, the PGA2505 reads Vref from PCM4202, uses it as an output common ground (Vcom), and generates voltage outputs accordingly.

The PCM4202 is set to PCM mode with 12.288MHz clock signal from the nRF24Z1. After the PCM4202 digitizes the analog input, it then sends the digital audio to the nRF24Z1. I2S with word length of 24bits is selected for this operation; it uses three pins for I2S data, I2S bit clock, and I2S frame-sync. On the PCM4202, all the unused modes, including DSD and multi-bit modulator mode, are disabled.

The nRF24Z1 is configured by the ATmega168 with one mode select (either Tx or Rx) pin, two volume control inputs de-bounced by the ATmega168, and the SPI bus. The nRF24Z1 reads I2S input from the PCM4202 and adds additional volume reading to the end of the audio bit stream. This signal is then transmitted via a 2.4GHz channel. On the nRF24Z1, the "antenna 2" output is tied to ground and all other unused pins are tied to ground to prevent EMI effects.

On the receiver, the PCM4202 is set to have the same data output format as the one on the transmitter. Chip select pins are set to source digital audio between the nRF24Z1 and the PCM4202. All the unused I/O are tied to ground and all the unused functions are disabled for both the nRF24Z1 and the PCM4202.

The SHARC Digital Signal Processor receives an I2S signal from either the PCM4202 or the nRF24Z1 and buffers the input data stream in internal RAM to perform digital signal processing on the digital audio. Since the SHARC has the most of GPIO pins and fastest clock speed, it is used as the master SPI device to select between different SPI controlled subsystems and sends out a reset flag to each subsystem every time the receiver restarts. Also, the SHARC requires an additional SPI based flash chip to store its boot-image.

An ATmega168 microcontroller is also used to show user device status, to read user inputs, and to drive the LCD display. The microcontroller is driven by the SHARC over SPI buses and reads user input from push buttons and rotary knobs. Analog rotary encoders and push buttons will take eight pins on the microcontrollers. The LCD display module is driven by the ATmega168 with two serial port pins, two LCD read/write pins, and one LCD chip select pin.

# 8.4 Summary

The transceiver is designed with low power consumption. A minimum amount of chips are used to reduce power consumption and pin connections. The transmitter uses the ATmega168 as a central processing unit to control the PGA2505, PCM4202, and nRF24Z1. The PGA2505 is connected to a single input to differential output converter and generates high gain voltage output. The PCM4202 reads the voltage s from both the positive and negative of the differential input and output I2S digital audio to the nRF24Z1. The nRF24Z1 accepts the I2S signal and performs input compression and channel coding before sending the modulated signal via a 2.4GHz wireless channel.

On the receiver, the nRF24Z1 receives an input signal from an external antenna and decodes the modulated input to an I2S digital audio. An additional PCM4202 is used on the receiver to read analog line-in input. The SHARC DSP has a chip select function to select the input source between the nRF24Z1 and PCM4202. The SHARC performs frequency analysis and applies frequency convolution to the digital audio signal. After frequency operations, the SHARC then sends the processed digital audio signal to the PCM1792. The PCM1792 takes the I2S data and converts it back to current driven differential outputs. The ATmega168 is used on the receiver to show device status, to read user inputs, and to drive the LCD display. The ATmega168 reads user inputs from a rotary encoder and push buttons. All the subsystems on the receiver side, with the exception of the PCM4202, are controlled by the SHARC using SPI buses. The entire system is powered by a 19V DC input and is sent to one +19V to +5V power module and one +19V to -15V power module with linear voltage regulators to acquire desired voltage outputs.

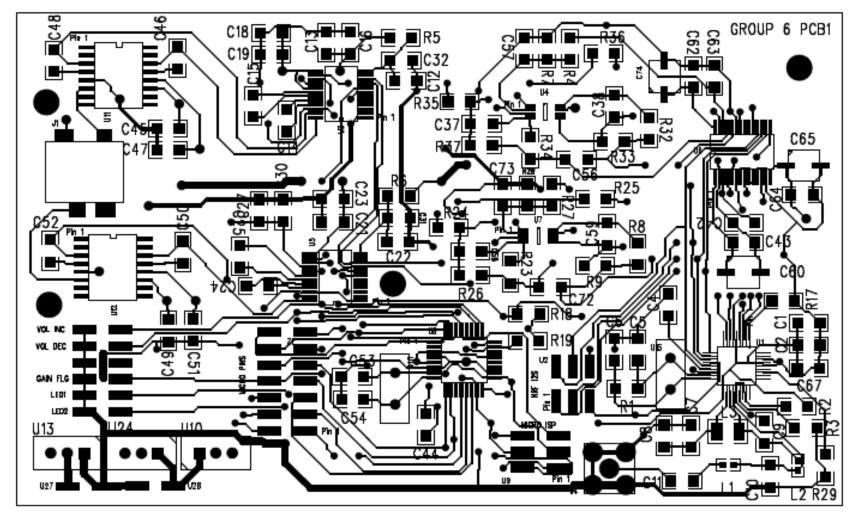

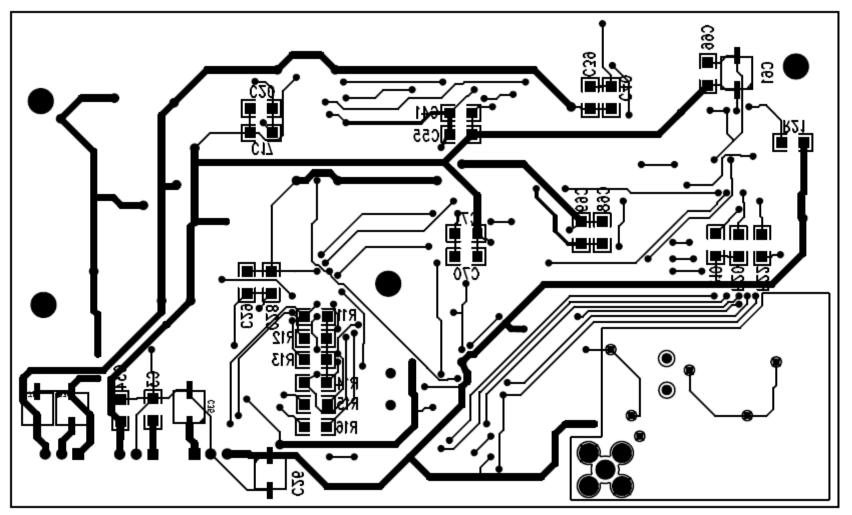

### 9.0 PCB Layout Design Considerations

#### 9.1 Introduction

As a design consideration, the transmitter circuit board will have to be small in order to retain the portability of a handheld device; however, there are specific limitations with some of the chip layouts that will require additional space on the board. However, there are limitations on how small the circuit boards can be due to noise considerations, placement of chips for convenient traces, and also based on the manufacturers' data sheets for each chip.

#### 9.2 PCB Layout Design Considerations – Overall

The project requires two separate printed circuit board designs: one transmitter and one receiver. The transmitter and receiver boards both have very similar requirements; however, the transmitter has the additional requirement of small size. As a benefit, the transmitter requires fewer physical chips and external connections, which will allow for less circuitry.

The nRF24Z1 transceiver is a major imitation on the size of the circuit boards, specifically the transmitter. This chip requires that the nRF24Z1 be placed alone on the board with no components or traces running underneath. The transceiver must also be placed close to the edge of the board where the SMA antenna connector is located so that traces are short. This is done to avoid the EMI radiation of the received wireless signal from the antenna, because if the trace is longer than a specific value depending on the frequency, then the electromagnetic fields could radiate off the trace as if it was an antenna itself. Keeping the antenna connection close to the nRF24Z1 chip will also help retain the characteristics of the 50 ohm matched output circuit without having to meet additional requirements concerning the physical trace as outlined in the layout application note. If there is a reason for the nRF24Z1 impedance matching network to require more board space, then the design must use a 50-ohm micro strip line to carry the signal [1]. In order to place the nRF24Z1 at the side of the board near the edge, the chip should be situated such that the I/O pins face the interior of the board in order to eliminate inefficient trace design.

A major concern for the layout is the risk of noise contamination between the chips themselves. This specifically is a consideration of the noise contribution that the analog devices on the circuit boards would have with the digital components. The first part of the solution for this problem is simple by creating two separate boards for the receiver: one board for the analog components and one board for the digital components. This will also help separate the analog and digital grounds, which will reduce noise between the two different types of components. A header will then be needed to connect the two boards with the important signal and power/ground traces that are common between the two boards. With two separate boards, it is preferred that the sizes are kept to a minimum in order to fit the receiver into the chosen receiver package. To minimize the size some planning is needed to draw out, by hand, the orientation and placement of the chips to most efficiently use the board space. The transmitter design will only be placed on one board and due to size constraints the only solution is to separate the analog and digital chips on opposite sides of the board. There will not be much space in between the chips, but this could possibly help reduce noise contamination between the components.

Each printed circuit board for the receiver will be a four layer board and the transmitter will be a two layer board. This will require strategic routing and placement of the off-chip circuitry. In order to use as much board space as possible while maintaining minimum size, careful planning will be needed to place traces, passive, and active components on both sides of the board. To prevent further noise contamination, no traces or noisy components should be placed underneath the chips themselves. The multiple layers will also allow for bypass and decoupling capacitors to be placed right next to the pins on one side of the board without interfering with any of the traces between chips. The Op-Amps (OPA1632, DRV134, PGA2505) will require as short of a trace as possible in order to prevent small signal oscillation while operating at the expected values, which can be done by taking advantage of the two layers. The maximum current draw for any of the chips' signal pins does not exceed 100mA, which means the width of the signal traces can be at the minimum 10-12 mil width. This will help in routing because there will be less space on the PCB used to route these thin traces.

One other consideration for the layout of the project's circuit boards will be the off board peripherals. The antennas, microphone input, RCA input, and RCA output will all be connected using surface mount or through-hole connectors on the boards. These connectors will have to be placed on the edge of the board but also close to the respective chips for which they are inputs or outputs. The boards will also require several headers for programming chips like the ATmega168 microcontroller and the ADSP-21262 DSP. These headers will also give an opportunity to make use of extra unused pins of chips to provide alternatives in case of pins

burning out. Space will need to be allocated for these headers, which will increase the size of the board, specifically for the SHARC's 26 pin DAI header and 16 pin JTAG header, and also require additional planning for the placement with respect to the chips that they are connected to so that there is no risk of crossing traces. The user interface including the LCD, pushbuttons, batteries, and LEDs will also require some header connections since these devices will not be connected to the PCBs directly but will be placed on the project casing. The other decision with the headers is whether to use surface mount or through-hole. Any through-hole mounting will essentially eliminate possible trace routing on both sides of the board where these headers are located while surface mount would only take up space on one side of the board. If any through-hole components are used, then these should be placed such that they would not interfere with any traces on either side of the board.

#### 9.3 PCB Layout Design Considerations – Microcontroller

The circuit board layouts for the ATmega168 Microcontroller and the SHARC ADSP-21262 DSP are similar to the rest of the chips on the boards. Bypass and decoupling capacitors need to be placed as close to the pins as possible to reduce noise on the supply pin. The same aspect applies with the oscillator circuit that must be placed close to the pins of the nRF24Z1 transceiver, ATmega168 microcontroller, and SHARC ADSP-21262. With several components that need to be placed next to these chips, then both sides of the board will need to be taken advantage of. This is important for the SHARC due to its large number of power and ground pins. These power traces will need to be larger than the signal traces (around 60-100 mils in width), but will need to gradually decrease in width to match the width of the pins so they do not interfere with the rest of the connections to the chip. This reduces the amount of resistance for the large current ratings from the power supplies and prevents burning out traces. In addition, both the SHARC and the ATmega168 will require large headers and extra space on the board in order to program the chips and to access unused pins as a back up to any burned pins.

#### 9.4 PCB Layout Design Considerations - Power Supply

The placement of the voltage regulators for each circuit board is a major concern for the design because of the noise that these devices produce. A solution to this problem is to place the