MF761-03

# CMOS 4-BIT SINGLE CHIP MICROCOMPUTER E0C6256 TECHNICAL MANUAL

# E0C6256 Technical Hardware E0C6256 Technical Software

**SEIKO EPSON CORPORATION**

#### NOTICE

No part of this material may be reproduced or duplicated in any form or by any means without the written permission of Seiko Epson. Seiko Epson reserves the right to make changes to this material without notice. Seiko Epson does not assume any liability of any kind arising out of any inaccuracies contained in this material or due to its application or use in any product or circuit and, further, there is no representation that this material is applicable to products requiring high level reliability, such as medical products. Moreover, no license to any intellectual property rights is granted by implication or otherwise, and there is no representation or warranty that anything made in accordance with this material will be free from any patent or copyright infringement of a third party. This material or portions thereof may contain technology or the subject relating to strategic products under the control of the Foreign Exchange and Foreign Trade Law of Japan and may require an export license from the Ministry of International Trade and Industry or other approval from another government agency. Please note that "EOC" is the new name for the old product "SMC". If "SMC" appears in other manuals understand that it now reads "EOC".

## PREFACE

This manual is individually described about the hardware and the software of the E0C6256.

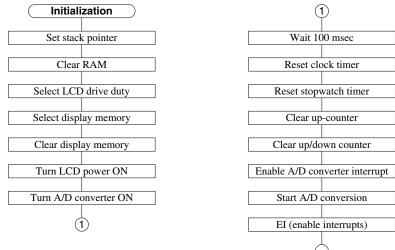

# I. E0C6256 Technical Hardware

This part explains the function of the E0C6256, the circuit configurations, and details the controlling method.

# II. E0C6256 Technical Software

This part explains the programming method of the principal functions of the E0C6256.

# E0C6256 Technical Hardware

### **CONTENTS**

| CHAPTER 1 | 0v       | ERVIEW                                                                  | I-1          |

|-----------|----------|-------------------------------------------------------------------------|--------------|

|           | 1.1      | Features                                                                |              |

|           | 1.2      | Block Diagram                                                           | <i>I-2</i>   |

|           | 1.3      | Pin Layout Diagram                                                      |              |

|           |          |                                                                         |              |

|           | 1.4      | Pin Description                                                         | 1-4          |

| CHAPTER 2 | Po       | wer Supply and Initial Reset                                            | I-5          |

|           | 2.1      | Power Supply                                                            | <i>I-5</i>   |

|           |          | 2.1.1 Supply voltage doubler/halver and operating mode                  |              |

|           |          | 2.1.2 Voltage <vs1> for oscillation circuit and internal circuits</vs1> |              |

|           |          | 2.1.3 Voltage <vl1, and="" vl2="" vl3=""> for LCD driving</vl1,>        |              |

|           | 2.2      | Initial Reset                                                           |              |

|           |          | 2.2.1 Reset terminal (RESET)                                            |              |

|           |          | 2.2.2 Simultaneous high input to terminals K00–K03                      |              |

|           |          | 2.2.3 Oscillation detection circuit                                     |              |

|           |          | 2.2.4 Watchdog timer<br>2.2.5 Internal register at initial resetting    |              |

|           | <u> </u> |                                                                         |              |

|           | 2.3      | Test Terminals (TEST, CP)                                               | 1-8          |

| CHAPTER 3 | СР       | U, ROM, RAM                                                             | I-9          |

|           | 3.1      | СРИ                                                                     | <i>I-9</i>   |

|           | 3.2      | ROM                                                                     | <i>I-</i> 9  |

|           | 3.3      | RAM                                                                     |              |

|           | 5.5      |                                                                         |              |

| CHAPTER 4 | Per      | RIPHERAL CIRCUITS AND OPERATION                                         | I-10         |

|           | 4.1      | Memory Map                                                              | <i>I-10</i>  |

|           | 4.2      | Power Supply and Operating Mode Settings                                | <i>I-18</i>  |

|           |          | 4.2.1 Operating mode                                                    |              |

|           |          | 4.2.2 LCD drive voltage                                                 | <i>I-19</i>  |

|           |          | 4.2.3 Control of power supply and operating mode                        |              |

|           |          | 4.2.4 Programming notes                                                 | <i>I-20</i>  |

|           | 4.3      | Resetting Watchdog Timer                                                |              |

|           |          | 4.3.1 Configuration of watchdog timer                                   |              |

|           |          | 4.3.2 Mask option                                                       |              |

|           |          | 4.3.3 Control of watchdog timer                                         |              |

|           |          | 4.3.4 Programming note                                                  |              |

|           | 4.4      | Oscillation Circuit                                                     |              |

|           |          | 4.4.1 Configuration of oscillation circuit                              |              |

|           |          | 4.4.2 OSC1 oscillation circuit                                          |              |

|           |          | 4.4.3 OSC3 oscillation circuit<br>4.4.4 Operating voltage switching     |              |

|           |          | 4.4.5 Clock frequency and instruction execution time                    |              |

|           |          | 4.4.6 Control of oscillation circuit                                    |              |

|           |          | 4.4.7 Programming notes                                                 |              |

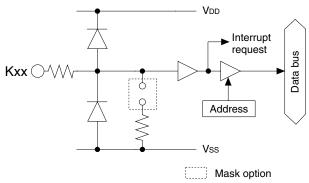

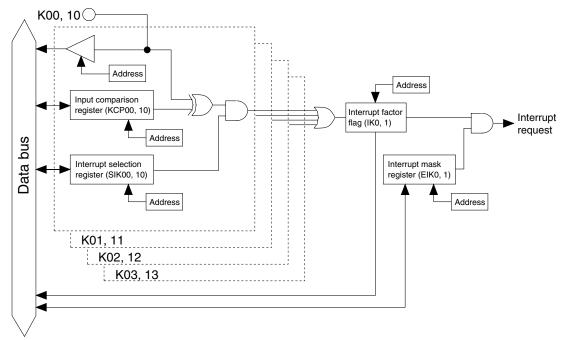

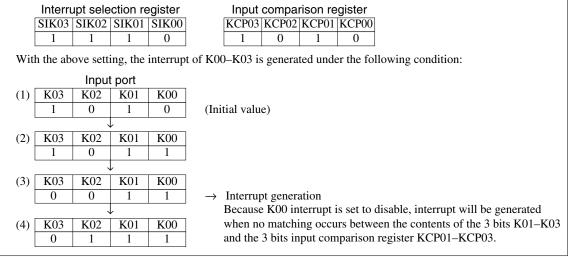

|           | 4.5      | Input Ports (K00–K03, K10–K13)                                          |              |

|           |          | 4.5.1 Configuration of input ports                                      |              |

|           |          |                                                                         |              |

|           |          | 4.5.2 Interrupt junction                                                | <i>I-</i> 20 |

|           |          | 4.5.2 Interrupt function<br>4.5.3 Mask option                           | <i>I-27</i>  |

|           |          |                                                                         | I-27<br>I-28 |

#### CONTENTS

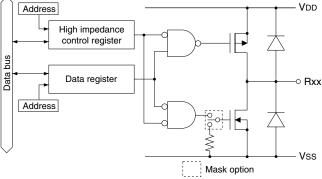

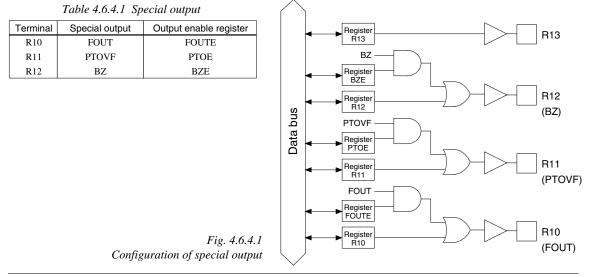

| 4.6  | Output Ports (R00–R03, R10–R13)                                                        | <i>I-31</i>  |

|------|----------------------------------------------------------------------------------------|--------------|

|      | 4.6.1 Configuration of output ports                                                    | <i>I-31</i>  |

|      | 4.6.2 Mask option                                                                      |              |

|      | 4.6.3 High impedance control                                                           | <i>I-31</i>  |

|      | 4.6.4 Special output                                                                   |              |

|      | 4.6.5 Control of output ports                                                          |              |

|      | 4.6.6 Programming notes                                                                | <i>I-34</i>  |

| 4.7  | I/O Ports (P00–P03, P10–P13)                                                           | <i>I-35</i>  |

|      | 4.7.1 Configuration of I/O ports                                                       | <i>I-35</i>  |

|      | 4.7.2 I/O control registers and input/output mode                                      | <i>I-35</i>  |

|      | 4.7.3 Pull down during input mode                                                      | <i>I-35</i>  |

|      | 4.7.4 Mask option                                                                      |              |

|      | 4.7.5 Control of I/O ports                                                             | <i>I-36</i>  |

|      | 4.7.6 Programming note                                                                 | <i>I-37</i>  |

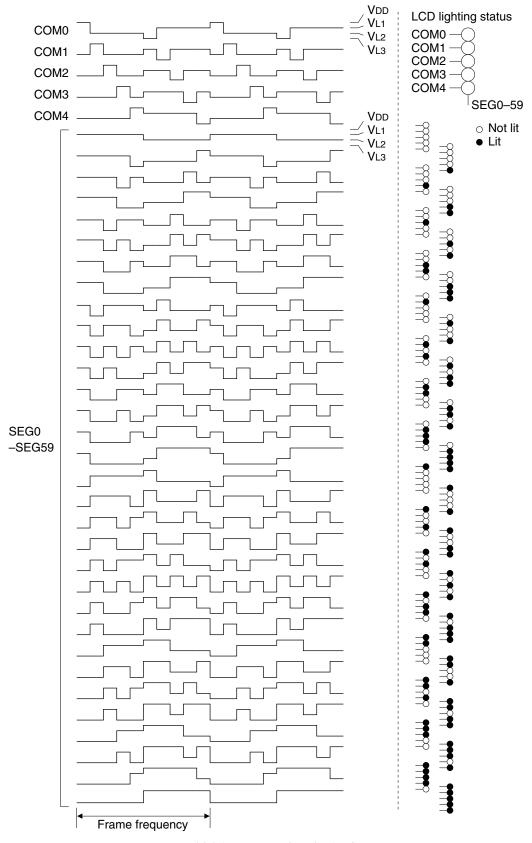

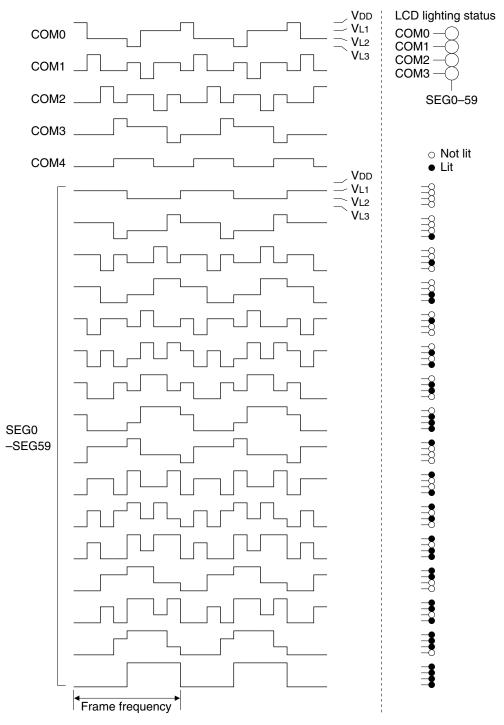

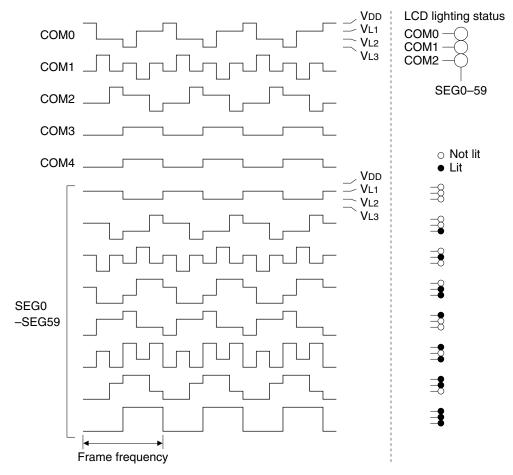

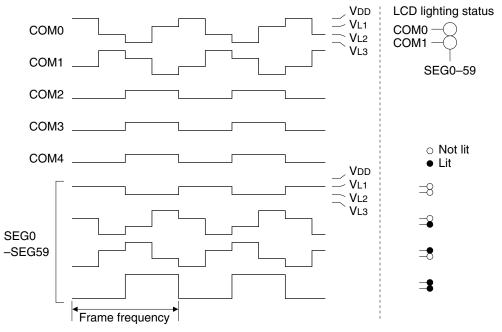

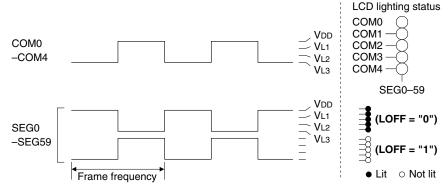

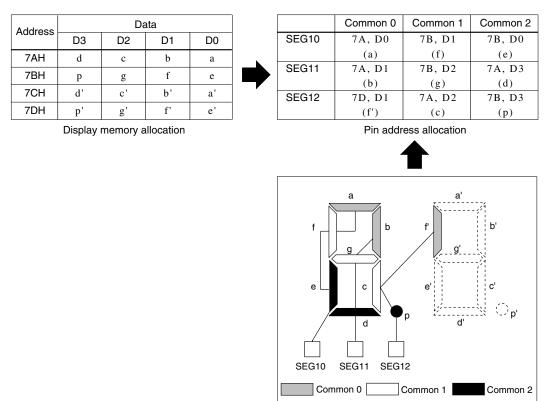

| 4.8  | LCD Driver (COM0–COM4, SEG0–SEG59)                                                     | <i>I-3</i> 8 |

|      | 4.8.1 Configuration of LCD driver                                                      | <i>I-38</i>  |

|      | 4.8.2 LCD drive voltage                                                                | <i>I-38</i>  |

|      | 4.8.3 LCD display ON/OFF control and duty switching                                    | <i>I-39</i>  |

|      | 4.8.4 Switching between dynamic and static drive                                       |              |

|      | 4.8.5 Display memory area                                                              |              |

|      | 4.8.6 Mask option (segment allocation)                                                 |              |

|      | 4.8.7 Control of LCD driver                                                            |              |

|      | 4.8.8 Programming notes                                                                | <i>I-47</i>  |

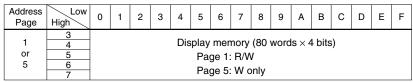

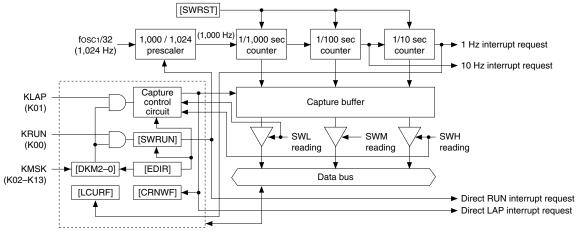

| 4.9  | Clock Timer                                                                            | <i>I-48</i>  |

|      | 4.9.1 Configuration of clock timer                                                     |              |

|      | 4.9.2 Data reading and hold function                                                   |              |

|      | 4.9.3 Interrupt function                                                               |              |

|      | 4.9.4 Control of clock timer                                                           |              |

|      | 4.9.5 Programming notes                                                                |              |

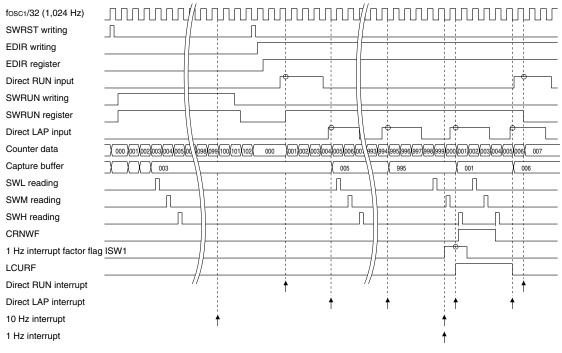

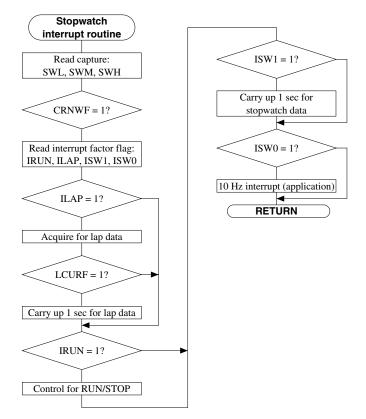

| 4.10 | Stopwatch Timer                                                                        |              |

|      | 4.10.1 Configuration of stopwatch timer                                                |              |

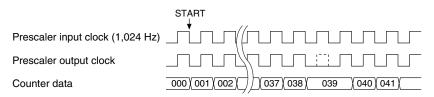

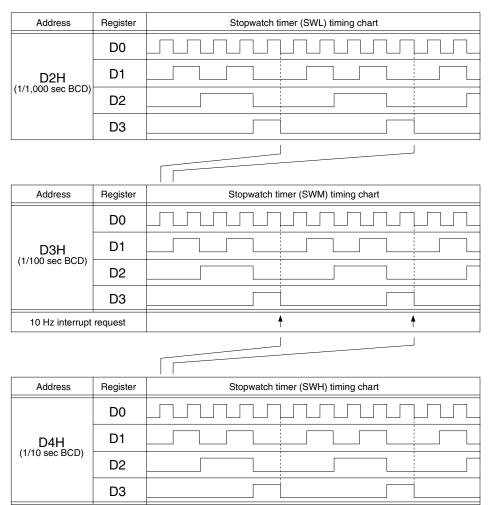

|      | 4.10.2 Counter and prescaler                                                           |              |

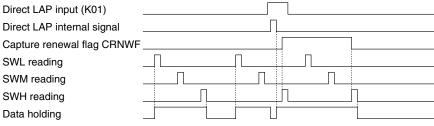

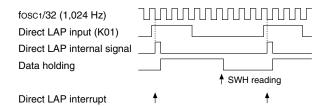

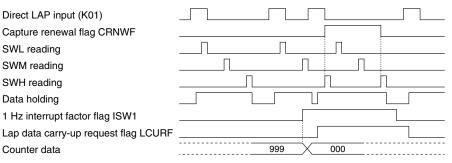

|      | 4.10.3 Capture buffer and hold function                                                |              |

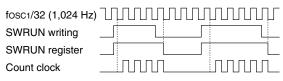

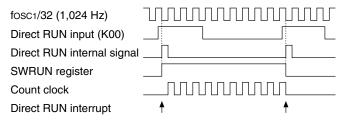

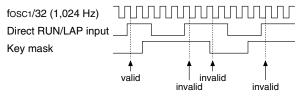

|      | 4.10.4 Stopwatch timer RUN/STOP and reset<br>4.10.5 Direct input function and key mask |              |

|      | 4.10.6 Interrupt function                                                              |              |

|      | 4.10.7 Control of stopwatch timer                                                      |              |

|      | 4.10.8 Programming notes                                                               |              |

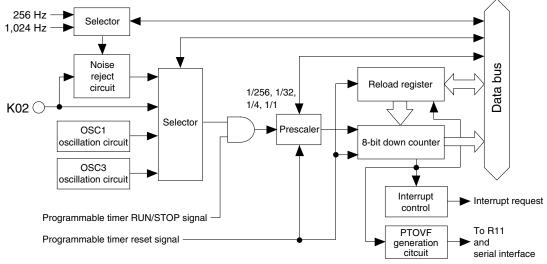

| A 11 | Programmable Timer                                                                     |              |

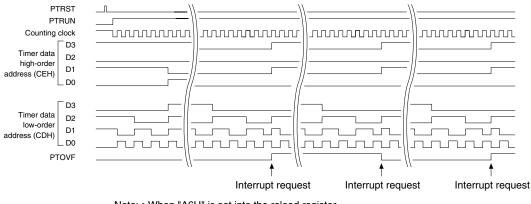

| 7.11 | 4.11.1 Configuration of programmable timer                                             |              |

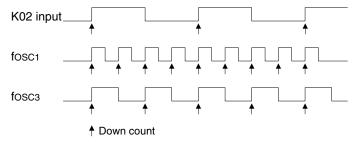

|      | 4.11.2 Input clock and prescaler                                                       |              |

|      | 4.11.3 Operation of programmable timer                                                 |              |

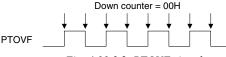

|      | 4.11.4 Interrupt function                                                              |              |

|      | 4.11.5 Control of programmable timer                                                   |              |

|      | 4.11.6 Programming notes                                                               | <i>I-</i> 67 |

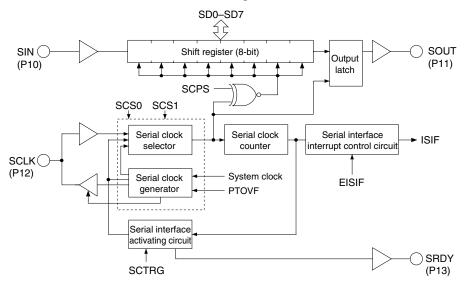

| 4.12 | Serial Interface (SIN, SOUT, SCLK, SRDY)                                               | <i>I-6</i> 8 |

|      | 4.12.1 Configuration of serial interface                                               |              |

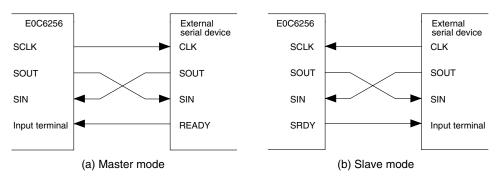

|      | 4.12.2 Master mode and slave mode of serial interface                                  |              |

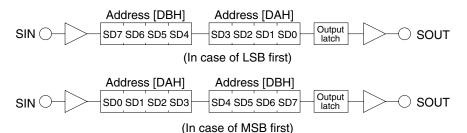

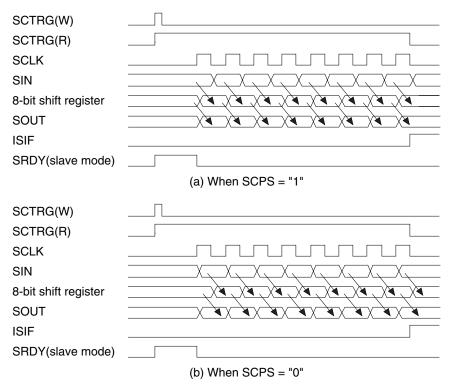

|      | 4.12.3 Data input/output and interrupt function                                        | <i>I-70</i>  |

|      | 4.12.4 Mask option                                                                     |              |

|      | 4.12.5 Control of serial interface                                                     |              |

|      | 4.12.6 Programming notes                                                               | <i>I-75</i>  |

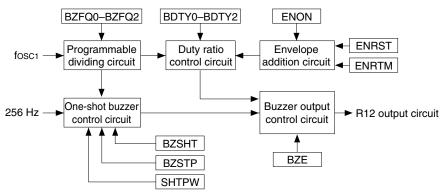

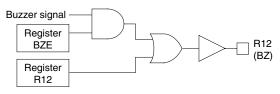

| 4.13 | Sound Generator                                                                        | <i>I-76</i>  |

|      | 4.13.1 Configuration of sound generator                                                |              |

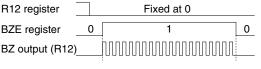

|      | 4.13.2 Control of buzzer output                                                        |              |

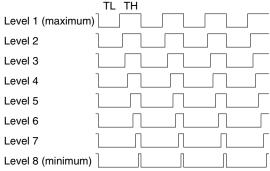

|      | 4.13.3 Setting of buzzer frequency and sound level                                     |              |

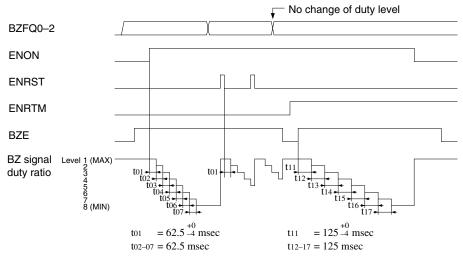

|      | 4.13.4 Digital envelope                                                                | <i>1-</i> 78 |

Hardware

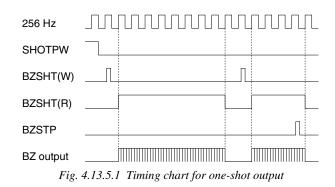

|           | 4.13.5 One-shot output                                                             | <i>I-</i> 78 |

|-----------|------------------------------------------------------------------------------------|--------------|

|           | 4.13.6 Control of sound generator                                                  |              |

|           | 4.13.7 Programming notes                                                           | <i>I-81</i>  |

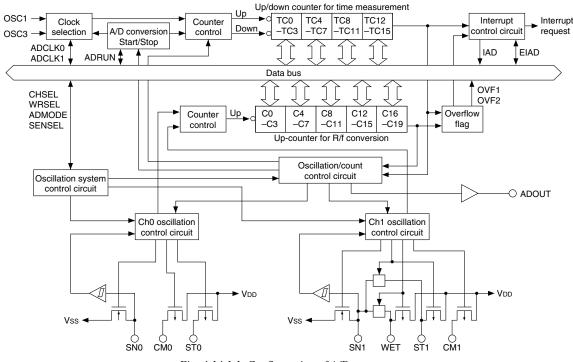

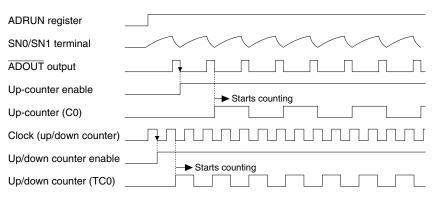

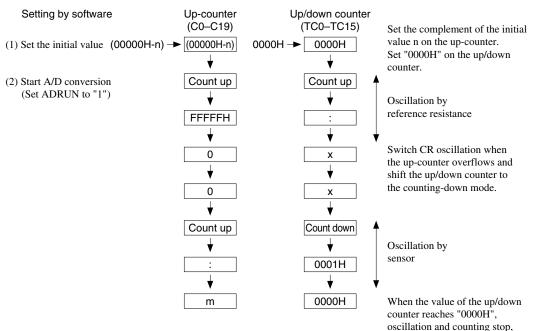

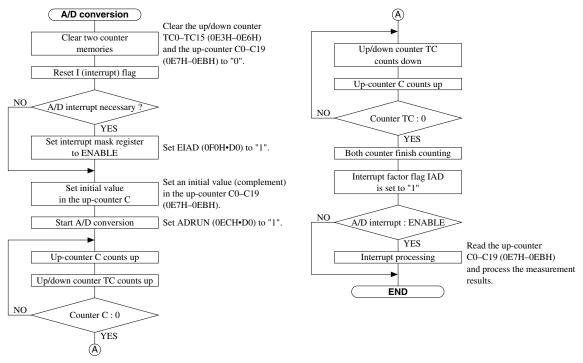

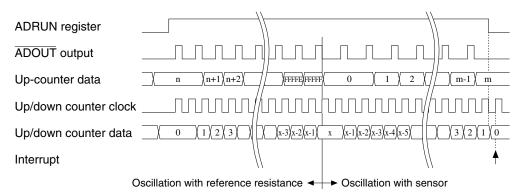

|           | 4.14 A/D Converter                                                                 | <i>I-82</i>  |

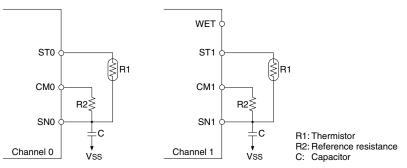

|           | 4.14.1 Configuration of A/D converter                                              |              |

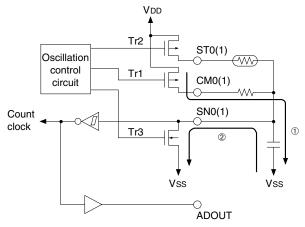

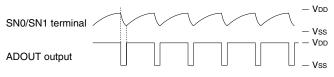

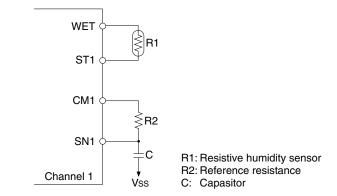

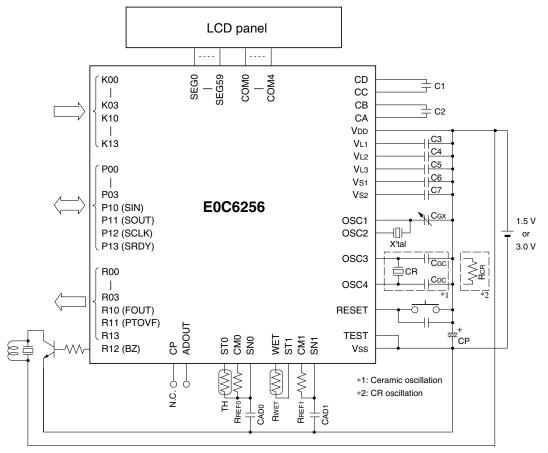

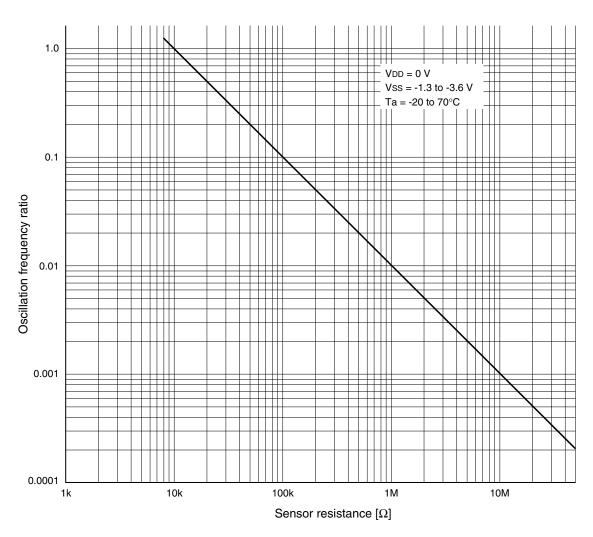

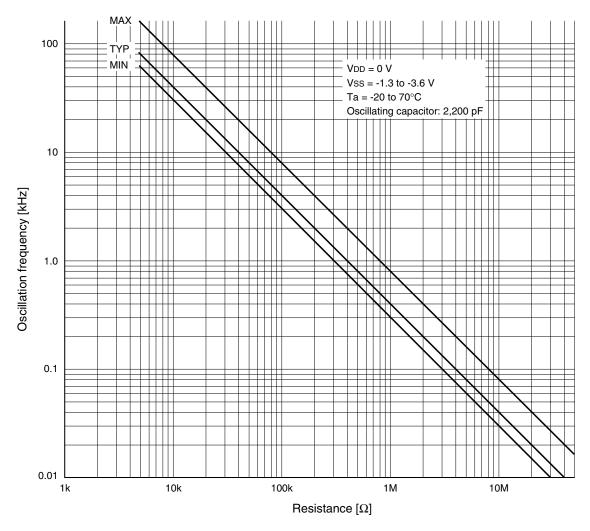

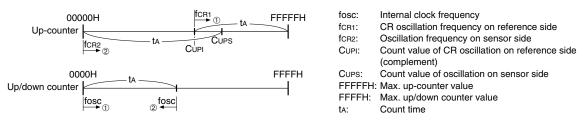

|           | 4.14.2 CR oscillation circuit                                                      |              |

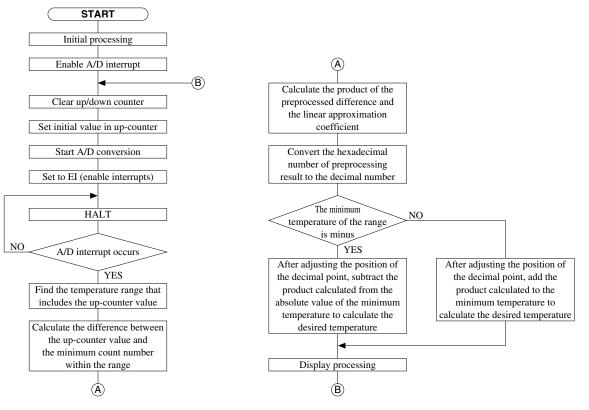

|           | 4.14.3 Operation of A/D conversion                                                 |              |

|           | 4.14.4 Interrupt function                                                          |              |

|           | 4.14.5 Control of A/D converter<br>4.14.6 Programming notes                        |              |

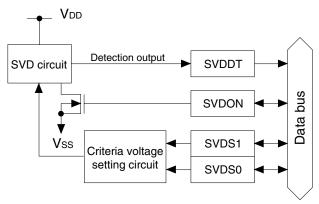

|           | 4.15 SVD (Supply Voltage Detection) Circuit                                        |              |

|           | 4.15 SVD (Supply Voltage Delection) Circuit<br>4.15.1 Configuration of SVD circuit |              |

|           | 4.15.2 Mask option                                                                 |              |

|           | 4.15.3 SVD operation                                                               |              |

|           | 4.15.4 Control of SVD circuit                                                      |              |

|           | 4.15.5 Programming notes                                                           | <i>I-96</i>  |

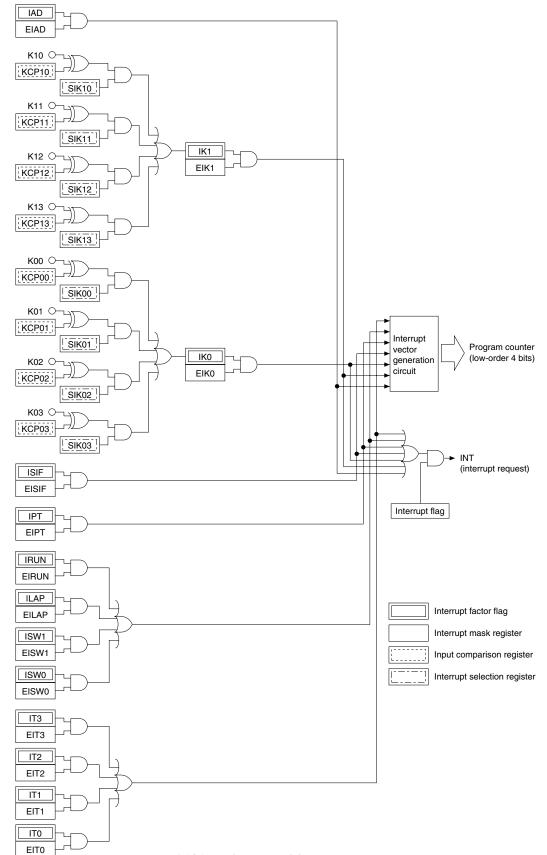

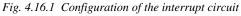

|           | 4.16 Interrupt and HALT                                                            | <i>I-97</i>  |

|           | 4.16.1 Interrupt factor                                                            |              |

|           | 4.16.2 Interrupt mask                                                              | <i>I-99</i>  |

|           | 4.16.3 Interrupt vector                                                            |              |

|           | 4.16.4 Control of interrupt                                                        |              |

|           | 4.16.5 Programming notes                                                           |              |

| CHAPTER 5 | Summary of Notes                                                                   | <i>I-103</i> |

|           | 5.1 Notes for Low Current Consumption                                              |              |

|           | 5.2 Summary of Notes by Function                                                   |              |

|           |                                                                                    |              |

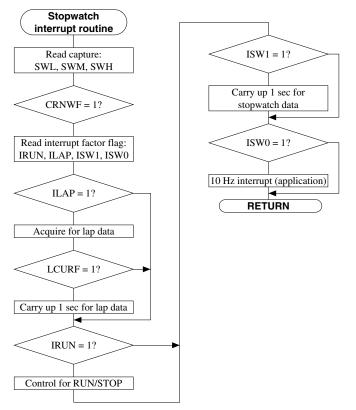

| CHAPTER O | DIAGRAM OF BASIC EXTERNAL CONNECTIONS                                              | I-108        |

| CHAPTER 7 | Electrical Characteristics                                                         | I-109        |

|           | 7.1 Absolute Maximum Rating                                                        | <i>I-109</i> |

|           | 7.2 Recommended Operating Conditions                                               |              |

|           | 7.3 DC Characteristics                                                             |              |

|           | 7.4 Analog Characteristics and Consumed Current                                    | I-111        |

|           | 7.5 Oscillation Characteristics                                                    |              |

|           | 7.6 Characteristics Curves                                                         | <i>I-113</i> |

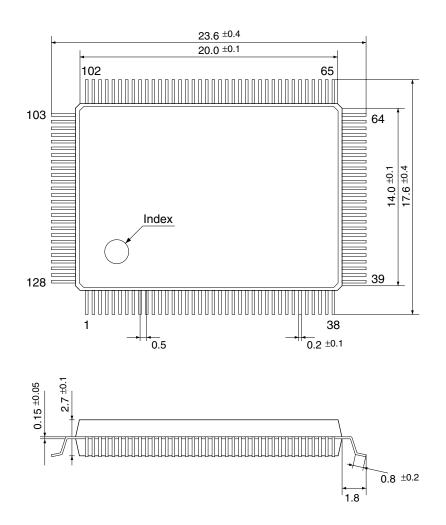

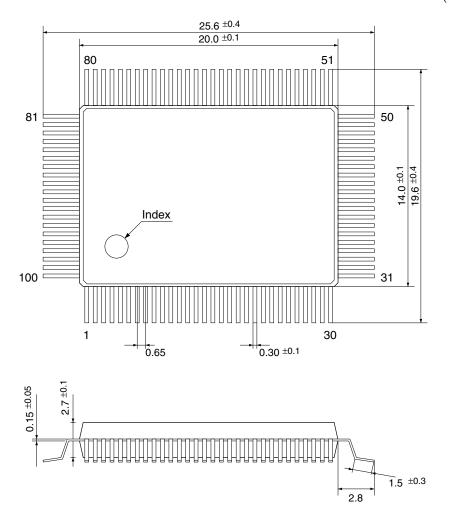

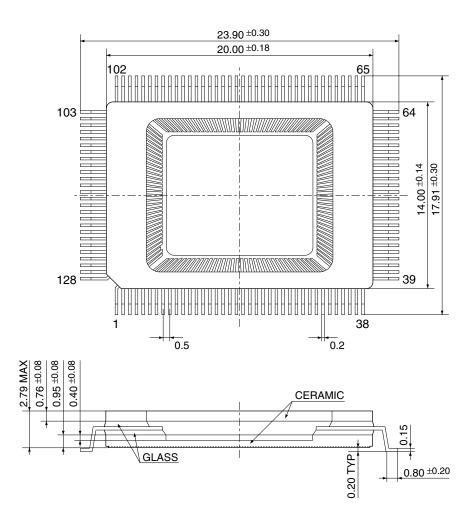

| CHADTED & | PACKAGE                                                                            | I-116        |

| CHAPIER O | PACKAGE                                                                            |              |

|           | 8.1 Plastic Package                                                                |              |

|           | 8.2 Ceramic Package for Test Samples                                               | <i>I-118</i> |

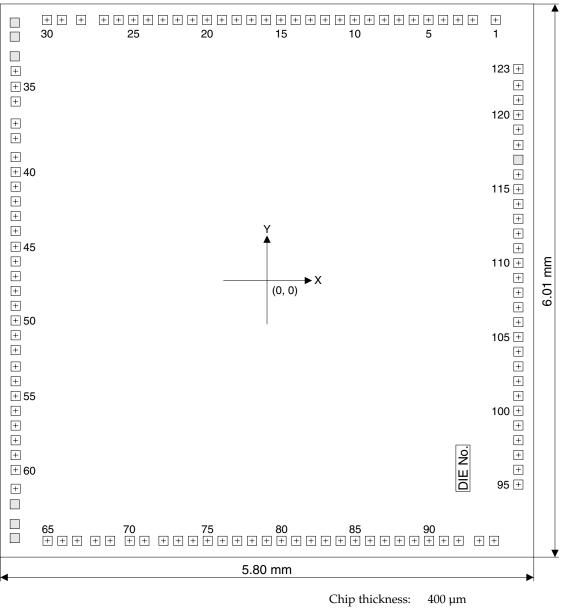

| CHAPTER 9 | PAD LAYOUT                                                                         | I-119        |

|           | 9.1 Diagram of Pad Layout                                                          | I-119        |

|           | 9.2 Pad Coordinates                                                                | <i>I-120</i> |

# CHAPTER 1 OVERVIEW

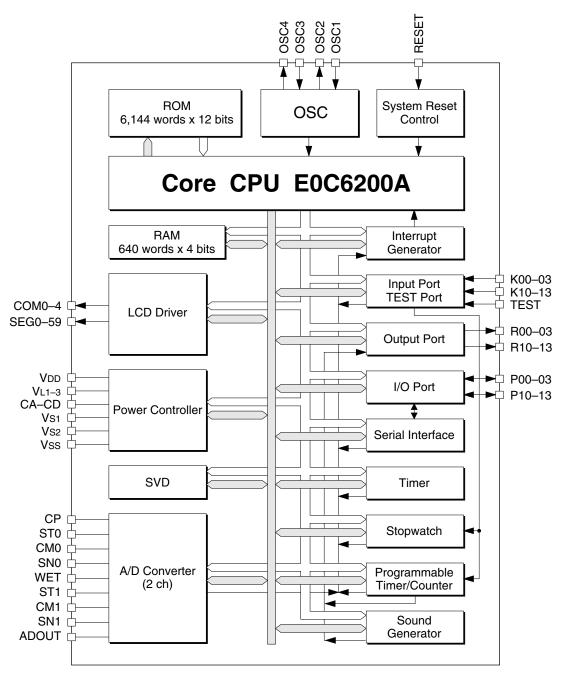

The E0C6256 is a single-chip microcomputer made up of the 4-bit core CPU E0C6200A, ROM (6,144 words, 12 bits to a word), RAM (640 words, 4 bits to a word), A/D converter (R/f conversion type), SVD circuit, LCD driver, serial interface, watchdog timer, programmable timer and time base counter.

It can realize system to measure temperature and humidity by the internal A/D converter and externally attached parts.

Because of its low-voltage operation and low power consumption, this series is ideal for a wide range of applications, and is especially suitable for battery-driven systems.

# 1.1 Features

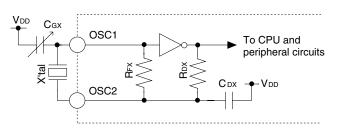

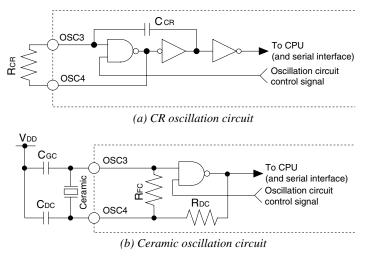

| OSC1 oscillation circuit Crystal oscill                                                   | ation circuit: 32.                                                | 768 kHz (Typ.)                                                                                                                                                                                                                                |

|-------------------------------------------------------------------------------------------|-------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OSC3 oscillation circuit CR or ceram                                                      | ic oscillation circ                                               | cuit (*1): 1 MHz (Typ.)                                                                                                                                                                                                                       |

| Instruction set 108 types                                                                 |                                                                   |                                                                                                                                                                                                                                               |

| Instruction execution time During opera<br>(differ depending on instruction) During opera |                                                                   |                                                                                                                                                                                                                                               |

| ROM capacity 6,144 words                                                                  | × 12 bits                                                         |                                                                                                                                                                                                                                               |

| RAM capacity 640 words $\times$                                                           | 4 bits                                                            |                                                                                                                                                                                                                                               |

| Input port 8 bits (pull de                                                                | own resistors ma                                                  | y be supplemented *1)                                                                                                                                                                                                                         |

| Output port 8 bits (BZ, F                                                                 | OUT and PTOVI                                                     | F outputs are possible *2)                                                                                                                                                                                                                    |

| I/O port 8 bits (4 bits                                                                   | are shared with s                                                 | serial input/output port *2)                                                                                                                                                                                                                  |

| Serial interface 1 port (8 bits                                                           | serial, synchrono                                                 | ous type clock)                                                                                                                                                                                                                               |

| A/D converter R/f (resistand                                                              | ce/frequency) cor                                                 | version type, 2 channels                                                                                                                                                                                                                      |

| LCD driver 60 segments<br>LCD drive vo                                                    |                                                                   | nmons (*2)<br>40 V, programmable (0.05 V unit)                                                                                                                                                                                                |

| Time base counter Clock timer: 1/1000 sec st                                              | opwatch timer:                                                    | 1 system<br>1 system                                                                                                                                                                                                                          |

| Programmable timer Built-in, 1 in                                                         | put $	imes$ 8 bits, with                                          | event counter function                                                                                                                                                                                                                        |

| Watchdog timer Built-in (It is                                                            | possible to exclu                                                 | ude *1)                                                                                                                                                                                                                                       |

| SVD circuit                                                                               |                                                                   | mable (for 1.5 V system, *1)<br>mable (for 3.0 V system, *1)                                                                                                                                                                                  |

| External interrupt Input port int                                                         | errupt:                                                           | 2 systems                                                                                                                                                                                                                                     |

| Internal interrupt Timer interru<br>Serial interfa<br>A/D converte                        | ce interrupt:                                                     | 3 systems<br>1 system<br>1 system                                                                                                                                                                                                             |

| Supply voltage 0.9-3.6 V (2.                                                              | 2-3.6 V when O                                                    | SC3 is used, 1.3–3.6 V when A/D converter is used)                                                                                                                                                                                            |

| Current consumption During HAL<br>(Typ.)<br>During opera                                  | T: 1.2 μA<br>650 nA<br>tion: 3.5 μA<br>2.0 μA<br>170 μA<br>220 μA | <ul> <li>(1.5 V, 32 kHz, normal mode)</li> <li>(3 V, 32 kHz, halver mode)</li> <li>(1.5 V, 32 kHz, normal mode)</li> <li>(3 V, 32 kHz, halver mode)</li> <li>(3 V, 1 MHz ceramic oscillation)</li> <li>(3 V, 1 MHz CR oscillation)</li> </ul> |

| Package QFP5-128pin                                                                       | n / QFP5-100pin                                                   | (plastic) or chip                                                                                                                                                                                                                             |

|                                                                                           |                                                                   |                                                                                                                                                                                                                                               |

\*1 May be selected with mask option.

\*2 May be selected with software.

## 1.2 Block Diagram

Fig. 1.2.1 Block diagram

# 1.3 Pin Layout Diagram

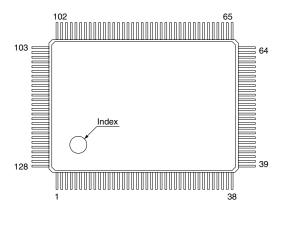

#### QFP5-128pin (plastic)

| Pin No. | Pin name |    | Pin name |    | Pin name | Pin No. | Pin name |

|---------|----------|----|----------|----|----------|---------|----------|

| 1       | N.C.     | 33 | OSC4     | 65 | SEG58    | 97      | Vss      |

| 2       | SEG27    | 34 | VS1      | 66 | SEG59    | 98      | N.C.     |

| 3       | SEG28    | 35 | SEG30    | 67 | N.C.     | 99      | N.C.     |

| 4       | SEG29    | 36 | SEG31    | 68 | N.C.     | 100     | N.C.     |

| 5       | COM0     | 37 | SEG32    | 69 | N.C.     | 101     | SEG0     |

| 6       | COM1     | 38 | N.C.     | 70 | VDD      | 102     | SEG1     |

| 7       | COM2     | 39 | N.C.     | 71 | RESET    | 103     | SEG2     |

| 8       | COM3     | 40 | SEG33    | 72 | TEST     | 104     | SEG3     |

| 9       | COM4     | 41 | SEG34    | 73 | K00      | 105     | SEG4     |

| 10      | CB       | 42 | SEG35    | 74 | K01      | 106     | SEG5     |

| 11      | CA       | 43 | SEG36    | 75 | K02      | 107     | SEG6     |

| 12      | VL3      | 44 | SEG37    | 76 | K03      | 108     | SEG7     |

| 13      | VL2      | 45 | SEG38    | 77 | K10      | 109     | SEG8     |

| 14      | VL1      | 46 | SEG39    | 78 | K11      | 110     | SEG9     |

| 15      | CC       | 47 | SEG40    | 79 | K12      | 111     | SEG10    |

| 16      | CD       | 48 | SEG41    | 80 | K13      | 112     | SEG11    |

| 17      | VS2      | 49 | SEG42    | 81 | R00      | 113     | SEG12    |

| 18      | Vss      | 50 | SEG43    | 82 | R01      | 114     | SEG13    |

| 19      | ADOUT    | 51 | SEG44    | 83 | R02      | 115     | SEG14    |

| 20      | SN1      | 52 | SEG45    | 84 | R03      | 116     | SEG15    |

| 21      | WET      | 53 | SEG46    | 85 | R10      | 117     | SEG16    |

| 22      | ST1      | 54 | SEG47    | 86 | R11      | 118     | SEG17    |

| 23      | CM1      | 55 | SEG48    | 87 | R12      | 119     | SEG18    |

| 24      | SN0      | 56 | SEG49    | 88 | R13      | 120     | SEG19    |

| 25      | CM0      | 57 | SEG50    | 89 | P00      | 121     | SEG20    |

| 26      | ST0      | 58 | SEG51    | 90 | P01      | 122     | SEG21    |

| 27      | СР       | 59 | SEG52    | 91 | P02      | 123     | SEG22    |

| 28      | VDD      | 60 | SEG53    | 92 | P03      | 124     | SEG23    |

| 29      | N.C.     | 61 | SEG54    | 93 | P10      | 125     | SEG24    |

| 30      | OSC1     | 62 | SEG55    | 94 | P11      | 126     | SEG25    |

| 31      | OSC2     | 63 | SEG56    | 95 | P12      | 127     | SEG26    |

| 32      | OSC3     | 64 | SEG57    | 96 | P13      | 128     | N.C.     |

Fig. 1.3.1 Pin layout diagram (QFP5-128pin)

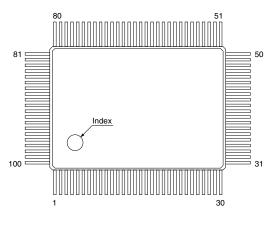

#### QFP5-100pin (plastic)

| Pin No. | Pin name |

|---------|----------|---------|----------|---------|----------|---------|----------|

| 1       | SEG29    | 26      | OSC2     | 51      | SEG59    | 76      | P11      |

| 2       | COM0     | 27      | OSC3     | 52      | VDD      | 77      | P12      |

| 3       | COM1     | 28      | OSC4     | 53      | RESET    | 78      | P13      |

| 4       | COM2     | 29      | VS1      | 54      | TEST     | 79      | Vss      |

| 5       | COM3     | 30      | SEG30    | 55      | K00      | 80      | SEG0     |

| 6       | COM4     | 31      | SEG31    | 56      | K01      | 81      | SEG1     |

| 7       | CB       | 32      | SEG32    | 57      | K02      | 82      | SEG2     |

| 8       | CA       | 33      | SEG34    | 58      | K03      | 83      | SEG4     |

| 9       | VL3      | 34      | SEG36    | 59      | K10      | 84      | SEG6     |

| 10      | VL2      | 35      | SEG38    | 60      | K11      | 85      | SEG8     |

| 11      | VL1      | 36      | SEG40    | 61      | K12      | 86      | SEG10    |

| 12      | CC       | 37      | SEG41    | 62      | K13      | 87      | SEG12    |

| 13      | CD       | 38      | SEG42    | 63      | R00      | 88      | SEG13    |

| 14      | VS2      | 39      | SEG43    | 64      | R01      | 89      | SEG14    |

| 15      | ADOUT    | 40      | SEG44    | 65      | R02      | 90      | SEG15    |

| 16      | SN1      | 41      | SEG45    | 66      | R03      | 91      | SEG16    |

| 17      | WET      | 42      | SEG46    | 67      | R10      | 92      | SEG17    |

| 18      | ST1      | 43      | SEG47    | 68      | R11      | 93      | SEG18    |

| 19      | CM1      | 44      | SEG48    | 69      | R12      | 94      | SEG19    |

| 20      | SN0      | 45      | SEG49    | 70      | R13      | 95      | SEG21    |

| 21      | CM0      | 46      | SEG51    | 71      | P00      | 96      | SEG23    |

| 22      | ST0      | 47      | SEG53    | 72      | P01      | 97      | SEG25    |

| 23      | СР       | 48      | SEG55    | 73      | P02      | 98      | SEG26    |

| 24      | VDD      | 49      | SEG57    | 74      | P03      | 99      | SEG27    |

| 25      | OSC1     | 50      | SEG58    | 75      | P10      | 100     | SEG28    |

Fig. 1.3.2 Pin layout diagram (QFP5-100pin)

# 1.4 Pin Description

| Pin name    | Pin No.      |             |     | Function                                                                      |  |

|-------------|--------------|-------------|-----|-------------------------------------------------------------------------------|--|

| Tinname     | QFP5-128pin  | QFP5-100pin | Out |                                                                               |  |

| VDD         | 28, 70       | 24, 52      | (I) | Power supply pin (+)                                                          |  |

| Vss         | 18, 97       | 79          | (I) | Power supply pin (-)                                                          |  |

| VS1         | 34           | 29          | 0   | Oscillation and internal logic system regulated voltage output pin            |  |

| VS2         | 17           | 14          | 0   | Supply voltage doubler/halver output pin                                      |  |

| VL1         | 14           | 11          | 0   | LCD system regulated voltage output pin                                       |  |

| VL2         | 13           | 10          | 0   | LCD system booster voltage output pin (VL1 $\times$ 2)                        |  |

| VL3         | 12           | 9           | 0   | LCD system booster voltage output pin (VL1 $\times$ 3)                        |  |

| CA, CB      | 11, 10       | 8, 7        | -   | LCD system voltage booster capacitor connecting pin                           |  |

| CC, CD      | 15, 16       | 12, 13      | -   | Supply voltage doubler/halver capacitor connecting pin                        |  |

| OSC1        | 30           | 25          | I   | Crystal oscillation input pin                                                 |  |

| OSC2        | 31           | 26          | 0   | Crystal oscillation output pin                                                |  |

| OSC3        | 32           | 27          | Ι   | Ceramic or CR oscillation input pin (selected by mask option)                 |  |

| OSC4        | 33           | 28          | 0   | Ceramic or CR oscillation output pin (selected by mask option)                |  |

| K00-K03     | 73–76        | 55–58       | Ι   | Input port pin                                                                |  |

| K10-K13     | 77–80        | 59–62       | Ι   | Input port pin                                                                |  |

| P00-P03     | 89–92        | 71–74       | I/O | I/O port pin                                                                  |  |

| P10-P13     | 93–96        | 75–78       | I/O | I/O port pin (switching to SIN, SOUT, SCLK, SRDY pin is possible by software) |  |

| R00-R03     | 81-84        | 63–66       | 0   | Output port pin                                                               |  |

| R10-R13     | 85-88        | 67–70       | 0   | Output port pin (switching to BZ, PTOVF, FOUT output is possible by software) |  |

| COM0–COM4   | 5–9          | 2–6         | 0   | LCD common output pin (1/5, 1/4, 1/3, 1/2 duty, programmable)                 |  |

| SEG0-SEG59* | 101–127, 2–4 | 80-100      | 0   | LCD segment output pin (DC output may be selected by mask option)             |  |

|             | 35–37, 40–66 | 1, 30–51    |     |                                                                               |  |

| СР          | 27           | 23          | 0   | A/D converter test output pin                                                 |  |

| ST0         | 26           | 22          | 0   | A/D converter CH0 CR oscillation output pin                                   |  |

| CM0         | 25           | 21          | 0   | A/D converter CH0 CR oscillation output pin                                   |  |

| SN0         | 24           | 20          | Ι   | A/D converter CH0 CR oscillation input pin                                    |  |

| WET         | 21           | 17          | 0   | A/D converter CH1 CR oscillation output pin                                   |  |

| ST1         | 22           | 18          | 0   | A/D converter CH1 CR oscillation output pin                                   |  |

| CM1         | 23           | 19          | 0   | A/D converter CH1 CR oscillation output pin                                   |  |

| SN1         | 20           | 16          | Ι   | A/D converter CH1 CR oscillation input pin                                    |  |

| ADOUT       | 19           | 15          | 0   | A/D converter oscillation frequency output pin                                |  |

| RESET       | 71           | 53          | Ι   | Initial reset input pin                                                       |  |

| TEST        | 72           | 54          | I   | Testing input pin                                                             |  |

Table 1.4.1 Pin description

\* The following SEG pins are not included in the QFP5-100pin package, so they cannot be used.

SEG3, SEG5, SEG7, SEG9, SEG11, SEG20, SEG22, SEG24, SEG33, SEG35, SEG37, SEG39, SEG50, SEG52, SEG54, SEG56

# CHAPTER 2 POWER SUPPLY AND INITIAL RESET

# 2.1 Power Supply

The E0C6256 operating power voltage is as follows:

0.9 V to 3.6 V

- Note: When using a supply voltage within the range of 0.9 to 1.4 V, it is necessary to use software to control it.

- When using the OSC3 oscillation circuit, a supply voltage within the range of 2.2 to 3.6 V is required.

- When using the A/D converter, a supply voltage within the range of 1.3 to 3.6 V is required.

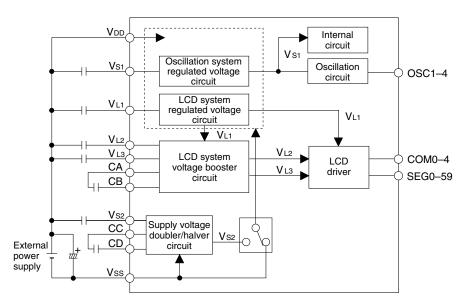

The E0C6256 operates when a single power supply within the above range is applied between VDD and Vss. The IC itself can generate the voltage necessary for the internal circuits with the following built-in power supply circuit.

| Circuit                                       | Power supply circuit                         | Output voltage |

|-----------------------------------------------|----------------------------------------------|----------------|

| Oscillation and internal circuits             | Oscillation system regulated voltage circuit | Vs1            |

| LCD driver                                    | LCD system regulated voltage circuit         | VL1-VL3        |

| Oscillation system regulated voltage circuit, | Supply voltage doubler/halver circuit        | Vs2            |

| LCD system regulated voltage circuit          |                                              |                |

- *Note:* External loads cannot be driven by the regulated voltage, voltage booster and voltage doubler/ halver circuits' output voltages.

- See Chapter 7, "ELECTRICAL CHARACTERISTICS" for voltage values.

Fig. 2.1.1 Configuration of power supply

#### **CHAPTER 2: POWER SUPPLY AND INITIAL RESET**

#### 2.1.1 Supply voltage doubler/halver and operating mode

The power supply circuit has the supply voltage doubler/halver built-in. The supply voltage doubler/halver doubles or halves the voltage (VSS) supplied from outside, and generates the VS2 voltage for the internal power supply circuits (oscillation system regulated voltage circuit and LCD system regulated voltage circuit). Anyone of the following three operating modes can be set according to the status of the supply voltage doubler/halver, and switching between them is done by the software.

#### (1) Doubler mode

The E0C6256 operates with 0.9 to 3.6 V supply voltage. However, a minimum 1.4 V supply voltage is needed for the internal powr supply circuit of oscillation and LCD systems. Therefore, when operating with the supply voltage within the range of 0.9 to 1.4 V, it is necessary to double the supply voltage using the supply voltage doubler/halver. Operating mode at this time is the doubler mode. The internal power supply circuit operates by the Vs2 voltage (1.8 to 2.8 V) output from the supply voltage doubler/halver.

When the supply voltage is more than 1.4 V, do not set in this mode because doubling voltage increases current consumption.

Note: The OSC3 oscillation circuit cannot be used in this mode even when 2.2 V or more voltage is generated by doubling. Turning the OSC3 oscillation circuit ON in this mode may cause malfunction.

#### (2) Normal mode

In this mode, the internal power supply circuit directly operates by the supply voltage Vss within the range of 1.3 to 3.6 V without the supply voltage doubler/halver. The OSC3 oscillation circuit can be used when a 2.2 V or more voltage is supplied. At initial reset, this mode is set.

#### (3) Halver mode

The halver mode can be set when a 2.55 to 3.6 V supply voltage is used to operate. This mode halves the supply voltage using the supply voltage doubler/halver, and operates the internal power supply circuit using its output voltage Vs2. Therefore, current consumption can be reduced to about half of the normal mode.

Note: The OSC3 oscillation circuit cannot be used in this mode even when 2.2 V or more voltage is generated by halving. Turning the OSC3 oscillation circuit ON in this mode may cause malfunction.

See Section 4.2, "Power Supply and Operating Mode Settings", for the control of the operating mode.

#### 2.1.2 Voltage <VS1> for oscillation circuit and internal circuits

VS1 is the voltage for the oscillation circuit and the internal circuits, and is generated by the oscillation system regulated voltage circuit for stabilizing the oscillation.

Making VDD the standard (GND level), the oscillation system regulated voltage circuit generates VS1 from the supply voltage that is input from the VDD–VSS terminals. However, when the supply voltage doubler/halver is used, VS1 is generated from the voltage between the VDD and VS2 terminals.

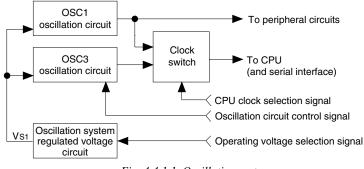

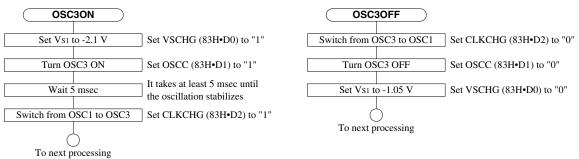

The E0C6256 is designed with twin clock specification; it has two types of oscillation circuits OSC1 and OSC3 built-in. Use OSC1 clock for normal operation, and switch it to OSC3 by the software when high-speed operation is necessary. When switching the clock, the operating voltage VS1 must be switched by the software to stabilize the operation of the oscillation circuit and internal circuits. The VS1 voltage must be set to -1.05 V when operating with the OSC1 clock or to -2.10 V when operating with the OSC3 clock. See Section 4.4, "Oscillation Circuit", for the VS1 switching procedure.

#### 2.1.3 Voltage <VL1, VL2 and VL3> for LCD driving

VL1, VL2 and VL3 are the voltages for LCD drive, and are generated by the LCD system regulated voltage circuit and the LCD system voltage booster circuit to stabilize the display quality.

VL1 is generated by the LCD system regulated voltage circuit with VDD as the standard from the supply voltage input from the VDD–VSS terminals. However, when the supply voltage doubler/halver is used, VL1 is generated from the voltage between the VDD and VS2 terminals.

The VL1 voltage can be adjusted within the range from -1.05 to -1.40 V in unit of 0.05 V to match the LCD panel characteristics by the software. To generate VL1, VSS (VS2 when the supply voltage doubler/halver is used) voltage (VDD standard) must be lower than VL1 - 0.2 V.

Vss/Vs₂ (absolute value) ≥ VL1 (absolute value) + 0.2 V

See Section 4.2, "Power Supply and Operation Mode Settings", for the VL1 setting. VL2 and VL3 are respectively double and triple obtained from the LCD system voltage booster circuit.

## 2.2 Initial Reset

To initialize the E0C6256 circuits, initial reset must be executed. There are four ways of doing this.

- (1) External initial reset by the RESET terminal

- (2) External initial reset by simultaneous high input to terminals K00-K03 (mask option setting)

- (3) Initial reset by the oscillation detection circuit

- (4) Initial reset by the watchdog timer (mask option setting)

Be sure to use reset functions (1) or (2) when turning the power on and be sure to initialize securely. In normal operation, the circuit may be initialized by any of the above four types.

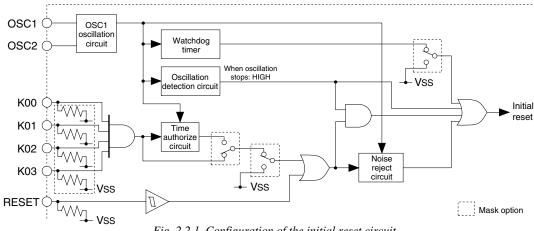

Figure 2.2.1 shows the configuration of the initial reset circuit.

Fig. 2.2.1 Configuration of the initial reset circuit

#### 2.2.1 Reset terminal (RESET)

Initial reset can be executed externally by setting the reset terminal to a high level. However, be sure to observe the following precautions, because the RESET signal passes through the noise reject circuit. When the reset terminal is used for initial resetting during operation, a pulse (high level) of 0.4 msec or less is considered to be noise by the noise reject circuit. Maintain a high level of 1.5 msec (when the oscillation frequency fOSC1 = 32 kHz) to securely perform the initial reset. When the reset terminal goes low, the CPU begins to operate.

Since the noise reject circuit does not operate when oscillation is stopped, the noise reject circuit is bypassed until it starts oscillation. For this reason, be sure to maintain a high level the reset input in the oscillation stopped status, such as at power-on, until starting oscillation.

#### 2.2.2 Simultaneous high input to terminals K00–K03

Another way of executing initial reset externally is to input a high signal simultaneously to the input ports (K00-K03) selected with the mask option.

Since this initial reset also passes through the same noise reject circuit as the reset terminal, you should maintain the specified input port terminal at high level for 1.5 msec (when oscillation frequency fOSC1 = 32 kHz) or more during operation and until it begins oscillation at times such as when turning the power on. Table 2.2.2.1 shows the combinations of input ports (K00–K03) that can be selected with the mask option.

Table 2.2.2.1 Combinations of input ports

|   |                 | ı Wh |

|---|-----------------|------|

| 1 | Not use         | sele |

| 2 | K00*K01*K02*K03 | fou  |

| 3 | K00*K01*K02     | 100  |

| 3 | K00*K01*K02     | rese |

| 4 | K00*K01         | sele |

nen, for instance, mask option 2 (K00\*K01\*K02\*K03) is ected, initial reset is executed when the signals input to the r ports K00–K03 are all high at the same time. The initial et is done, even when a key entry including a combination of ected input ports is made.

Further, the time authorize circuit can be selected with the mask option. The time authorize circuit performs initial reset, when the input time of the simultaneous high input is authorized and found to be the same or more than the defined time (1 to 2 sec).

If you use this function, make sure that the specified ports do not go high at the same time during ordinary operation.

#### 2.2.3 Oscillation detection circuit

The oscillation detection circuit outputs the initial reset signal at power-on until the oscillation circuit starts oscillating, or when the oscillation circuit stops oscillating for some reason.

However, this circuit may not operate properly depending on the power-on procedure. Consequently, use a simultaneous high input of the input ports (K00–K03) or reset terminal for the initial reset at power-on and you should not execute it by this function alone.

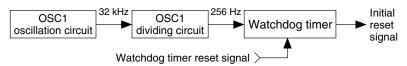

#### 2.2.4 Watchdog timer

If the CPU runs away for some reason, the watchdog timer will detect this situation and output an initial reset signal. See Section 4.3, "Resetting Watchdog Timer", for details. As with the oscillation detection circuit, you should not do an initial reset at power-on using this function.

#### 2.2.5 Internal register at initial resetting

Initial reset initializes the CPU as shown in the table below.

| CPU core                   |        |                |               |  |  |

|----------------------------|--------|----------------|---------------|--|--|

| Name                       | Symbol | Number of bits | Setting value |  |  |

| Program counter step       | PCS    | 8              | 00H           |  |  |

| Program counter page       | PCP    | 4              | 1H            |  |  |

| Program counter bank       | PCB    | 1              | 0             |  |  |

| New page pointer           | NPP    | 4              | 1H            |  |  |

| New bank pointer           | NBP    | 1              | 0             |  |  |

| Stack pointer              | SP     | 8              | Undefined     |  |  |

| Index register IX          | IX     | 11             | Undefined     |  |  |

| Index register IY          | IY     | 11             | Undefined     |  |  |

| Register pointer           | RP     | 4              | Undefined     |  |  |

| General-purpose register A | А      | 4              | Undefined     |  |  |

| General-purpose register B | В      | 4              | Undefined     |  |  |

| Interrupt flag             | Ι      | 1              | 0             |  |  |

| Decimal flag               | D      | 1              | 0             |  |  |

| Zero flag                  | Z      | 1              | Undefined     |  |  |

| Carry flag                 | C      | 1              | Undefined     |  |  |

| Peripheral circuits               |   |           |  |  |  |  |

|-----------------------------------|---|-----------|--|--|--|--|

| Name Number of bits Setting value |   |           |  |  |  |  |

| RAM                               | 4 | Undefined |  |  |  |  |

| Display memory                    | 4 | Undefined |  |  |  |  |

| Other peripheral circuits         | — | *         |  |  |  |  |

\* See Section 4.1, "Memory Map".

# 2.3 Test Terminals (TEST, CP)

These terminals are used at the time of the factory inspection of the IC. During normal operation, connect the TEST to Vss, and do not connect anything to the CP terminal.

# CHAPTER 3 CPU, ROM, RAM

# 3.1 CPU

The E0C6256 employs the 4-bit core CPU E0C6200A for the CPU, so that register configuration, instructions and so forth are virtually identical to those in other family processors using the E0C6200A. Refer to "E0C6200/6200A Core CPU Manual" for details about the E0C6200A. Note the following points with regard to the E0C6256:

- (1) The SLEEP operation is not assumed, so the SLP instruction cannot be used.

- (2) RAM is set up to five pages, so only the three low-order bits are valid for the page portion (XP, YP) of the index register that specifies addresses. (The one high-order bit is ignored.)

# 3.2 ROM

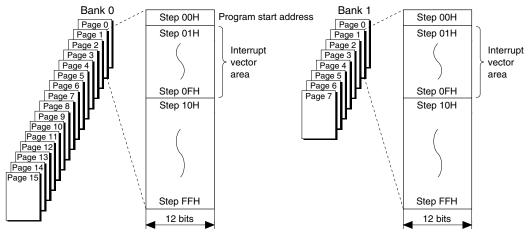

The built-in ROM, a mask ROM for loading the program, has a capacity of 6,144 steps, 12 bits each. The program area is divided into two banks. Bank 0 is configured of 16 pages (0–15) with 256 steps each (00H–FFH), and bank 1 of 8 pages (0–7) with 256 steps each. After initial reset, the program beginning address is bank 0, page 1, step 00H. The interrupt vector is allocated to each page 1, steps 01H–0FH.

Fig. 3.2.1 ROM configuration

# 3.3 RAM

The RAM, a data memory storing a variety of data, has a capacity of 640 words, each of four bits. When programming, keep the following points in mind.

- (1) Part of the data memory can be used as stack area when subroutine calls and saving registers, so be careful not to overlap the data area and stack area.

- (2) Subroutine calls and interrupts take up three words of the stack area.

- (3) The data memory 000H–00FH is for the register pointers (RP), and is the addressable memory register area.

# CHAPTER 4 PERIPHERAL CIRCUITS AND OPERATION

Peripheral circuits (timer, I/O, and so on) of the E0C6256 are memory mapped, and interfaced with the CPU. Thus, all the peripheral circuits can be controlled by using the memory operation command to access the I/O memory in the memory map.

The following sections describe how the peripheral circuits operation.

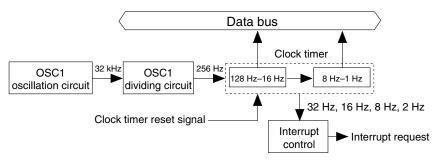

# 4.1 Memory Map

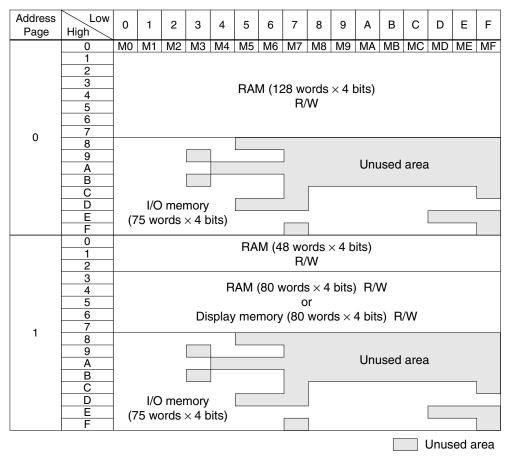

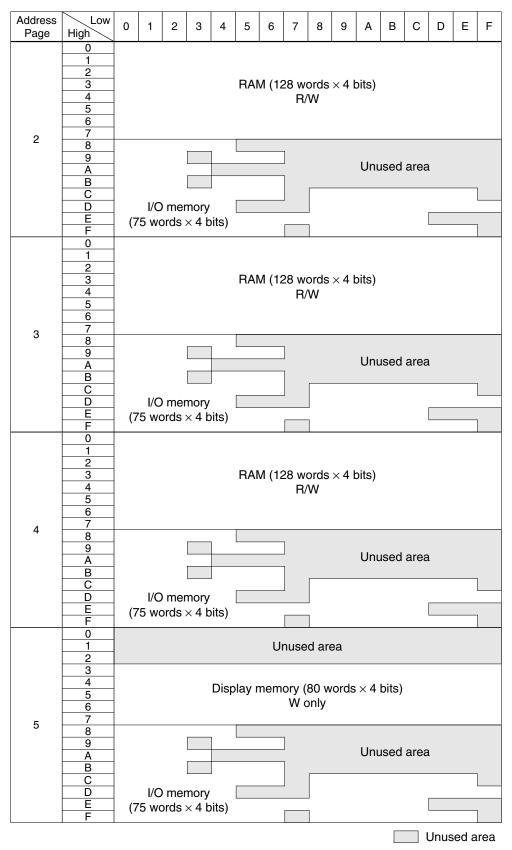

Data memory of the E0C6256 has an address space of 795 words (715 words when the display memory is assigned in page 1), of which 80 words are allocated to display memory and 75 words to I/O memory. Figures 4.1.1(a) and (b) present the overall memory maps of the E0C6256, and Tables 4.1.1(a)–(h) the peripheral circuits' (I/O space) memory maps.

In the E0C6256 the same I/O memory has been laid out for each page 80H–FFH. As a result, the I/O memory can be accessed without changing over the data memory page. The same result is obtained for I/O memory changes and for readable/writable address references, no matter on what page it is done.

Note: • The display memory area can be assigned to 130H–17FH or 530H–57FH by software.

When page 1 (130H–17FH) is selected: read/write is enabled. When page 5 (530H–57FH) is selected: write only is enabled.

If page 1 is selected, RAM (80 words) is used as the display memory area.

• Memory is not mounted in unused area within the memory map and in memory area not indicated in this chapter. For this reason, normal operation cannot be assured for programs that have been prepared with access to these areas.

Fig. 4.1.1(a) Memory map

Fig. 4.1.1(b) Memory map

| Address |     | Regi     | ister    |          |        |         |       |        | Comment                                            |

|---------|-----|----------|----------|----------|--------|---------|-------|--------|----------------------------------------------------|

| *7      | D3  | D2       | D1       | D0       | Name   | Init *1 | 1     | 0      | Comment                                            |

|         | 0   | 0        | SVDS1    | SVDS0    | 0 *5   | - *2    |       |        | Unused                                             |

| 80H     | 0   | 0        | 34031    | 31030    | 0 *5   | - *2    |       |        | Unused                                             |

| 0011    |     | R        | B        | w        | SVDS1  | 0       |       |        | SVD criteria voltage setting (1.5 V/3.0 V)         |

|         |     |          | 10       | **       | SVDS0  | 0       |       |        | □ 0: 1.05/2.30, 1: 1.20/2.45, 2 & 3: 1.35/2.60 (V) |

|         | 0   | 0        | SVDDT    | SVDON    | 0 *5   | - *2    |       |        | Unused                                             |

| 81H     | •   | Ŭ        | 01001    | - OVDON  | 0 *5   | - *2    |       |        | Unused                                             |

| 0111    |     | B        |          | R/W      | SVDDT  | 0       | Low   | Normal | Supply voltage detection data                      |

|         |     |          |          | 10,44    | SVDON  | 0       | On    | Off    | SVD circuit On/Off                                 |

|         | 0   | VSEL     | HLON     | DBON     | 0 *5   | - *2    |       |        | Unused                                             |

| 82H     | v   | VOLL     | TIEON    | DDON     | VSEL   | 0       | VS2   | Vss    | Voltage regulator power source selection           |

| 0211    | В   |          | R/W      | R/W      |        | 0       | On    | Off    | Halver On/Off                                      |

|         |     |          |          |          | DBON   | 0       | On    | Off    | Doubler On/Off                                     |

|         | 0   | CLKCHG   | oscc     | VSCHG    | 0 *5   | - *2    |       |        | Unused                                             |

| 83H     | Ŭ   | OLIVOITO | 0000     | Voona    | CLKCHG | 0       | OSC3  | OSC1   | CPU clock selection                                |

|         | В   |          | R/W      |          | OSCC   | 0       | On    | Off    | OSC3 oscillation On/Off                            |

|         |     |          | 1000     |          | VSCHG  | 0       | -2.1V | -1.05V | VS1 output voltage change                          |

|         | 0 1 |          | VLCHG1   | VLCHG0   | 0 *5   | - *2    |       |        | Unused                                             |

| 84H     |     | VEONAL   | v Loniar | V LONIGO | VLCHG2 | 0       |       |        | VL1 output voltage change                          |

|         | В   |          | R/W      |          | VLCHG1 | 0       |       |        | 0: 1.05, 1: 1.10, 2: 1.15, 3: 1.20,                |

|         |     |          |          |          | VLCHG0 | 0       |       |        | 4: 1.25, 5: 1.30, 6: 1.35, 7: 1.40 (V)             |

*Table 4.1.1(a) I/O memory map (80H–84H)*

| Address |           | Reg    | ister        |       |       |         |        |                                     | Comment                             |

|---------|-----------|--------|--------------|-------|-------|---------|--------|-------------------------------------|-------------------------------------|

| *7      | D3        | D2     | D1           | D0    | Name  | Init *1 | 1      | 0                                   | Comment                             |

|         | SIK03     | SIK02  | SIK01        | SIK00 | SIK03 | 0       | Enable | Disable                             | Interrupt selection register (K03)  |

| 0011    | 31103     | SIKUZ  | SIKUI        | SIKUU | SIK02 | 0       | Enable | Disable                             | Interrupt selection register (K02)  |

| 90H     |           | R/     |              |       | SIK01 | 0       | Enable | Disable                             | Interrupt selection register (K01)  |

|         |           | Π/     | vv           |       | SIK00 | 0       | Enable | Disable                             | Interrupt selection register (K00)  |

|         | K03       | K02    | K01          | K00   | K03   | - *2    | High   | Low                                 |                                     |

| 91H     | K03       | NU2    | RUT          | NUU   | K02   | - *2    | High   | Low                                 | Input post (K00, K02)               |

| 910     |           | r      | 3            |       | K01   | - *2    | High   | Low                                 | Input port (K00–K03)                |

|         |           | Г      | ר            |       | K00   | - *2    | High   | Low                                 |                                     |

|         | KCP03     | KCP02  | KCP01        | KCP00 | KCP03 | 0       | Ţ      |                                     |                                     |

| 0011    | 92H       |        | NOF 00       | KCP02 | 0     | Ţ       | Ŀ      | Input comparison register (K00–K03) |                                     |

| 92⊓     |           |        | <b>\</b>     |       | KCP01 | 0       | Ţ      | Ŀ                                   | Input comparison register (K00–K03) |

|         |           | Π/     | vv           |       | KCP00 | 0       | Ţ      | ſ                                   |                                     |

|         | SIK13     | SIK12  | SIK11        | SIK10 | SIK13 | 0       | Enable | Disable                             | Interrupt selection register (K13)  |

| 94H     | 51115     | SIK12  | SIXTI        | SIKTU | SIK12 | 0       | Enable | Disable                             | Interrupt selection register (K12)  |

| 940     |           | R/     |              |       | SIK11 | 0       | Enable | Disable                             | Interrupt selection register (K11)  |

|         |           | Π/     | vv           |       | SIK10 | 0       | Enable | Disable                             | Interrupt selection register (K10)  |

|         | K13       | K12    | K11          | K10   | K13   | - *2    | High   | Low                                 | 7                                   |

| 95H     | KI3       | N12    | K11          | KIU   | K12   | - *2    | High   | Low                                 | Input port (K10–K13)                |

| 9011    |           | F      | 2            |       | K11   | - *2    | High   | Low                                 | input port (K10–K13)                |

|         |           | ſ      | 1            |       | K10   | - *2    | High   | Low                                 |                                     |

|         | KCP13 KCP |        | KCP11        | KCP10 | KCP13 | 0       | Ţ      | 1                                   |                                     |

| 96H     | 101 13    | 101 12 |              | KCP10 | KCP12 | 0       | ٦.     | ſ                                   | Input comparison register (K10–K13) |

| 900     |           | B/     | \ <b>\</b> / |       | KCP11 | 0       | Ţ      | Ŀ                                   | input comparison register (K10–K13) |

|         |           | n/     | **           |       | KCP10 | 0       | Ţ      |                                     |                                     |

*Table 4.1.1(b) I/O memory map (90H–96H)*

\*1 Initial value at the time of initial reset

\*2 Not set in the circuit

\*3 Undefined

- \*4 Reset (0) immediately after being read

- \*5 Constantly "0" when being read

\*6 Refer to main manual

\*7 Page switching in I/O memory is not necessary

| Address |      | Reg  | ister |       |       |         |        |                       | Comment                          |

|---------|------|------|-------|-------|-------|---------|--------|-----------------------|----------------------------------|

| *7      | D3   | D2   | D1    | D0    | Name  | Init *1 | 1      | 0                     | Comment                          |

|         | 0    | 0    | 0     | R0HIZ | 0 *5  | - *2    |        |                       | Unused                           |

| AOH     | 0    | 0    | 0     |       | 0 *5  | - *2    |        |                       | Unused                           |

| AUL     |      | R    |       | R/W   | 0 *5  | - *2    |        |                       | Unused                           |

|         |      | п    |       | N/ W  | R0HIZ | 0       | High-Z | Output                | R0 output high-impedance control |

|         | R03  | R02  | R01   | R00   | R03   | 0       | High   | Low                   |                                  |

| A1H     | 1100 | 1102 | 1101  | 1100  | R02   | 0       | High   | Low                   | Output port (R00–R03)            |

|         | R/W  |      |       | R01   | 0     | High    | Low    | Surput port (NOO-NOS) |                                  |

|         |      |      |       |       | R00   | 0       | High   | Low                   |                                  |

|         | 0    | 0    | 0     | R1HIZ | 0 *5  | - *2    |        |                       | Unused                           |

| A2H     | U    |      |       |       | 0 *5  | - *2    |        |                       | Unused                           |

| 7211    |      | R    |       | R/W   | 0 *5  | - *2    |        |                       | Unused                           |

|         |      |      |       | 10.44 | R1HIZ | 0       | High-Z | Output                | R1 output high-impedance control |

|         |      | R12  | R11   | R10   | R13   | 0       | High   | Low                   | Output port (R13)                |

|         | R13  |      |       |       | R12   | 0       | High   | Low                   | Output port (R12)                |

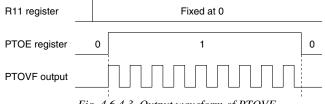

|         |      | BZ   | PTOVF | FOUT  | BZ    | 0       | Off    | On                    | Buzzer output                    |

| A3H     |      |      |       |       | R11   | 0       | High   | Low                   | Output port (R11)                |

|         |      | _    |       |       | PTOVF | 0       | Off    | On                    | PTOVF output                     |

|         |      | R    | /W    |       | R10   | 0       | High   | Low                   | Output port (R10)                |

|         |      |      |       |       | FOUT  | 0       | Off    | On                    | FOUToutput                       |

Table 4.1.1(c) I/O memory map (A0H–A3H)

Table 4.1.1(d) I/O memory map (B0H–B6H)

| Address |                                                                              | Reg          | ister       |           |       |         |        |            | Comment                                     |

|---------|------------------------------------------------------------------------------|--------------|-------------|-----------|-------|---------|--------|------------|---------------------------------------------|

| *7      | D3                                                                           | D2           | D1          | D0        | Name  | Init *1 | 1      | 0          | Confinent                                   |

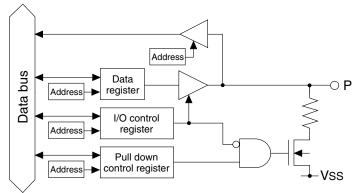

|         | IOC03                                                                        | IOC02        | IOC01       | 10C00     | IOC03 | 0       | Output | Input      |                                             |

| вон     | 10003                                                                        | 10002        | 10001       | 10000     | IOC02 | 0       | Output | Input      | I/O control register (P00–P03)              |

| БОП     |                                                                              | D/           | w           |           | IOC01 | 0       | Output | Input      | 10 control register (100–103)               |

|         |                                                                              | 11           | ···         | -         | IOC00 | 0       | Output | Input      |                                             |

|         | PUL03                                                                        | PUL02        | PUL01       | PUL00     | PUL03 | 1       | On     | Off        |                                             |

| B1H     | 1 0200                                                                       |              |             | 1 0200    | PUL02 | 1       | On     | Off        | Pull down control register (P00–P03)        |

| DIII    |                                                                              | B/           | w           |           | PUL01 | 1       | On     | Off        |                                             |

|         |                                                                              |              |             |           | PUL00 | 1       | On     | Off        |                                             |

|         | P03                                                                          | P02          | P01         | P00       | P03   | - *2    | High   | Low        |                                             |

| B2H     |                                                                              |              |             |           | P02   | - *2    | High   | Low        | I/O port (P00–P03)                          |

| DZIT    | B/W                                                                          |              |             |           | P01   | - *2    | High   | Low        |                                             |

|         | 1000                                                                         |              |             |           | P00   | - *2    | High   | Low        |                                             |

|         | IOC13                                                                        | IOC12        | IOC11       | 10C10     | IOC13 | 0       | Output | Input      |                                             |

|         |                                                                              |              |             |           | IOC12 | 0       | Output | Input      | I/O control register (P10–P13)              |

|         |                                                                              | B/           | w           |           | IOC11 | 0       | Output | Input      | (ESIF = 0)                                  |

|         | When the serial I/F is used (ESIF = 1):<br>P10 = SIN (in), P11 = SOUT (out), |              |             |           | IOC10 | 0       | Output | Input      |                                             |

| B4H     |                                                                              |              |             |           | IOC13 | 0       | Output | Input      | Master mode: P13 I/O control register       |

|         |                                                                              |              |             |           | IOC13 | 0       | 1      | 0          | Slave mode: General-purpose register        |

|         | P12 = SC                                                                     | CLK (mast    | er: out, sl | ave: in), | IOC12 | 0       | 1      | 0          |                                             |

|         | P13 = SF                                                                     | RDY (slave   | e: out),    |           | IOC11 | 0       | 1      | 0          | General-purpose register                    |

|         | P13 = I/0                                                                    | ) port (ma   | ster: in/ou | t)        | IOC10 | 0       | 1      | 0          |                                             |

|         | PUL13                                                                        | PUL12        | PUL11       | PUL10     | PUL13 | 1       | On     | Off        |                                             |

|         |                                                                              |              |             |           | PUL12 | 1       | On     | Off        | Pull down control register (P10–P13)        |

|         |                                                                              | B/           | w           |           | PUL11 | 1       | On     | Off        | (ESIF = 0)                                  |

|         |                                                                              |              |             |           | PUL10 | 1       | On     | Off        | <u>`````````````````````````````````</u>    |

| B5H     | When the                                                                     | e serial I/F | is used (I  | ESIF = 1: | PUL13 | 1       | On     | Off        | Master mode: P13 pull down control register |

| Don     |                                                                              | N (in), P1   |             |           | PUL13 | 1       | 1      | 0          | Slave mode: General-purpose register        |

|         |                                                                              | CLK (mast    | · · ·       | ave: in), | PUL12 | 1       | 1      | 0          | Master mode: General-purpose register       |

|         |                                                                              | RDY (slave   |             |           | PUL12 | 1       | On     | Off        | Slave mode: SCKL pull down control register |

|         | P13 = I/0                                                                    | ) port (ma   | ster: in/ou | t)        | PUL11 | 1       | 1      | 0          | General-purpose register                    |

|         |                                                                              |              |             |           | PUL10 | 1       | On     | Off        | SIN pull down control register              |

|         | P13                                                                          | P12          | P11         | P10       | P13   | - *2    | High   | Low        |                                             |

|         |                                                                              |              |             |           | P12   | - *2    | High   | Low        | I/O port (P10–P13)                          |

| B/W     |                                                                              |              |             | P11       | - *2  | High    | Low    | (ESIF = 0) |                                             |

|         |                                                                              |              |             |           | P10   | - *2    | High   | Low        | `                                           |

| B6H     |                                                                              | e serial I/F |             |           | P13   | - *2    | High   | Low        | Master mode: I/O port P13                   |

|         |                                                                              | N (in), P1   |             |           | P13   | - *2    | 1      | 0          | Slave mode: General-purpose register        |

|         |                                                                              | CLK (mast    |             | ave: in), | P12   | - *2    | 1      | 0          |                                             |

|         |                                                                              | RDY (slave   |             |           | P11   | - *2    | 1      | 0          | General-purpose register                    |

|         | P13 = I/C                                                                    | ) port (ma   | ster: in/ou | t)        | P10   | - *2    | 1      | 0          |                                             |

E0C6256 TECHNICAL HARDWARE

| Address | Register |      |       |              |                              |                   |               | <b>2</b>            |                                                    |

|---------|----------|------|-------|--------------|------------------------------|-------------------|---------------|---------------------|----------------------------------------------------|

| *7      | D3       | D2   | D1    | D0           | Name                         | Init *1           | 1             | 0                   | Comment                                            |

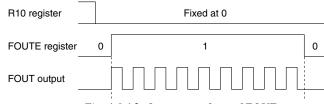

|         | FOUTE    | 0    |       | FOFOO        | FOUTE                        | 0                 | Enable        | Disable             | FOUT output enable                                 |

| 0011    | FOULE    | 0    | FOFQ1 | FOFQ0        | 0 *5                         | - *2              |               |                     | Unused                                             |

| COH     | DAA      |      |       |              | FOFQ1                        | 0                 |               |                     | FOUT frequency selection                           |

|         | R/W      | R    | К     | W            | FOFQ0                        | 0                 |               |                     | 0: 512 Hz, 1: 4096 Hz, 2: fosc1, 3: fosc3          |

|         | 0        | 0    | 0     | WDDOT        | 0 *5                         | - *2              |               |                     | Unused                                             |

| 0411    | 0        | 0    | 0     | WDRST        | 0 *5                         | - *2              |               |                     | Unused                                             |

| C1H     |          |      | •     | 14/          | 0 *5                         | - *2              |               |                     | Unused                                             |

|         |          | R    |       | W            | WDRST <sup>*5</sup>          | Reset             | Reset         | -                   | Wachdog timer reset                                |

|         | LDMS     | STCD | LDTY1 | LDTY0        | LDMS                         | 0                 | 1p(R/W)       | 5p(W)               | LCD data memory area selection                     |