# DIGITAL TECHNIQUES IN DELTA MODULATION

BY

CORNELIS JAN KIKKERT, B.E. (Hons.)

A Thesis

Submitted to the Faculty of Engineering

of the

University of Adelaide

for the Degree of

Doctor of Philosophy

FEBRUARY 1972

|                                                 | II   |

|-------------------------------------------------|------|

| INDEX                                           |      |

| TITLE PAGE                                      | I    |

| TABLE OF CONTENTS                               | II   |

| SULMARY                                         | VIII |

| STATELENT                                       | X    |

| ACKNOVLEDGEMENT                                 | XI   |

| LIST OF ABBREVIATIONS                           | XIJ  |

|                                                 |      |

| CHAPTER 1 INTRODUCTION                          | 1    |

| 1.1 Code Modulation                             | 1    |

| 1.1.1 Pulse Code Modulation                     | 1    |

| 1.1.2 Differential Pulse Code Modulation        | 2    |

| 1.1.3 Delta Modulation                          | 3    |

| 1.2 Quantization Noise                          | 3    |

| 1.3 Historical Review                           | 4    |

| 1.3.1 The Development of Delta Modulation       | 5    |

| 1.3.2 Instantaneous Companding                  | 6    |

| 1.3.3 Syllabic Companding                       | 8    |

|                                                 |      |

| CHAPTER 2 THE MEASUREMENT OF THE PERFORMANCE OF |      |

| DELTA MODULATION AND RELATED SYSTEMS            | 11   |

| 2.1 Introduction                                | 11   |

| 2.2 Review                                      | 11   |

| 2.3 Measurement of Signal to Quantization       |      |

| Noise Ratio for Random Input Signals            | 14   |

|         |        |                                      | III        |

|---------|--------|--------------------------------------|------------|

|         | 2.3.1  | Definition of Quantization Noise     | 14         |

|         | 2.3.2  | Disadvantages of Using Sinewaves     |            |

|         |        | for Measurements                     | 15         |

| 2.4     | Measur | rement Equipment Description         | 17         |

|         | 2.4.1  | Theory                               | 17         |

|         | 2.4.2  | Measurement of Power                 | 19         |

| 2.5     | Hardwa | are Description                      | 20         |

|         | 2.5.1  | Tapped Delay Line                    | 21         |

|         | 2.5.2  | Power Measurement                    | 22         |

|         | 2.5.3  | Accuracy Considerations              | 23         |

| 20      | 2.5.4  | Results                              | 23         |

| 2.6     | Conclu | sions                                | 24         |

| CHAPTER | 3 THE  | DEVELOPMENT OF HONLINEAR DIGITAL     |            |

|         | DELT   | 'A MODULATION                        | 25         |

| 3.1     | Introd | uction                               | 25         |

| 3.2     | Instan | taneous Companding                   | 25         |

|         | 3.2.1  | Principles of Instantaneous Compandi | .ng 25     |

|         | 3.2.2  | Dynamic Range Considerations         | 27         |

|         | 3.2.3  | Nonlinear Instantaneous Companding   | 28         |

|         | 3.2.4  | Improvement of Stability             | 29         |

|         | 3.2.5  | Error Performance                    | 31         |

|         | 3.2.6  | Summary of Companding Strategy       | <b>3</b> 3 |

| 3.3     | Optimi | zation                               | 34         |

|         | 3.3.1  | Aims of Optimization                 | 34         |

|         | 3.3.2  | Selection of Parameters              | 35         |

|         |                                              | IV          |

|---------|----------------------------------------------|-------------|

|         | 3.3.3 Accuracy Considerations                | 38          |

| 3.4     | Practical Realisation                        | 39          |

|         | 3.4.1 Hardware                               | 39          |

|         | 3.4.2 Results                                | 40          |

| 3.5     | Extensions                                   | 41          |

| 3.6     | Conclusions                                  | 42          |

|         |                                              |             |

| CHAPTER | 4 DIGITAL SYLLABIC COMPANDED DELTA MODULATIO | <u>N</u> 43 |

| 4.1     | Introduction                                 | 43          |

| 4.2     | Syllabic Companding                          | 43          |

|         | 4.2.1 Companding with Incomplete Control     | 44          |

|         | 4.2.2 Companding with Complete Control       | 45          |

| 4.3     | Companding with Complete Control,            |             |

|         | Applied to Delta Modulation                  | 46          |

|         | 4.3.1 Detection of Normalised Input Power    | 47          |

|         | 4.3.2 Linear Companding                      | 48          |

|         | 4.3.3 Logarithmic Companding                 | 50          |

|         | 4.3.4 Semilogarithmic Companding             | 52          |

| 4.4.    | Discussion of Parameters                     | 54          |

|         | 4.4.1 Selecting the Companding Ratio         | 54          |

|         | 4.4.2 The Effect of Transmission Errors      | 55          |

|         | 4.4.3 Stability Considerations               | 58          |

| 4.5     | The Design of a Digital Syllabic             |             |

|         | Companded Delta Modulation System            | 59          |

|         | 4.5.1 Selection of Parameters                | 59          |

|         | 4.5.2 Computer Simulation                    | 61          |

|         |                                              |             |

|                                                      | V    |

|------------------------------------------------------|------|

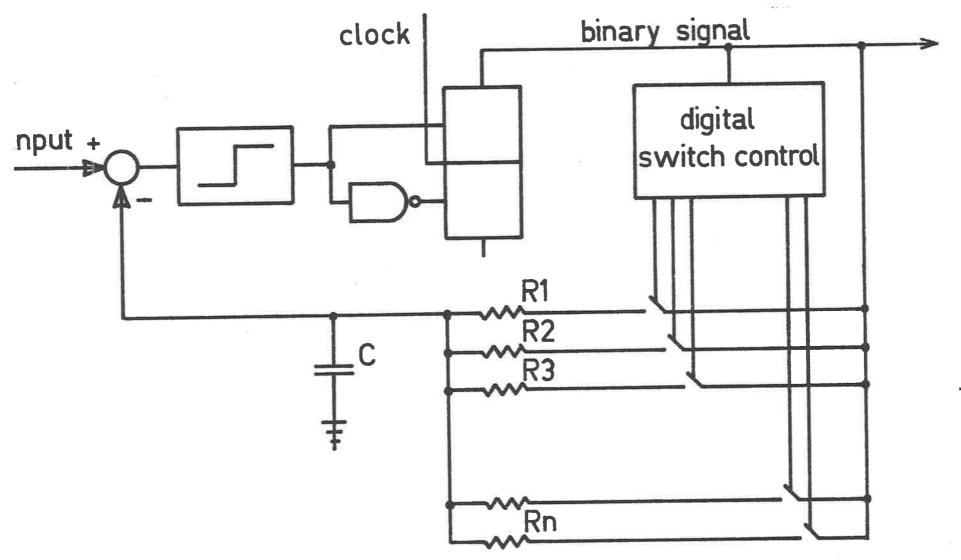

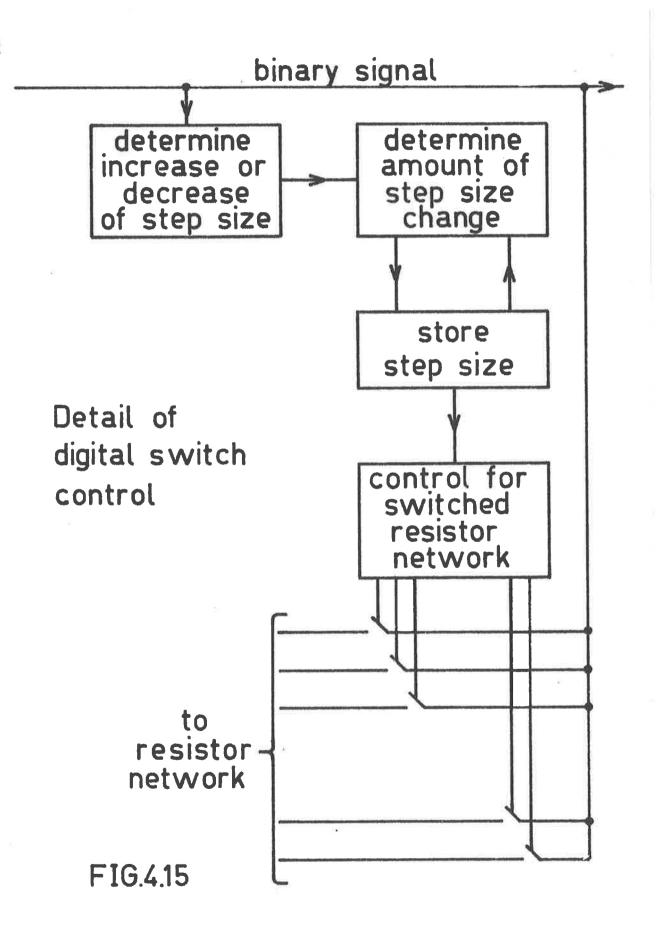

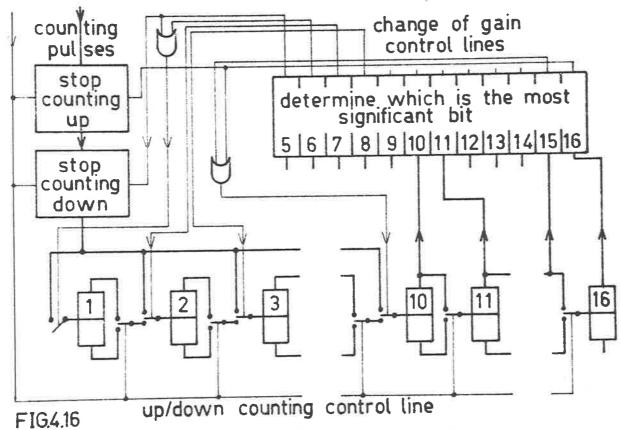

| 4.5.3 Hardware                                       | 63   |

| 4.6 Extension to Other Modulators                    | 66   |

| 4.7 Conclusions                                      | 67   |

| CHAPTER 5 COMPUTER SIMULATION                        | 68   |

| 5.1 Introduction                                     | 68   |

|                                                      |      |

| 5.2 Particular Examples of Simulation                | 69   |

| 5.2.1 Simulation of Delta Modulation                 | 69   |

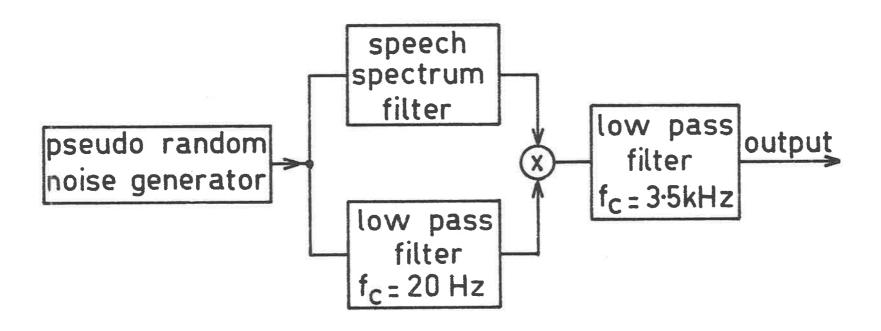

| 5.2.2 Simulation of S eech                           | 70   |

| 5.3 Results                                          | 7.1  |

| ×2                                                   |      |

| CHAPTER 6 CONCLUSIONS                                | 74   |

|                                                      |      |

| APPENDIX 1 METHODS FOR EVALUATION OF THE PERFORMANCE |      |

| OF DELTA MODULATION                                  |      |

| A1.1 Intelligibility Tests                           | A1/1 |

| A1.2 Equivalent White Noise Method                   | A1/2 |

| A1.3 Notch Filter Method                             | Δ1/3 |

| A1.4 Frequency Analysis Method                       | Λ1/4 |

| A1.5 Cancellation Method                             | Λ1/4 |

| A1.6 Intermodulation Distortion Method               | A1/5 |

|                                                      |      |

| APPETDIX 2 HARDWARE                                  |      |

| A2.1 Introduction                                    | A2/1 |

| A2.2 Measuring Equipment Hardware                    | Λ2/1 |

| A2.3 Monlinear Digital Delta Modulation Hardware     | A2/1 |

|          |                                              | VI       |

|----------|----------------------------------------------|----------|

| 341      | A2.3.1 Hardware of the Modulator             | V5/5     |

|          | A2.3.2 Demodulator Hardware                  | Λ2/2     |

| A2.4     | Digital Syllabic Companded Delta Modulation  |          |

|          | Hardware                                     | A2/3     |

|          | A2.4.1 Circuitry of the Modulator            | A2/3     |

|          | A2.4.2 Circuitry of the Demodulator          | A2/5     |

|          | 2                                            |          |

| APPENDIX | 3 COMPUTER PROGRAMS                          |          |

| A3.1     | Main Program                                 | A3/1     |

| A3.2     | Delta and Pulse Code Modulation Subroutines  | Δ3/4     |

|          | A3.2.1 Single Integration Delta Modulation   | A3/4     |

| 5        | A3.2.2 Digital Syllabic Companded            |          |

|          | Delta Modulation                             | A3/4     |

|          | A3.2.3 Monlinear Digital Delta Modulation    | Λ3/5     |

|          | A3.2.4 Digitally Syllabic Companded PCM      | A3/6     |

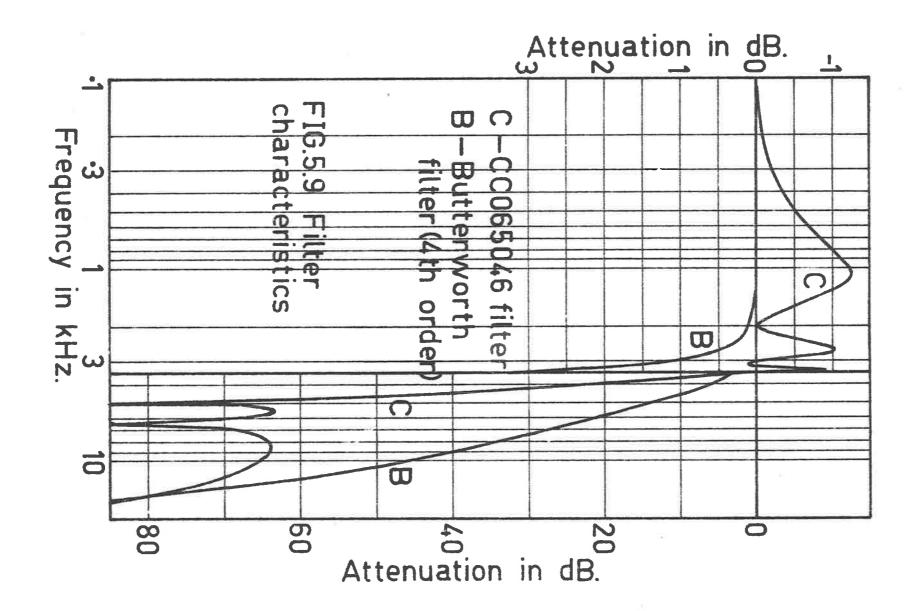

| А3.3     | Digital Filtering Subroutines                | A3/8     |

|          | A3.3.1 Filter Testing Program                | A3/8     |

|          | A3.3.2 Subroutines to Design the Speech Filt | er A3/10 |

|          | A3.3.3 Speech Filter Subroutine              | A3/11    |

|          | A3.3.4 Subroutine to Design a 4th Order      |          |

|          | Low Pass Butterworth Filter                  | A3/12    |

|          | A3.3.5 4th Order Low Pass Butterworth        |          |

|          | Filter Subroutine                            | A3/12    |

|          | A3.3.6 General Filter Design Subroutine      | A3/13    |

|          | A3.3.7 General Filter Subroutine             | A3/15    |

|                            |                                               | VII          |

|----------------------------|-----------------------------------------------|--------------|

| A3.4                       | Other Subroutines                             | A3/16        |

|                            | A3.4.1 Subroutine to Generate a Pseudo        |              |

|                            | Random Sequence                               | A3/16        |

|                            | A3.4.2 Subroutine to Calculate the RMS Power  | Λ3/16        |

|                            | A3.4.3 Subroutine to Calculate the Average    |              |

|                            | Signal                                        | A3/17        |

|                            | A3.4.4 Subroutine to Calculate the Relative   |              |

|                            | Occurrence of Control Words                   | A3/18        |

|                            | A3.4.5 Subroutine to Calculate the Group      |              |

|                            | Delay                                         | A3/20        |

|                            |                                               |              |

| APPENDIX                   | 4 ASSOCIATED MATHEMATICS                      |              |

| A4 • 1                     | Digital Filtering Theory                      | A4/1         |

| Λ4.2                       | Leaky Integrator Simulation                   | $\Delta 4/7$ |

| A4.3                       | Delay of an RC Network                        | A4/8         |

| Α4.4                       | The SNR Obtained from the Notch Filter Method | •            |

|                            | when Slope Limiting Occurs                    | Λ4/10        |

|                            | e a                                           |              |

| V <b>T/T</b> 17/17/17 (* ↑ | ב סווסדדמווש אם מיינים אם                     |              |

# APPENDIX 5 PUBLISHED PAPERS

- A5.1 Patent: A Method for Improving Modulation Efficiency

- A5.2 Digital Techniques in Delta Modulation

- A5.3 Measurements of Quantization Distortion for Random Inputs

## REFERENCES

# BIBLIOGRAPHY

#### SUMMARY

During the last twenty years delta modulation has received considerable attention as a simple but inefficient method of coding analogue signals into binary signals. Companding is used to improve the efficiency of the delta modulation process, but it gives added complexity to the hardware, so that a compromise is usually made between the performance and complexity of the delta modulator.

Recently, with the advent of integrated circuit (IC) technology it became apparent that firstly, the hardware was becoming cheaper and secondly, the cost of the IC was not strictly related to the complexity of the IC, but rather to the number of IC's made.

Because the input to the demodulator is a binary signal, delta modulation is ideally suited to the use of digital techniques in the demodulation process. Further advantages of digital techniques are; stability, noise immunity, tolerance to power supply and temperature variations, a higher yield during the manufacture of the IC and the ability to reproduce exactly the same signal at two different locations.

An efficient and therefore complex delta modulator, using digital techniques, will thus in the near future be an economical proposition.

This thesis is mainly concerned with the development of delta modulators using the above features. Furthermore

the delta modulators are specifically designed for speech transmission in telephone applications.

Two delta modulators are described in the thesis, one using instantaneous companding, the other using syllabic companding. It will be shown that the use of digital techniques in instantaneous companding can achieve a better transmission error performance, an improved stability, a wider dynamic range and a better matching of the companding laws at the transmitter and the receiver than can be obtained by using analogue methods.

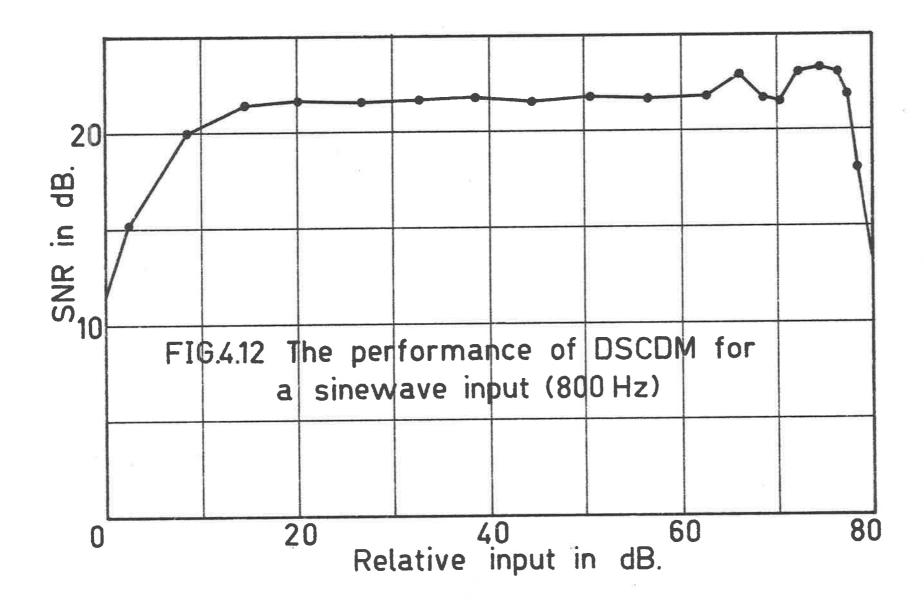

The use of digital techniques in syllabic companding enables the dynamic range to be chosen at will. The syllabic companded delta modulator described in this thesis has a 60dB companding ratio which is far more than can be obtained using analogue methods. Furthermore, digital techniques enable the modulation depth to be determined accurately, so that the companding takes place at the optimum performance of the modulator.

Computer simulation was used to optimize the delta modulators when speech is used as input.

#### STATEMENT OF ORIGINALITY

This thesis contains no material which has been accepted for the award of any other degree or diploma in any University and that, to the best of my knowledge and belief the thesis contains no material previously published or written by another person, except when due reference is made in the text of the thesis.

Cornelis Jan Kikkert.

#### AKNOVLEDGEMENTS

The author wishes to thank the staff of the Electrical Engineering Department at the University of Adelaide and in particular his supervisors, Mr. D. C. Pawsey and Dr. B. R. Davis for their encouragement, helpful comments and suggestions.

The author also thanks the Australian Government for making a Commonwealth Post Graduate Scholarship available during the first two years of this project.

Finally I would like to thank my wife Maxine for her encouragement, patience and for typing this thesis

#### LIST OF ABBREVIATIONS

DIDM - double integration delta modulation

∧M or DM - delta modulation

ΔPCM - delta pulse code modulation

ΔΣM - delta sigma modulation

IC - integrated circuit

NDDM - nonlinear digital delta modulation

PCM - pulse code modulation

RTL - resistor transistor logic

SIDM - single integration delta modulation

SNR - signal to (quantization) noise ratio

TTL - transistor transistor logic

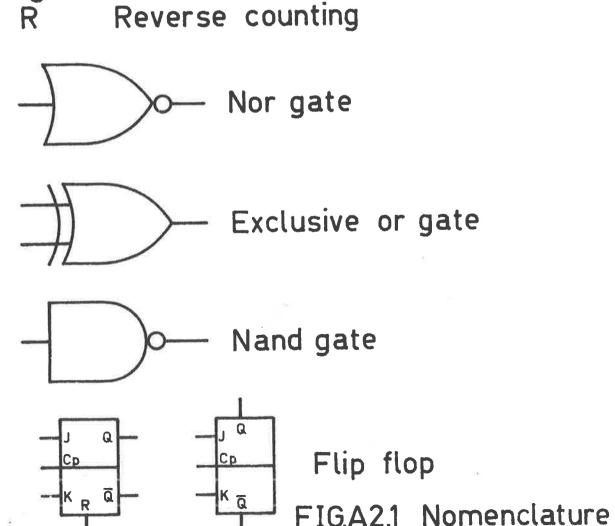

The graphical representation of the logic symbols used in the figures is shown in Appendix 2 in fig A2.1.

# CHAPTER 1

#### INTRODUCTION

#### 1.1 Code Modulation

Code modulation is a group of modulation processes where an analogue signal is coded into a binary signal. In order for this process to be possible, the analogue waveform must be sampled. These samples are then approximated to the nearest standard signal, this process is known as quantization. The standard signal is then represented by a certain binary coded word. These code words are then transmitted and at the receiver they are decoded into standard signals, giving a demodulated output which is an approximation of the input.

Because the analogue input is sampled, the sampling rate must be larger than the Nyquist rate, i.e. at least twice the bandwith of the input signal.

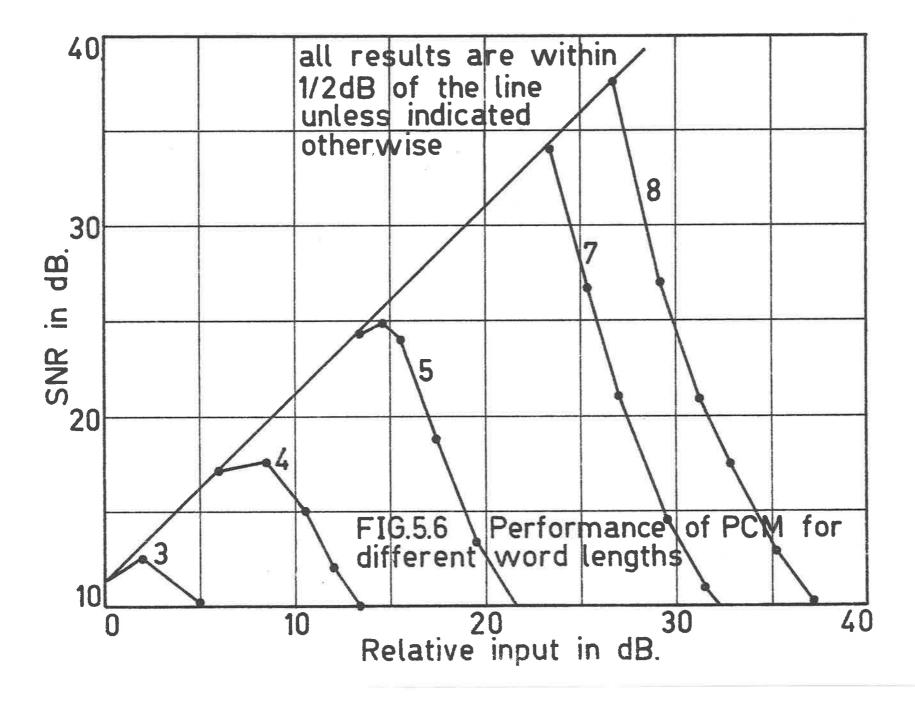

#### 1.1.1 Pulse Code Modulation

In pulse code modulation, (PCM) the range of amplitude over which the input signal is to operate is divided into n regions. In each region a standard level is chosen, which is usually the middle of the region. These regions are numbered 0 to n-1. At each sampling interval, the region in which the input signal falls is determined, and the number corresponding to this region is transmitted. At the receiver this information is decoded into the standard level for the

particular region. It is clear that all the input signals in one region are represented by the standard level and approximations of the input are involved.

From information theory it is clear that the most information about the signal will be transmitted if we choose the regions such that each of the regions has an equal probability of containing the input signal.

The most common spacings between the standard levels are linear and logarithmic, neither of which necessarily gives the best performance, depending on the signal being used.

The linear standard level division is often used in computer interfaces, where the pulse code modulation is known as analogue to digital conversion and the demodulation as digital to analogue conversion.

## 1.1.2 Differential Pulse Code Modulation

In differential pulse code modulation (APCM), the change of level is transmitted, instead of the absolute level as in PCM.

Because in A PCM the change of input is transmitted it is more suitable to input signals which have a spectrum that decreases with frequency, so that the rate of change of input is constant.

Both linear and logarithmic spacing between the standard levels can be used as for PCM.

## 1.1.3 Delta Modulation

Delta modulation is a special name for unity bit APCM. At each sampling interval we will thus send the information "increase output" or "decrease output". Because so little information is transmitted at each sampling interval, it can be seen that in order to transmit sufficient information to reconstruct the input signal accurately the sampling frequency must be many times the Nyquist rate.

Typical values for the sampling rate are between two and twelve times the Myquist rate, depending on the accuracy required.

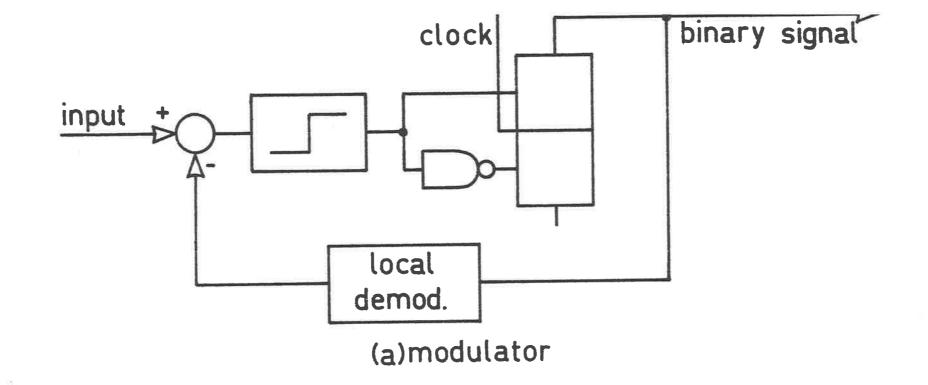

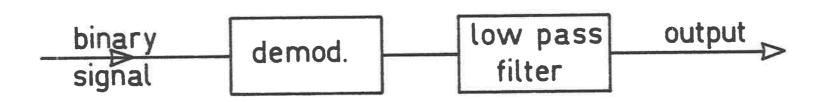

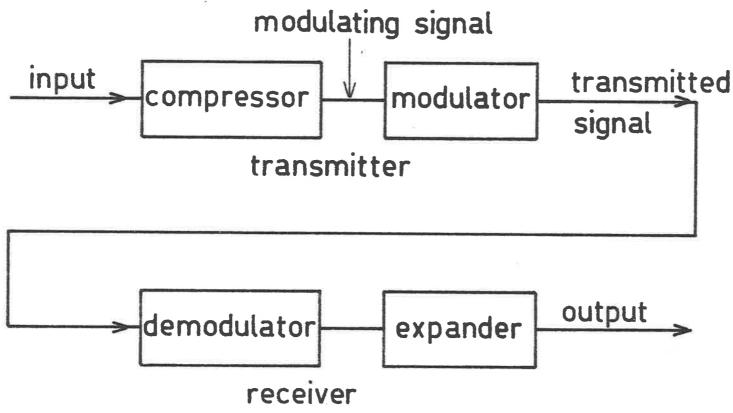

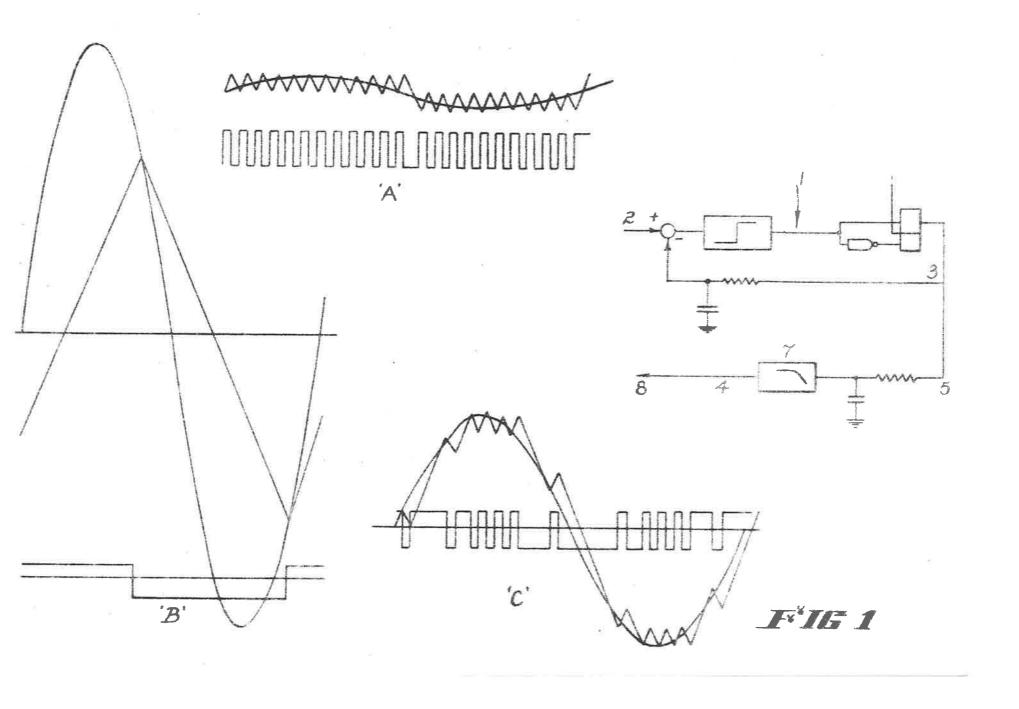

Furthermore because only one bit of information is transmitted at each sampling interval, the basic delta modulator is very simple. The block diagram for the system is shown in fig 1-1 and the input and unfiltered demodulated output waveform for the case where the demodulator is simply an integrator are shown in fig 1-2.

The low pass filter in the demodulator removes those frequency components of the unfiltered demodulated output signal that are outside the signal bandwidth, giving an output signal that closely resembles the input signal.

#### 1.2 Quantization Noise

In section 1.1 it was stated that in code modulation, the input signal is converted into a standard signal, which is then coded and transmitted. The distortion introduced by

(b)demodulator FIG.1.1 Delta modulator block diagram.

Delta modulator waveforms.

converting the input signal into the standard signal is known as the quantization noise. The quantization noise can thus be defined as the difference between the input and quantized waveforms. Furthermore, usually one is only interested in those frequency components of the quantization noise that lie inside the signal bandwidth, so that generally the term quantization noise only refers to those frequency components. It should be noted that the definition allows for a delay or amplitude change, introduced by the quantization process, since neither will affect the waveshape.

## 1.3 <u>Historical Review</u>

# 1.3.1 The Development of Delta Modulation

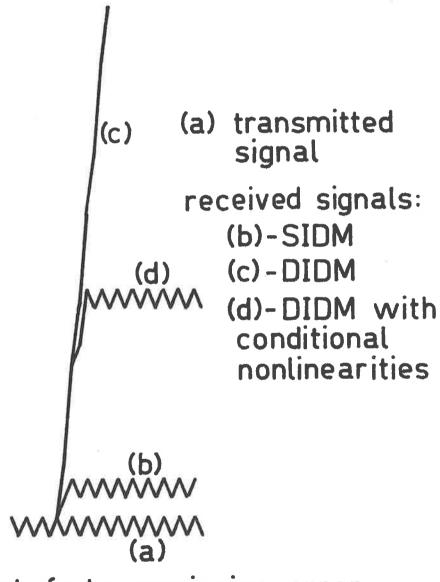

The principle of delta modulation was first described in a French patent <sup>(1)</sup>, issued in 1946. The first description of delta modulation in the English language was given by de Jager <sup>(2)</sup> in 1952. He originated the following intuitive concepts: Firstly, de Jager assumed that speech could be represented by an 800Hz sinewave. Secondly, he empirically derived formulae for the maximum SNR for both single integration delta modulation (SIDM) and double integration delta modulation (DIDM) as:

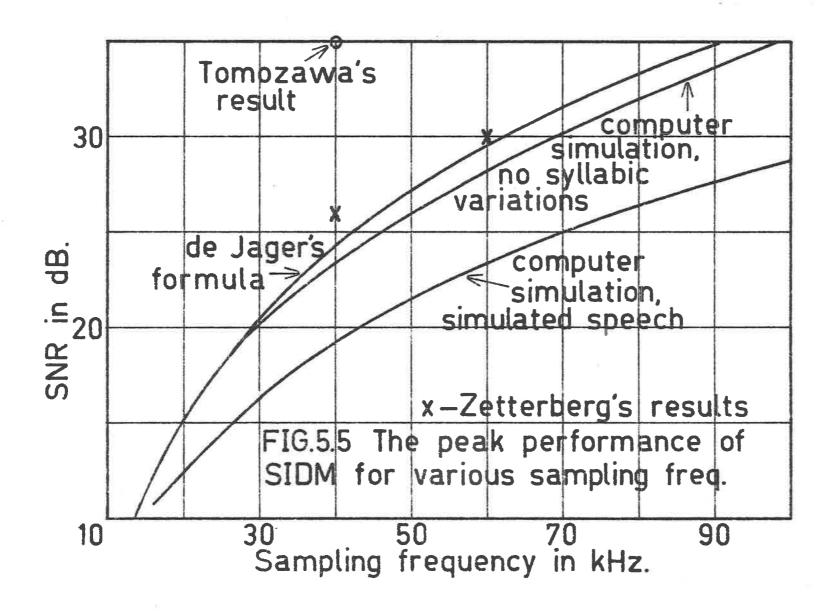

$$SNR_{max} = C_1 \frac{f_s^{3/2}}{f_* f_0^{1/2}}$$

for SIDM

$$SNR_{max} = C_2 - \frac{f_s^{5/2}}{f.f_o^{3/2}}$$

for DIDM

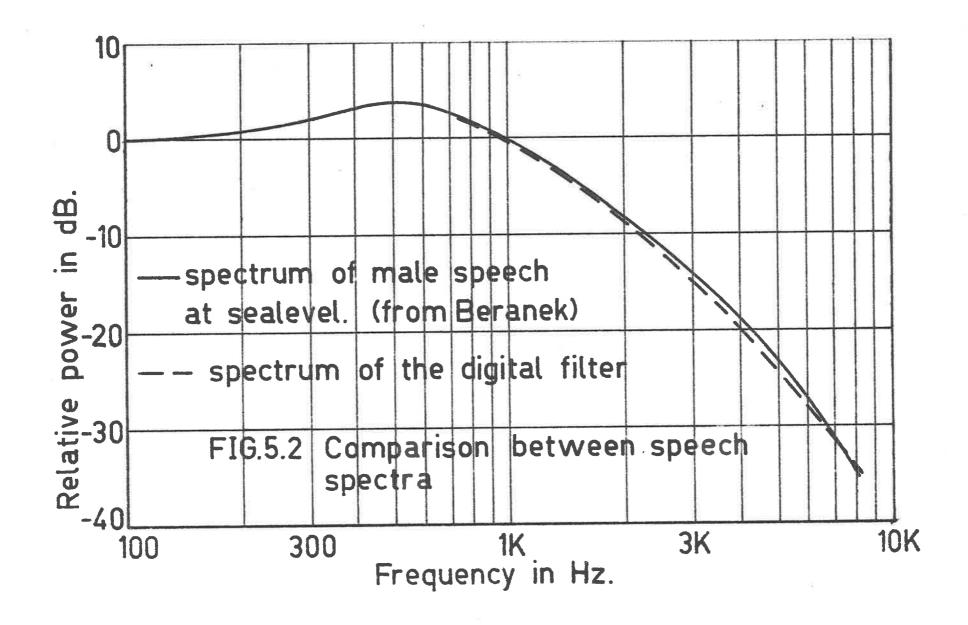

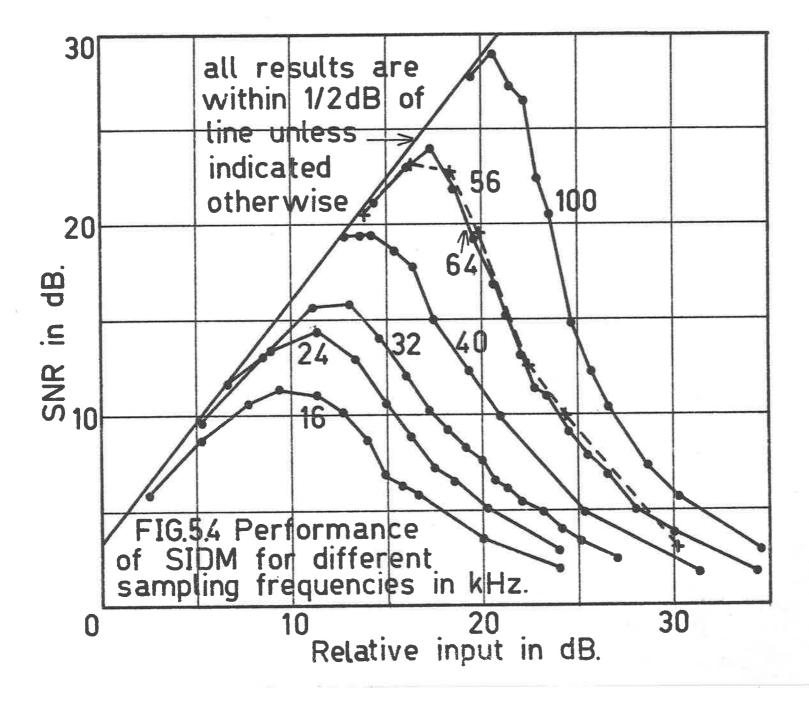

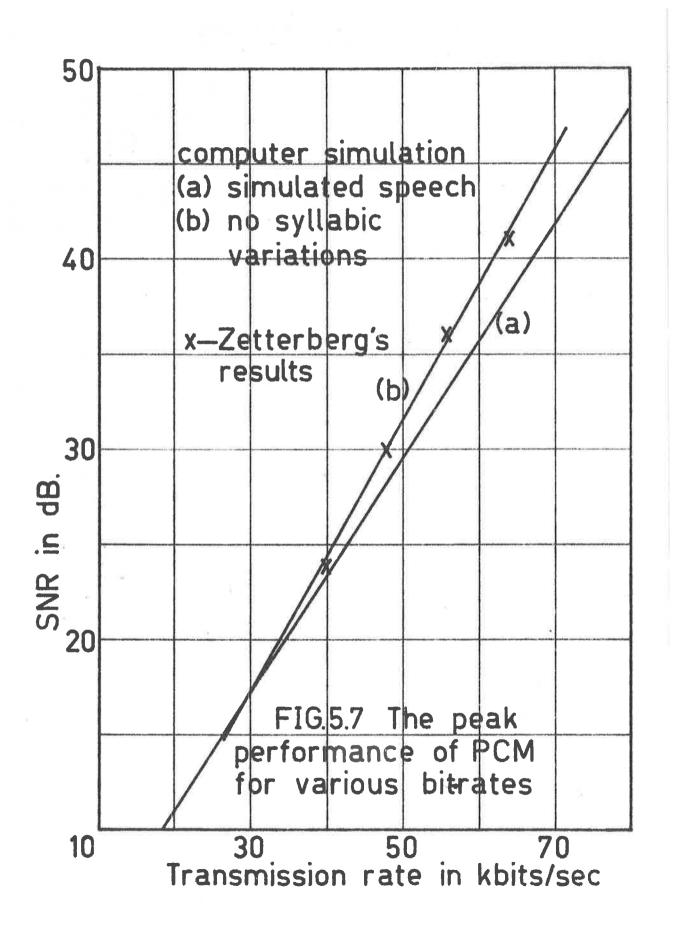

where  $C_1$  and  $C_2$  are constants,  $f_s$  is the sampling frequency, f is the audio signal frequency and  $f_o$  is the audio bandwidth. The constants  $C_1$  and  $C_2$  were determined experimentally as  $C_1 = 0.2$  and  $C_2 = 0.026$ . The maximum STR's obtained using these formulae are indicated in fig 5.5, together with a comparison of the results obtained by others.

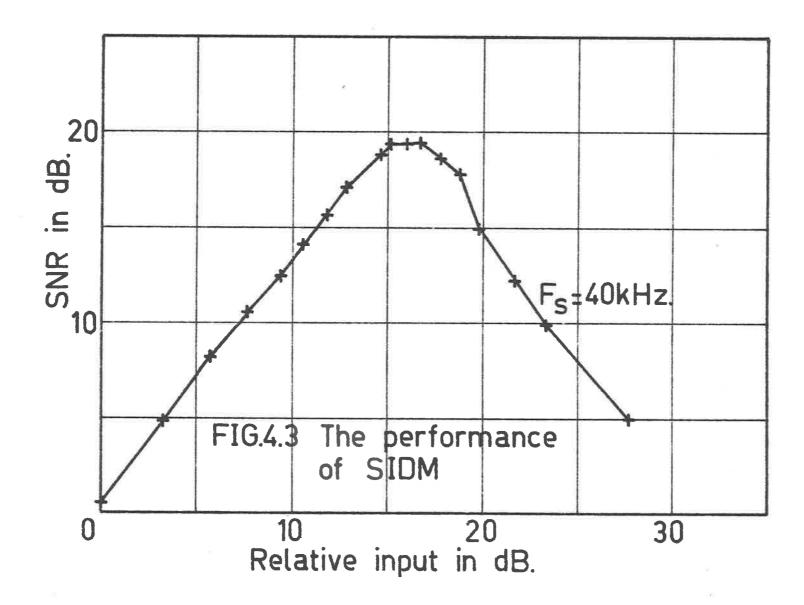

Zettenberg (3) obtained a mathematical model for speech and used this to analyse the performance of SIDM. Syllabic variations of power were however not included in the model for speech. The results obtained agreed reasonably well with the results obtained by de Jager, seemingly justifying de Jager's assumptions for evaluating the performance of SIDM. Zettenberg did however notice that the peak SIR occurred at an input power which was 6dB less than predicted by de Jager's assumptions.

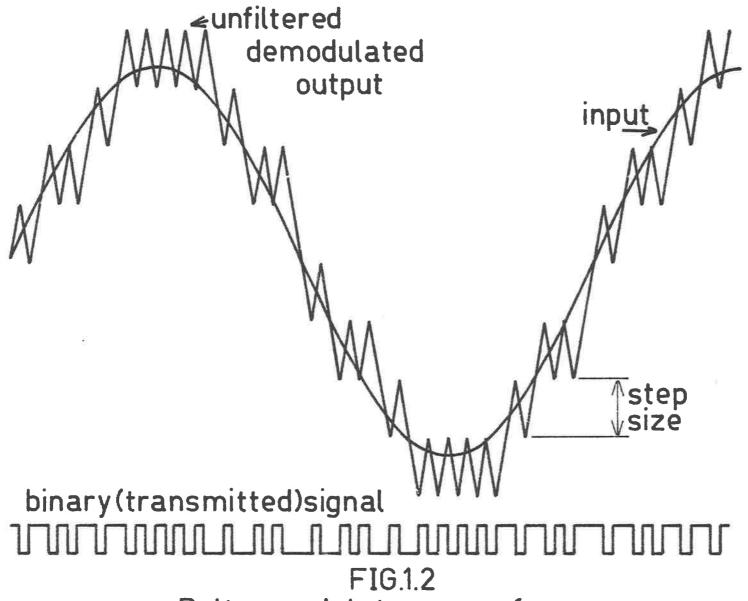

In 1962 Inosi et.al. <sup>(4)</sup> proposed integrating the input signal to obtain a delta modulator capable of handling a uniform spectrum. By re-arranging the block diagram as is shown in fig 1.3 only one integrator needs to be used. The resulting system is known as delta sigma modulation. They <sup>(4)</sup> found that the maximum STR is independent of the audio frequency and is given by:

FIG.1.3

Delta-sigma modulator block diagrams.

$$SNR_{max} = \frac{3}{4\pi} \frac{f_s}{f_o} \frac{3/2}{f_o} \qquad \frac{f_s}{f_o} \frac{3/2}{f_o}$$

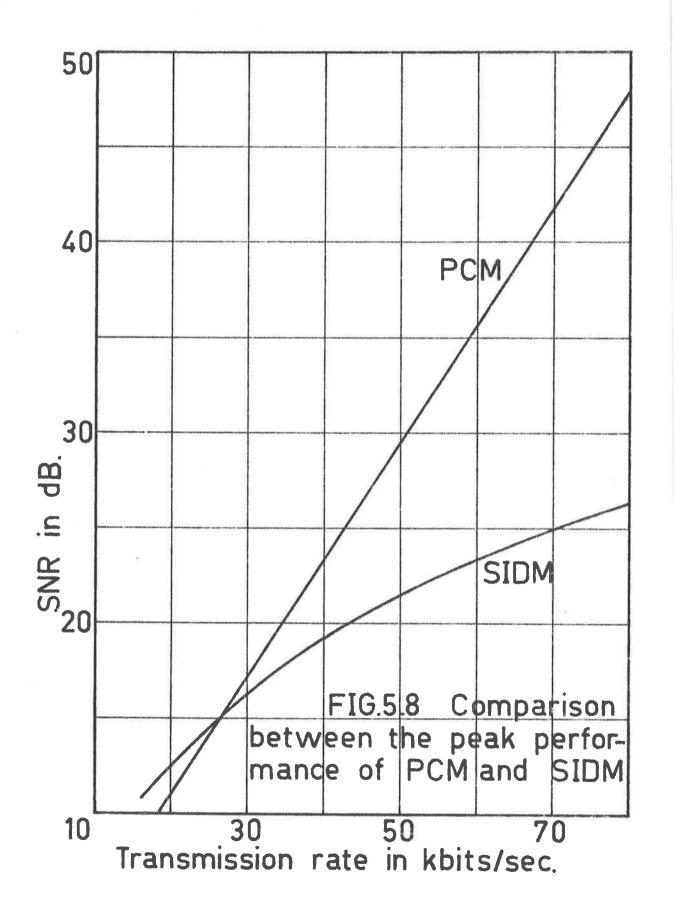

The three systems mentioned above namely SIDM, DIDM and  $\Delta \Sigma M$  are the basic delta modulation systems. The dynamic range of each of these systems can be extended by companding (compressing at the modulator and expanding at the demodulator).

The quantization step size, normally referred to as the step size, is defined as the increment in the unfiltered demodulated output during one clock period, as shown in fig 1.2.

The companding process varies the step size, to adapt the modem to the input signal.

# 1.3.2 Instantaneous Companding

Instantaneous companding has the property that the step size is varied rapidly.

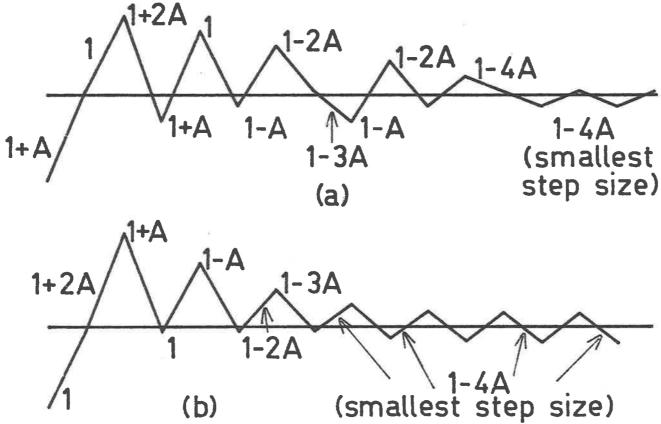

Winkler <sup>(5)</sup>, in 1963, proposed a system known as high information delta modulation. In her system the step size is doubled when three consecutive one's or zero's are detected. The step size is halved when a transition in the binary output occurs. A variation of this rule was developed by Montgomery <sup>(6)</sup> and has been used by the Weapons Research Establishment for their studies for project Mallard <sup>(7)</sup>.

With this variation, known as binary variable slope delta (type A), the step size is halved only if a transition has occurred and the previous two bits were the same.

In 1967 Abate <sup>(8)</sup> described a system where the step size is increased if a sequence of ones or zero's occur and decreased if a transition occurs. It was however not stated how long the sequence of ones or zeros must be before the step size is increased. It is presumed that at least 3 bits are used since if the step size is increased on the second consecutive bit, oscillations can take place, as is indicated in section 4.4.3. Abate found by using computer simulation and a bandlimited Gaussian input signal that a linear increment in step size gave the best performance.

In 1969 Bosworth and Candy <sup>(9)</sup> produced an instantaneous companded delta modulation system. The step size is increased if the transmitted bit is the same as the previous bit. The step size is varied according to the following sequence 1,1,2,3,5. When a transition occurs, the step size is reduced to the smallest step.

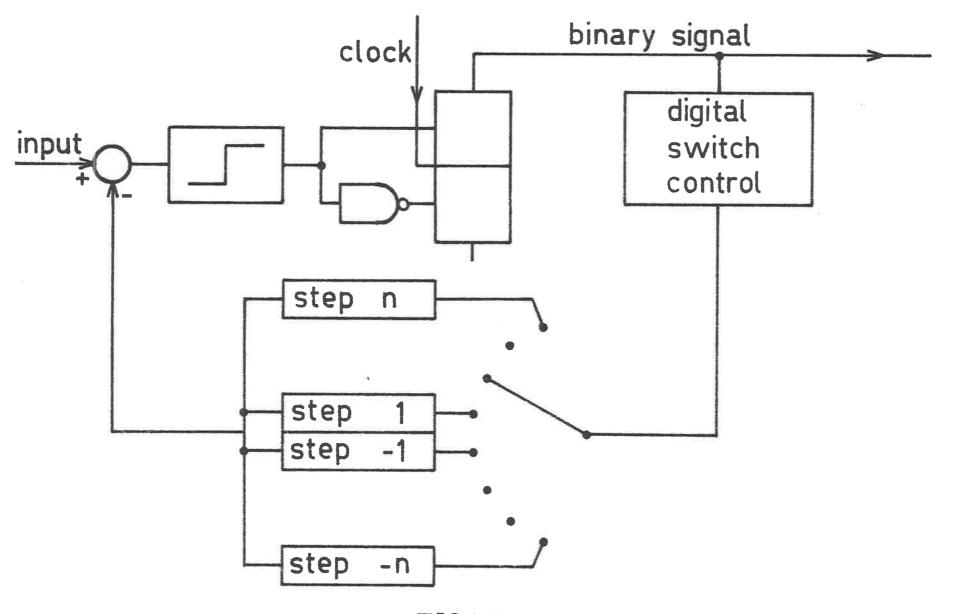

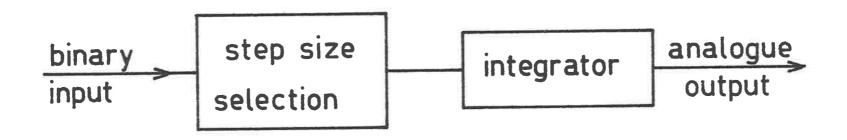

All the above systems can be represented by the block diagram in fig 1.4. In practice satisfactory results can be obtained by using only a small number of different step sizes. Bosworth and Candy for example use 4 step sizes only. However, the companding achieved by the last 2 systems is small. (12dB in the system proposed by Abate)

The author developed an instantaneous companded delta

FIG.1.4

Delta modulator with instantaneous companding.

modulation system which has a companding ratio of 43dB and is described in chapter 3. (The companding ratio is the ratio of the largest to the smallest step size) This companding ratio is far more than has been achieved by other workers (5-9).

## 1.3.3 Syllabic Companding

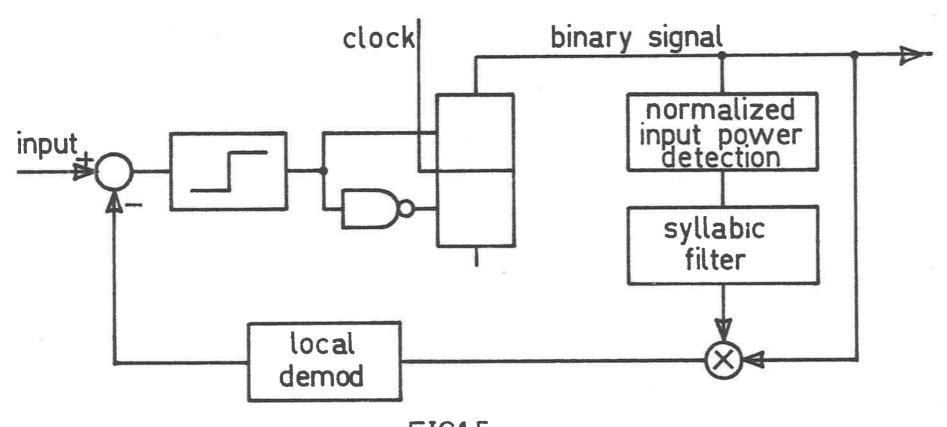

In syllabic companding the step size is varied slowly and in general the system can be represented by the block diagram shown in fig 1.5 The companding should ideally vary the step size in such a way that the modulator always operates at the maximum SNR. A detailed theory of the companding is presented in the sections 4.2 and 4.3. The companding can only stretch the horizontal axis of the SNR versus input power curve, but it cannot alter the maximum SNR's at all. If one compares the maximum SNR's obtained from the following systems one can see that the results are similar, the only difference being the dynamic range over which the companding can be obtained.

Tomozawa and Kaneko (10,11) described a system using syllabic companding in 1966. The normalized input power detection block in fig 1.5 consists of an integrator followed by a half wave rectifier. The filtering consists of a low pass RC network. Their hardware has a companding ratio of 20dB.

Hosokawa et.al. (12) devised a system where the output

FIG.1.5

Delta modulator with syllabic companding.

of the local demodulator is used to control the amplitude of the input to the modulator. In principle this is nearly the same as the incomplete companding proposed in the late thirties (13). A description of complete and incomplete companding is given in section 4.2.

Brolin and Brown <sup>(14)</sup> used two delta modulators, one for audio signal coding, the other to transmit information about the amplitude of the signal. This amounts to transtransmitting a separate pilot signal containing the amplitude of the signal. This is again one of the techniques used to obtain complete companding in the late thirties <sup>(13)</sup>.

The system described by Greefkes and de Jager <sup>(15)</sup> in 1968 uses the bandwidth below 200Hz to code the amplitude information, by adding a DC level, proportional to the signal power to the input signal. In this system the pilot signal containing the amplitude information is transmitted in the bandwidth below 200Hz. Only incomplete companding was achieved however and the companding ratio was about 20dB.

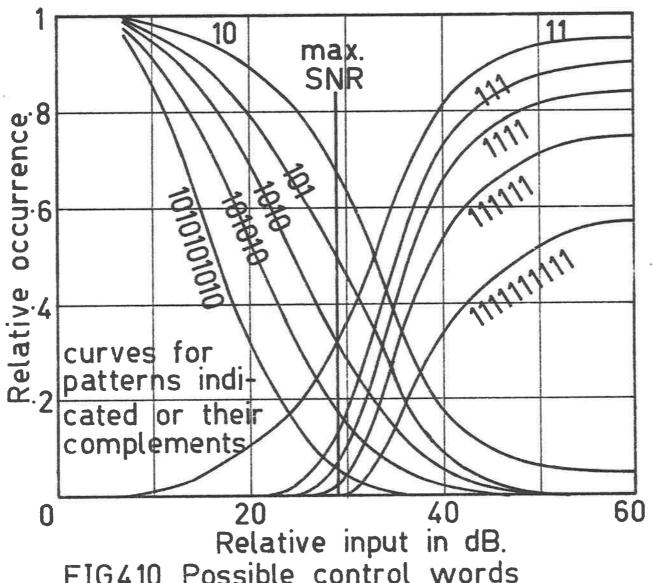

In 1968 Hosokawa and Yamashita <sup>(16)</sup> used logic circuitry for the normalised input power detection block in fig 1.5. Hauser and Zarda <sup>(17)</sup> produced a similar system, but the binary signal required to initiate a change of step size is different.

In 1970 Shindler <sup>(18)</sup> described a system which uses logarithmic companding. This system will be discussed further in section 4.3.3.

None of the above systems have been able to achieve a companding ratio of more than 35dB. In chapter 4 a system developed by the author, is described where the companding ratio can be chosen at will and results are presented for a hardware model incorporating a companding ratio of 60dB.

#### CHAPTER 2

# THE LEASUREMENT OF THE PERFORMANCE OF DELTA MODULATION AND RELATED SYSTEMS

#### 2.1 Introduction

Present indications are that delta modulation if it is to be used in the telephone network will mainly be used for speech applications. In order to develop better delta modulators and to compare the relative performances of different delta modulation systems, a precise measure of the performance must be obtained. Furthermore as shown in this chapter, the performance of a delta modulator when subject to sinewaves is not directly related to its performance when subject to speech as input, so that the performance should be evaluated for speech inputs, eliminating conventional measuring techniques. The author developed a technique enabling the exact performance of a delta modulator to be determined for any input signal. This technique and the resulting hardware are discussed in this chapter.

The discussion applies to related systems such as pulse code modulation (PCM) as well as delta modulation.

#### 2.2 Review

There are many methods for determining the performance of a delta modulator.

Since some of the methods mentioned in this section are

not commonly used, all these methods are described in Appendix 1.

The methods can be grouped into two classes namely subjective methods and nonsubjective methods.

The subjective methods are:

- 1) Intelligibility tests, which evaluate how good one can understand speech subjected to the delta modulation process.

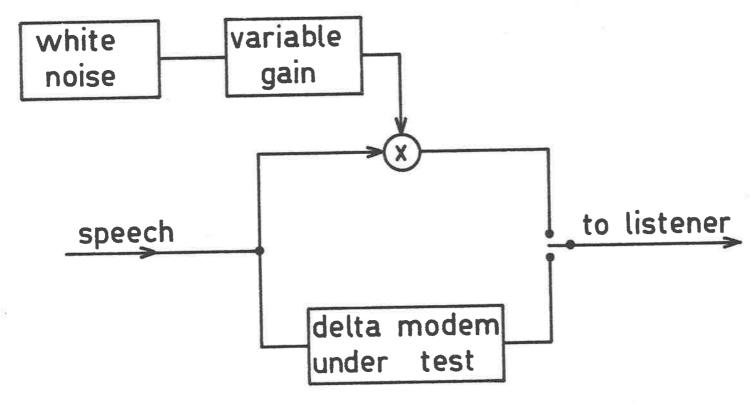

- 2) Equivalent white noise methods, which tests for the quality of the demodulated signal by comparing it with the input signal degraded by white noise.

Both these tests are useful when the delta modulator has an SNR of less than 20dB. Once the SNR becomes better than 20dB it becomes difficult to distinguish between the input and demodulated output so that the intelligibility score would be nearly 100%, regardless of whether the STR is 40dB or 20dB. Because these tests are subjective, care should be taken to eliminate or allow for the learning that the subjects may develop. Weapons Research Establishment (7) found that the subjects developed a skill at understanding the test words and the intelligibility score improved as time went on. The Australian Post Master General's Department Subjective Evaluation Group found that their test team developed a dislike to quantization distortion as time went on.

distortion measurements in audio equipment such as the Notch Filter method, the Frequency Analysis method and the Cancellation method. These methods are described in Appendix 1.

Since these methods measure distortion, they are also capable of measuring quantization distortion in delta modulation.

It should be pointed out that these methods are designed for equipment where limiting does not normally occur. It will be shown directly that these methods no longer give an indication of the performance of the equipment when limiting occurs.

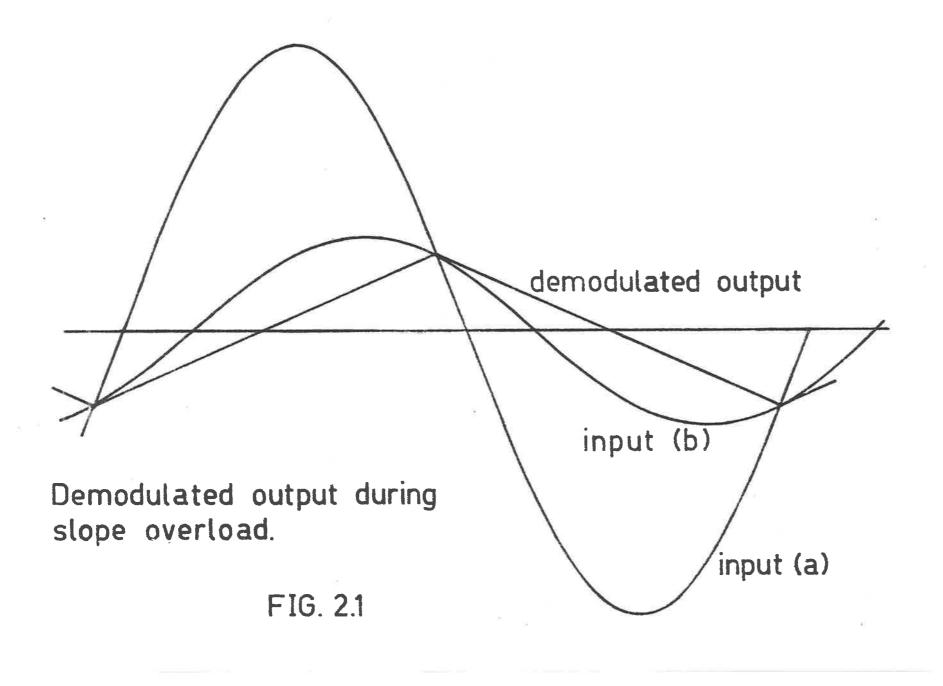

In delta modulation the dynamic range is normally small and slope overload occurs during a significant part of the useful operating range. When overload occurs the output signal is no longer proportional to the input signal, as is shown in fig 2.1.

Since the above methods use the output of the delta modulator to obtain a measure of the distortion, the quantization distortion will be the same for both input signals in fig 2.1. In one case the system is only just limiting, while in the other, severe overload occurs, and obviously the performance of the modulator is not the same.

When overload occurs, the above methods will no longer indicate a measure of the performance of the delta modulator.

# 2.3 Measurements of signal to quantization noise ratio for random input signals

Some of the work described in this section is also described elsewhere by the author (19). A copy of this publication is included in the thesis.

# 2.3.1 Definition of quantization noise

There are several definitions of quantization noise, each of which have their own merits.

The definition used in this thesis is as follows: Quantization noise is the difference between the input and demodulated output waveforms.

The gain and delay of a delta or pulse code modulator is independent of the amplitude and frequency of the input signal under non-overload conditions. If the gain and delay are assumed to be amplitude and frequency independent under overload conditions as well, one will obtain a different measure of the performance for both input signals in fig 2.1 as required.

The definition can thus be modified as follows:

Quantization noise is the difference between the input and demodulated output waveforms, provided the gain and delay of the delta or pulse code modulator are assumed to be independent of the amplitude and frequency of the input signal and the values of the gain and delay of the modulator are those corresponding to non-overload conditions.

It should be noted that the conventional methods mentioned in Appendix 1 do not assume the gain and delay of the delta modulator to be constant.

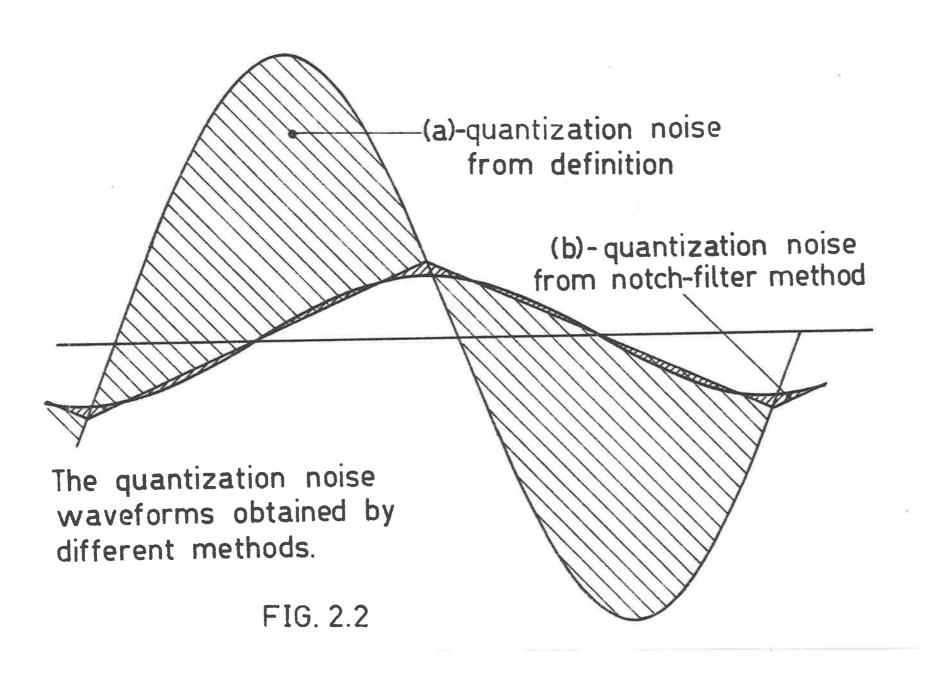

Fig 2.2 indicates which areas contribute to the distortion when the distortion is measured according to:

- (1) the above definition

- (2) the notch filter method

It can be seen that by using the above defintion, an indication of performance can be obtained even when the system is overloading.

# 2.3.2 Disadvantages of using sinewaves for measurements

The delta modulators investigated in this thesis are designed for use with speech.

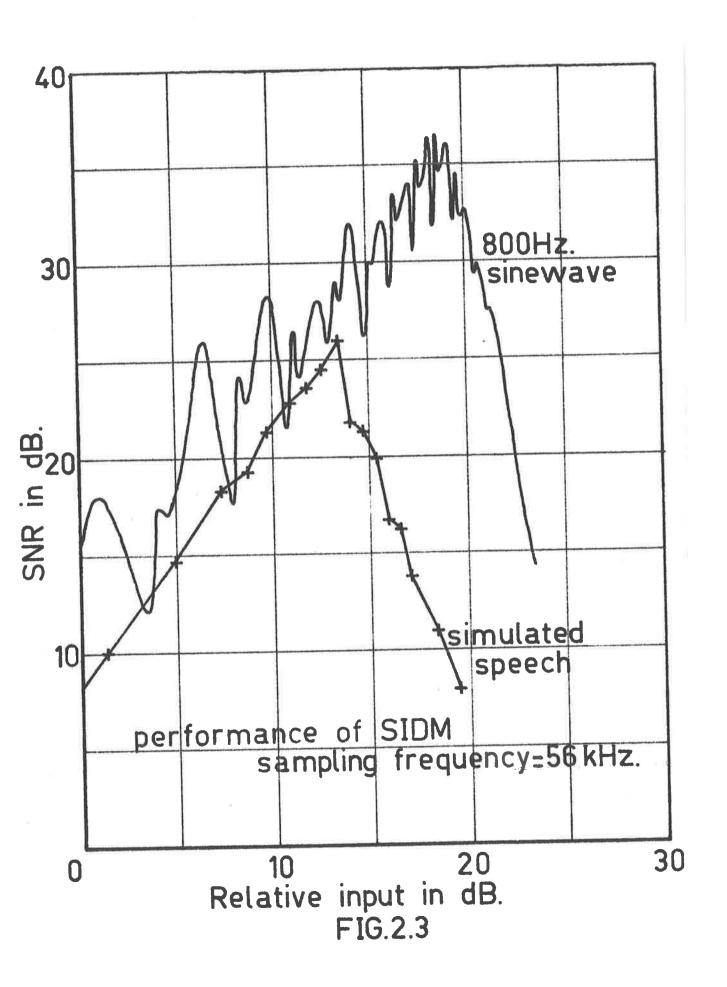

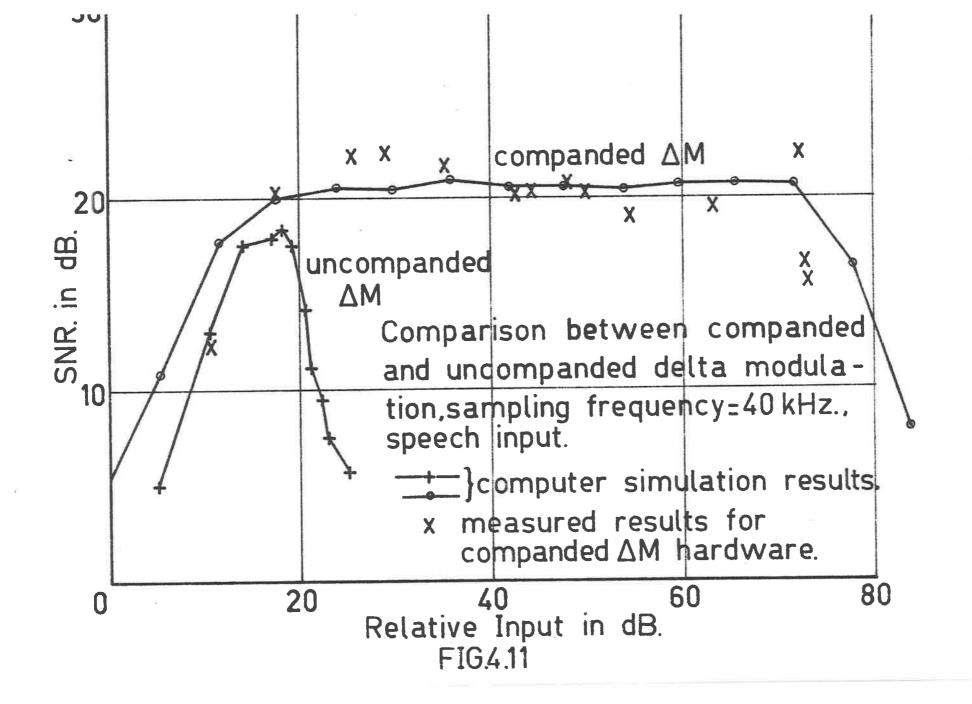

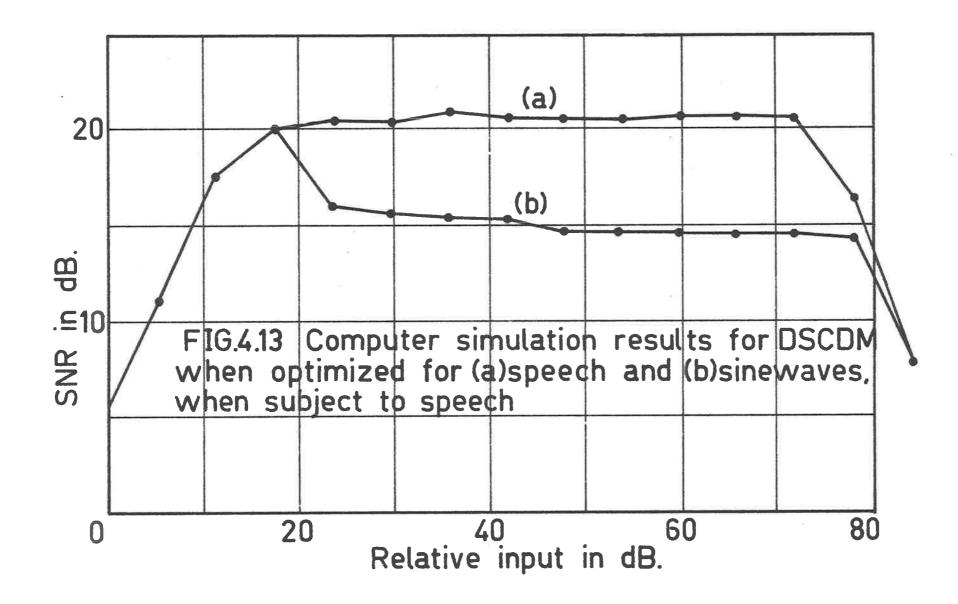

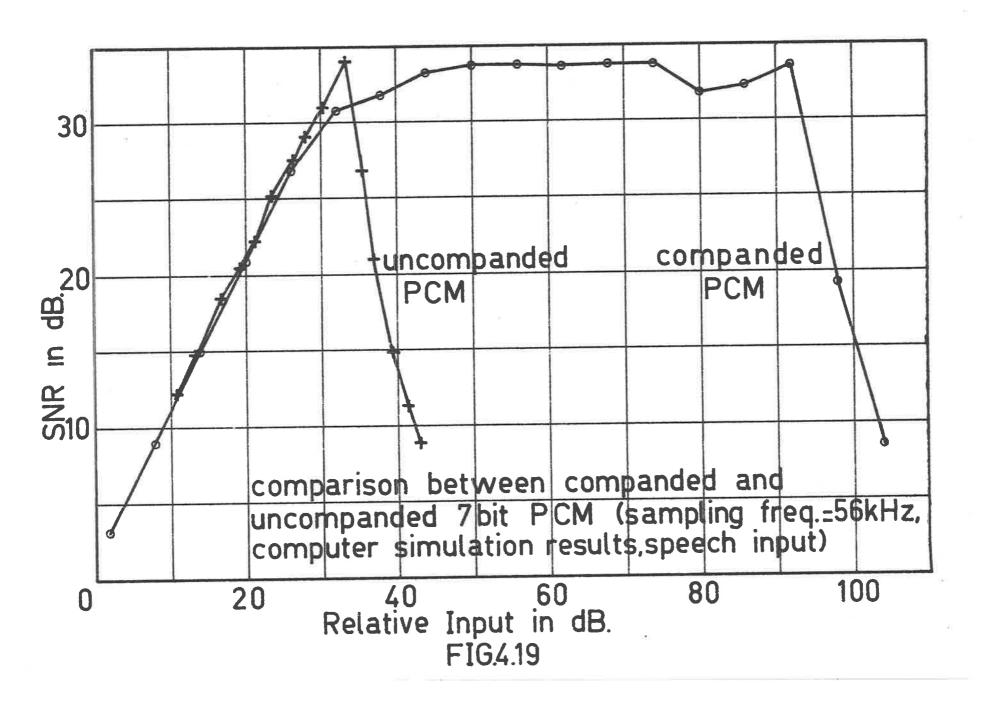

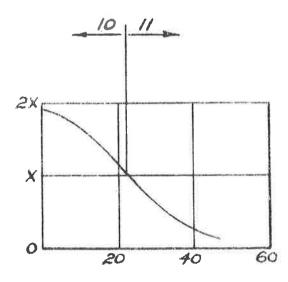

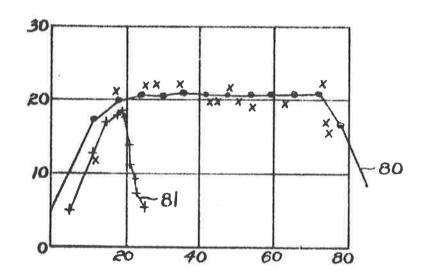

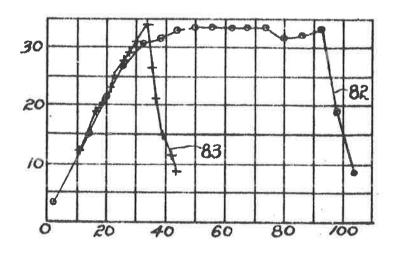

Since there are differences in the performance of a delta modulator when it is subject to an 800Hz sinewave input or a speech input, as is shown in fig 2.3 for SIDM, the testing should be done with speech as input. The results in fig 2.3 are obtained by computer simulation as discussed in chapter 5.

Furthermore the SNR of a nonlinear system such as a delta or pulse code modulator when subject to sinewaves need not be related to its performance when it is subjecj to speech, as is illustrated by the following 3 examples:

(a) A digital coder measures the frequency, and amplitude of a sinewave input, transmits this information in binary

form and at the receiver this information is used to set the amplitude and frequency of an oscillator. This system will have an excellent signal to quantization distortion ratio for sinewaves, but the performance when the system is subject to speech will not be good.

The example given above is extreme, it does however illustrate one of the differences between speech and sinewayes.

- (b) A delta modulator, employing syllabic companding has attack and decay time constants which are far too long so that when speech is used as input, the companding cannot follow the input power variations and the system is either overloading or operating near threshold. (i.e. at a small normalized input power) The performance of the system, when subject to sinewaves, will be good because the companding has sufficient time to adjust itself to the proper level. Schindler (18) indicates that the continuous delta modulation scheme used in France has this defect of improperly designed companding response times.

- (c) As shown in section 4.5.2 and fig 4.13 the normalized input power (which is defined in chapter 4 and <sup>(20)</sup>) at which the companding should operate is different for speech and sinewaves. This means that one can only obtain the best performance from a companded delta modulation system to be used with speech, if its companding is designed for speech. It is impossible to obtain the relevant information required

to design the companding from measurements using sinewaves.

This point is further discussed and illustrated in chapter 4.

None of the non-subjective methods previously mentioned can be used when a random input signal such as speech is used. The subjective methods require a team of listeners and normally the results cannot be repeated, due to the changing subjective standards of the team. Because of this and other practical and financial limitations, subjective methods have not been used in this thesis to evaluate the performance of delta modulators.

It is however possible to obtain a method for evaluation of the performance by either using control theory techniques related to nonlinear systems, or using the previous definition of quantization noise.

### 2.4 Measurement equipment description

#### 2.4.1 Theory

The quantization noise is defined previously as the difference between the input and output waveforms.

A frequency independent time delay will not affect the waveform. Since the delta modulator may introduce a delay, this delay has to be allowed for.

A gain, independent of frequency and amplitude will not affect the waveform and hence any amplification in the delta modulator must thus be allowed for also.

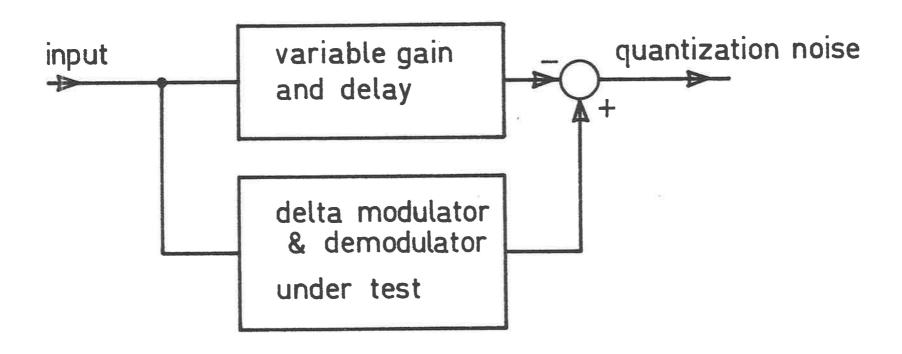

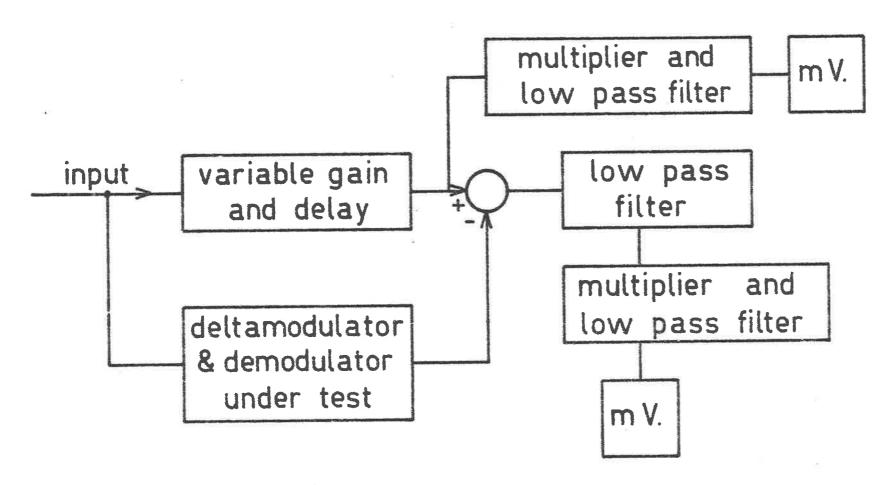

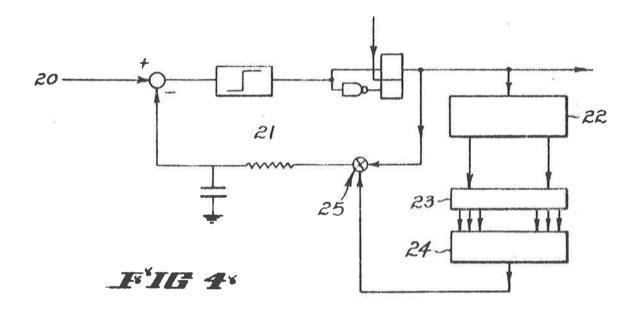

The block diagram in fig 2.4 shows equipment which will

FIG. 2.4 Method for obtaining the quantization noise.

evaluate the quantization noise as defined previously. In order to obtain the quantization noise, the gain and delay are adjusted such that the minimum difference signal is obtained when the delta modulator is not limiting. These then remain fixed for the rest of the measurements.

It should be realized that if sinewaves are used as input and no limiting occurs, the results obtained by this method will be exactly the same as those obtained by the cancellation method. There are however the following differences:

- (1) In the cancellation method, the gain and delay are adjusted continuously, while for the proposed method the gain and delay of the cancellation network are kept constant, so that when the modulator is limiting, the difference signal in fig 2.4 remains the quantization noise as indicated in fig 2.2 (a).

- (2) The cancellation network is frequency independent and any input signal, including speech, can be used.

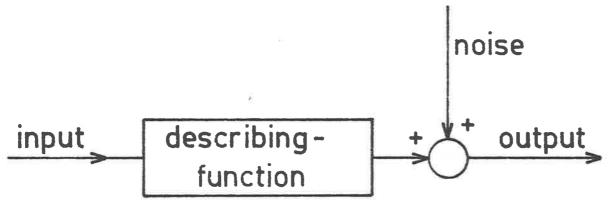

A second approach to the problem is as follows:

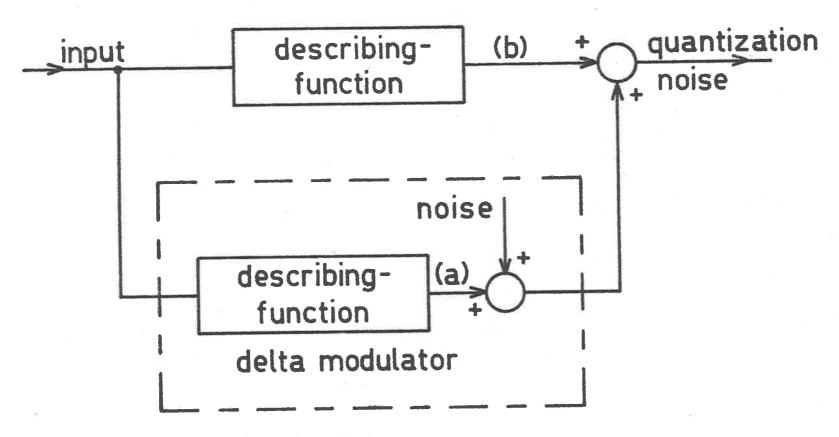

In control theory, a nonlinear element is usually represented by a linear describing function (21), plus a noise source as shown in fig 2.5 (a). A delta modulator contains nonlinearities, and can thus be represented similarly. A gain and delay which are independent of both frequency and amplitude, will not affect the waveshape. Since the object of the delta modulator is to reproduce the input waveform as

(a) block diagram of a nonlinear element

(b) block diagram of a delta modulator

FIG.2.5

closely as possible, the describing function should not alter the waveshape and the deviations from the input waveshape will will be due to the noise source. This noise is the quantization noise, according to the definition in section 2.3.1. The delta modem can thus be represented by the block diagram in fig 2.5 (b).

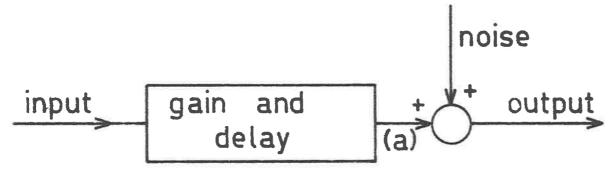

If we want to obtain the quantization noise, this can be done by using a cancellation network with a transfer function identical to the describing function of the delta modem, subjecting this to the same input signal as the delta modulator and subtracting the respective output signals, as is shown in fig 2.6.

Since the gain and delay of the delta modulator are not known in advance the gain and delay of the test equipment must be made variable.

### 2.4.2 Measurement of Power

The ultimate aim of the test equipment is to obtain a measure of the performance of the delta modulator under test which is hopefully indicated by the signal to quantization noise ratio. The SNR is normally expressed as a power ratio and in dB.

In the previous section a method was described which enables one to obtain the quantization noise. From this one can obtain the quantization noise power.

The signal power can be obtained from the input signal.

FIG. 2.6

Using the describing function to obtain the quantization noise

However since one is interested in the signal to noise ratio the gain of the delta modulator has to be allowed for.

The signal to be used for calculating the signal to noise ratio is the output signal from the describing function (i.e. at point (a) in fig 2.5 and 2.6). Unfortunately this signal is ficticious and thus unobtainable. When the test equipment is adjusted properly however the signal at point (b) in fig 2.6 is identical to the signal at point (a) which is the desired signal. The output of the cancellation network can thus be used to obtain the signal power.

The signal and quantization noise powers can be obtained by squaring and averaging the signal and noise voltages. The squaring can be achieved by using IC multipliers with the two inputs tied together. If speech is used as input signal, in order to minimise the effect of different power levels due to each syllable, a long averaging time typically between 10 and 100 seconds should be used.

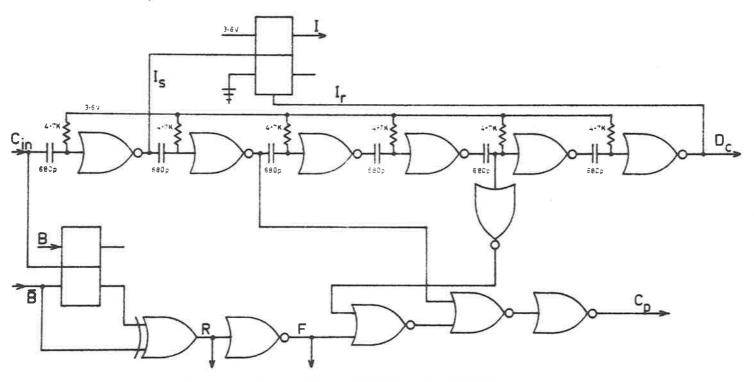

### 2.5 Hardware Description

The following section describes some aspects of the practical realization of the ideal concepts expressed in the previous section.

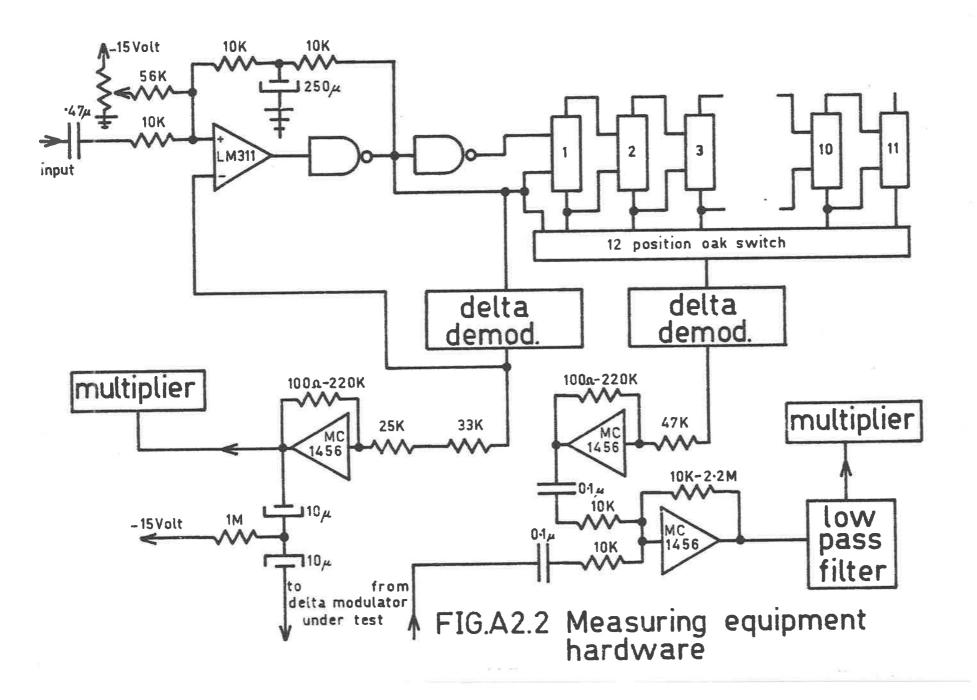

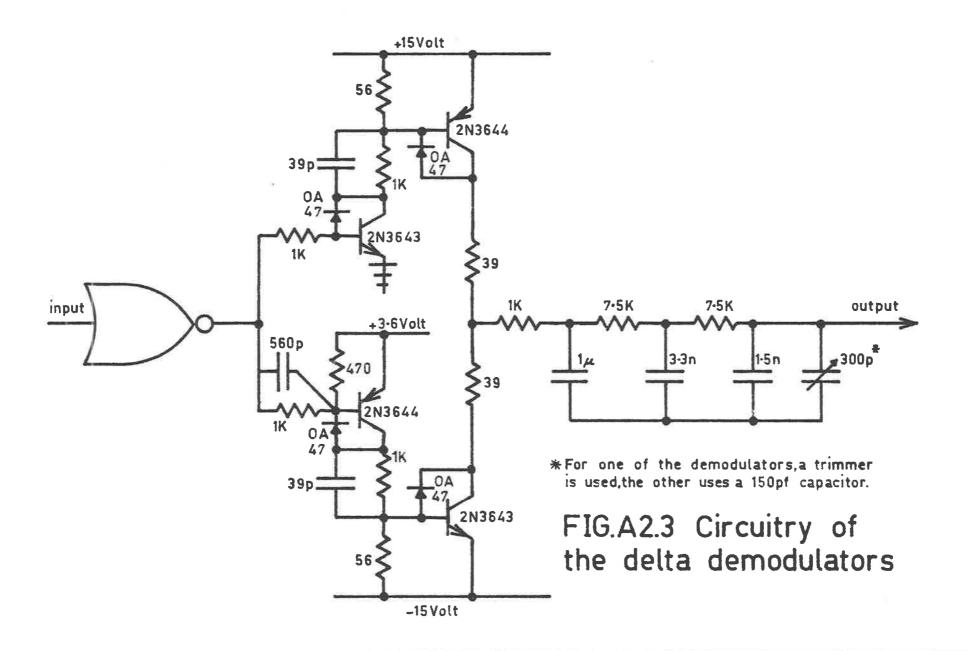

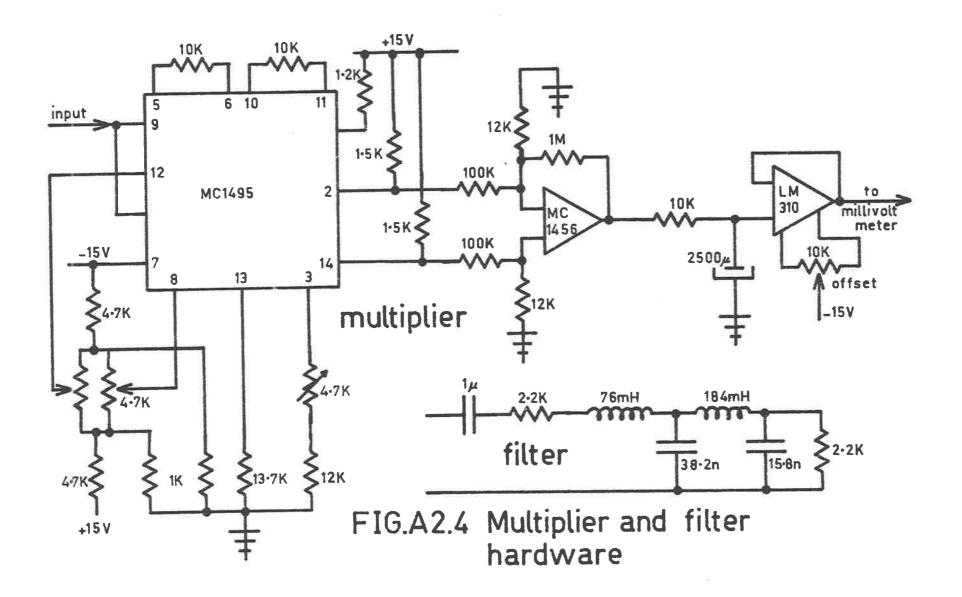

Since the details of the circuitry will vary depending on the availability of certain IC's, no circuit details will be discussed in the main text. They are however presented in Appendix 2.1.

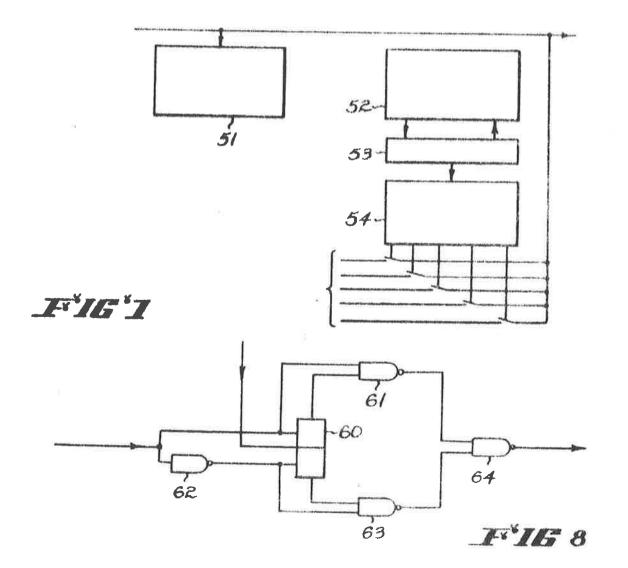

Some of the techniques used to obtain the required functions are worth mentioning. The block diagram of the equipment is shown in fig 2.7.

### 2.5.1 Tapped Delay Line

The easiest method of obtaining a variable delay is by the use of a tapped delay line. The delay line can either use:

- 1) analogue elements, such as a series of Bessel filters or a series of allpass networks. The time delay obtained by a series of RC networks is discussed in Appendix 4.3.

- 2) digital elements, such as a series of flipflops. The digital elements have the advantages that the per stage delay can easily be controlled. The disadvantage is however that the analogue input signal must be converted to binary signal.

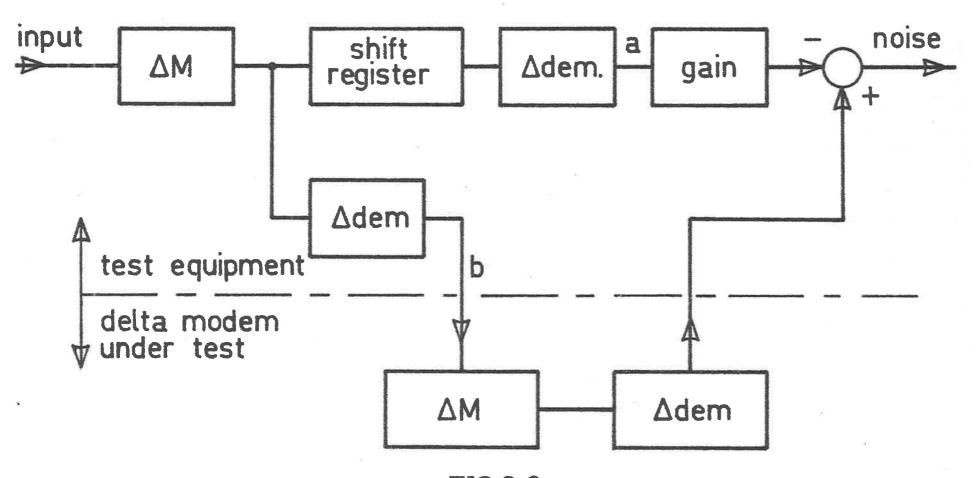

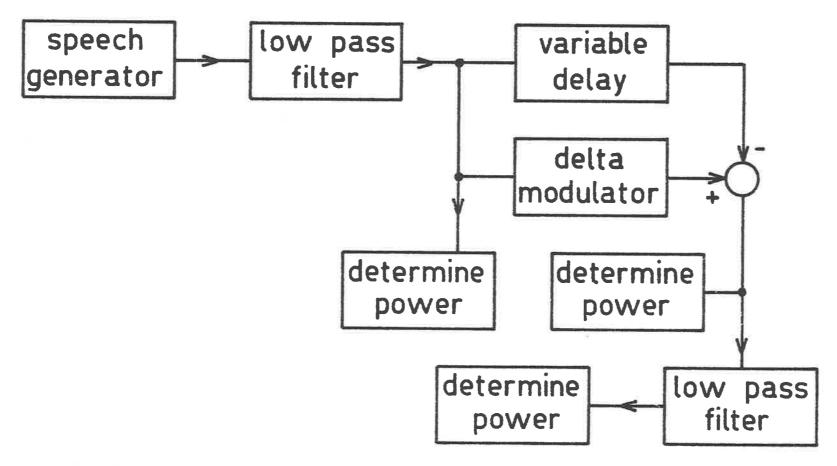

The easiest way to convert the binary signal into an analogue signal is by delta modulation, or delta sigma modulation <sup>(4)</sup>. This modulation process produces quantization distortion which must be allowed for. Fig 2.8 shows a block diagram of a system where 2 waveforms are produced, the relative delay of which can be varied. Furthermore since both the waveforms are obtained by the same process, the waveforms will be identical if the demodulators are matched properly, eliminating the effect of quantization distortion. The quantization distortion in each waveform is minimized by a high sampling frequency for

FIG.2.7

Block diagram of the measuring equipment.

FIG.2.8 Method for obtaining a variable time delay.

the delta modulator in the delay line. The undelayed output of the delay line can be used as input to the delta modulator or pulse code modulator under test and the delayed output can be used to compare with the demodulated output.

The resultant system will thus produce two identical waveforms, the time delay between which is variable and independent of frequency.

The above method was used in the construction of the test equipment. By careful matching of the delta demodulators and the lowpass filters, the difference between the waveforms at points (a) and (b) in fig 2.8 can be made less than 50dB below the signals at point (a) and (b), enabling SNR's of up to 50dB to be measured.

## 2.5.2 Power Measurement

When the research described in this thesis was started analogue multipliers were not readily available, so that the SMR was computed from the average rectified values rather than the RMS values. The results presented in (19) were obtained this way. (Obviously in order to compare the calculated and measured results, the STMR was evaluated by both methods during the computer simulation, but the error was found to be less than 1.5dB)

Recently IC analogue multipliers became available and test equipment was reconstructed using these in order to measure the actual signal and noise powers.

The output of these multipliers is filtered by the use of an RC network with a time constant of 25 seconds, giving the mean square voltage. This long time constant is necessary in order to eliminate variations of power due to pauses and syllabic variations in speech.

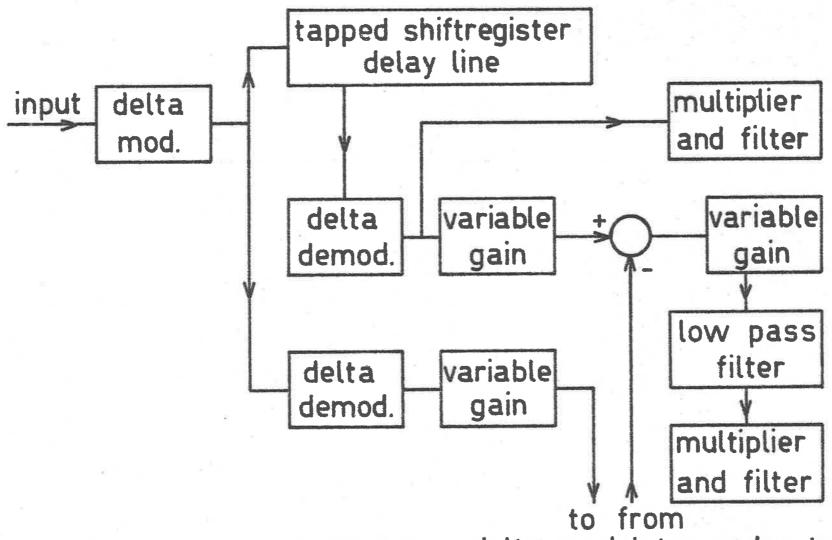

### 2.5.3 Accuracy Considerations

In order to reduce the effect of the quantization noise due to the delta modulator in the tapped delay line, this delta modulator is operated at nearly constant power, corresponding to the optimum performance. Any variation of signal power required for input to the delta modulator under test is obtained by the use of operational amplifiers after the delay line delta demodulators.

The gain of these amplifiers can be varied in approxim approximately 6dB steps over an 80dB range.

The quantization noise can also be amplified, so that the multipliers can be operated at a constant power level to obtain the most accurate results and to minimize the effects of drifts. The resultant block diagram is shown in fig 2.9.

Knowing the multiplier outputs and the gain of the amplifiers, the signal and noise powers and hence the signal to quantization noise ratio can be calculated.

## 2.5.4 Results

The results obtained with the measurement equipment are

FIG.2.9 delta modulator under test Final block diagram of the measuring equipment.

discussed in chapters 3 and 4, where the delta modulators developed during the research are discussed, together with a comparison with the calculated performance.

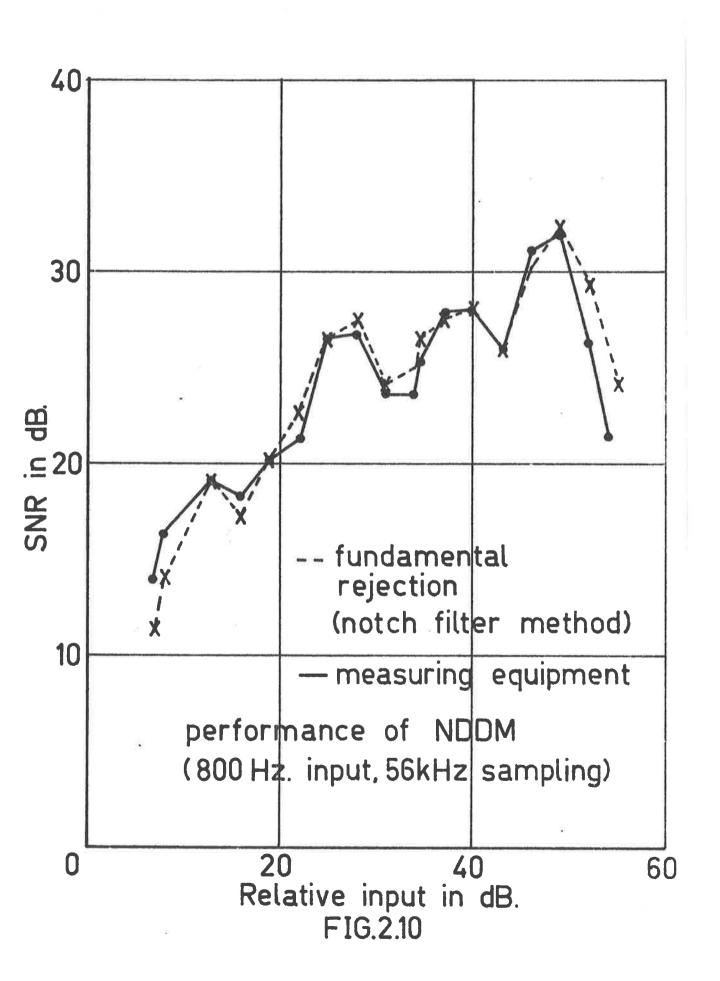

Fig 2.10 shows a comparison between the performance of NDDM which is described in the next chapter, obtained from

- (a) the notch filter method and

- (b) the measuring equipment.

The results can be seen to agree closely except for large input power, where the notch filter method gives optimistic results.

The differences at small input power are due to the background noise (switching spikes and thermal noise) causing a reduction in accuracy of the measurements.

### 2.6 Conclusions

This chapter has shown the desirability of testing a delta modulator or pulse code modulator, under actual operating conditions. If, as is common practice, a delta modulator to be used with speech is tested by using sinewaves, a misleading estimate of its performance can result.

Equipment has been developed which will enable the SNR of a delta modulator to be determined when this delta modulator is subject to random inputs such as speech. This equipment enables one to assess the performance of a delta modulator or pulse code modulator under actual operating conditions.

### CHAPTER 3

### THE DEVELOPMENT OF MONLINEAR DIGITAL DELTA MODULATION

### 3.1 Introduction

In this chapter the development, design criteria and the performance of nonlinear digital delta modulation (NDDM) are discussed.

Instantaneous companding is used in double integration delta modulation (DIDM) (2). However this makes the system less stable, causing a deterioration of the performance due to large amounts of overshoot. The use of digital techniques, together with nonlinear counting procedures enables instantaneous companding with good stability to be obtained.

Because the stability can be increased by the nonlinear counting developed by the author, the companding ratio and thus the dynamic range of NDDM is 30dB larger than those for the systems described by Abate (8) and Bosworth and Candy (9).

### 3.2 Instantaneous Companding

## 3.2.1 Principles of Instantaneous Companding

The dynamic range of a delta modulator can be increased by altering the gain of the local demodulator, to suit the input signal. This is known as companding.

Depending on the rate of change of gain of the local demodulator, the companding can be divided into 2 classes,

namely instantaneous companding and syllabic companding. In instantaneous companding, the gain is changed rapidly. For NDDM, the gain can change 40dB in 5 clockpulses and the delta modulator can thus track instantaneous variations of the input signal.

With syllabic companding, the gain is changed more slowly, so that the delta modulator can track variations of the average power.

Referring to fig 1.2 it can be seen that for single integration delta modulation (SIDM) which uses no companding, the change of demodulated output per clockpulse is fixed. This change in demodulated output is called the step size. Companding changes the step size. The step size is usually normalised to make the smallest step size unity.

A simple form of companding is used in DIDM <sup>(2)</sup>, by the use of 2 integrators in the feedback loop. However because the 2 integrators produce a 180° phase shift and a further delay is produced by the sampling process, oscillations can occur over a wide range of frequencies, often resulting in an audible output.

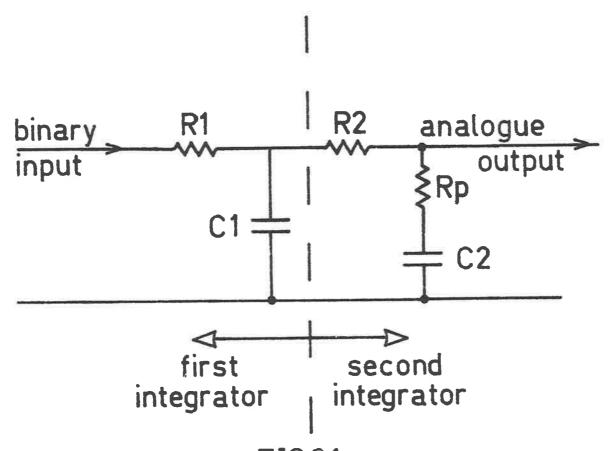

The stability can be improved by the use of what is known as "prediction", where the network in fig 3.1 replaces the 2 integrators in the feedback loop. The network no longer has a phase of 180° and by the proper choice of Rp, stable operation can be obtained.

From the description of DIDM it can thus be seen that

FIG.3.1

Double integration network with prediction

the usefulness of instantaneous companding is sometimes limited by a decrease in stability and the consequently large amounts of overshoot.

Other systems using instantaneous companding are described in section 1.2.2, but since NDDM was developed from DIDM in an attempt to overcome some of the disadvantages of DIDM, the principles of operation of NDDM will be compared with those of DIDM.

# 3.2.2 Dynamic Range Considerations

The step size of DIDM changes linearly with time as can be seen by comparing different step sizes in table 3.1. (The change in step size is related to the magnitude of the input voltage of the first integrator, which is the magnitude of the binary transmitted signal, which is constant. The step size is normalized to make the smallest step sizes plus and minus one, the difference between them is two.)

Consider an SOOHz input signal to a delta modulator with a sampling frequency of 56KHz. There will be about 18 clockpulses per quarter cycle and the maximum step size will be 36 (= 2 x 18). The companding ratio, which is defined as the ratio of the largest to the smallest step size, is thus approximately 30dB for an 800Hz input signal. The companding ratio is related to the dynamic range and if an extension of the dynamic range is required the companding ratio has to be increased.

TADLE 3.1

| Step           | SIDM | Step Size    | NDIM         |

|----------------|------|--------------|--------------|

| Number         |      | DIDM         |              |

| <del>-</del> 6 |      | ≈ <b>−11</b> | <b>-</b> 320 |

| <del>-</del> 5 |      | <b>-</b> 9   | -130         |

| <b>-</b> 4     | 100  | <b>-</b> 7   | - 44         |

| <b>-</b> 3     |      | <b>-</b> 5   | - 15         |

| <b>-</b> 2     |      | -3           | <b>-</b> 5   |

| -1             | -1   | -1           | - 1          |

| 1              | - 1  | 1            | 1            |

| 2              |      | 3            | 5            |

| 3              |      | 5            | 15           |

| 4.             |      | 7            | 44           |

| 5              |      | 9            | 130          |

| 6              |      | 11           | 320          |

(The step sizes for HDDM are discussed in section 5.3.2)

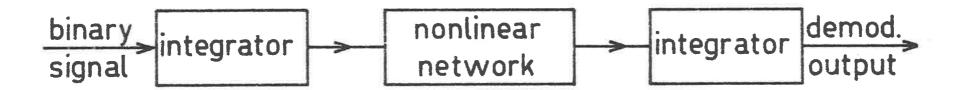

### 3.2.3 Monlinear Instantaneous Companding

The dynamic range can be increased by increasing the change of step size for large step sizes. This can however not be done by adding a third integrator, since this would give a phase shift of more than 180° and instability would result. Thus nonlinear methods must be used, as is indicated in fig 3.2.

The required nonlinearities can be generated by either analogue methods or digital methods. With analogue methods, diodes or other nonlinear devices are used to produce voltage dependant transfer functions, so that the change of step size can be made dependant on the step size. If the demodulated output from the local demodulator and the receiver demodulator are to be the same, the nonlinearities in the transmitter and receiver must be closely matched. Any mismatch will create distortion. Since diode characteristics depend on temperature and the transmitter and receiver are likely to be at different temperatures, a mismatch of nonlinearities will normally occur. Furthermore, supply voltage variations and a spread of component values will aggravate the problem.

These problems can be overcome by the use of digital techniques, where digital circuitry selects the step size to be used. Normally the information indicating an increase or decrease in step size is obtained from the binary signal. Since this binary signal is available at both the transmitter and receiver, the step size will be identical at the

The use of a nonlinear element to obtain instantaneous companding.

FIG.3.2

transmitter and receiver, provided no transmission errors have occurred.

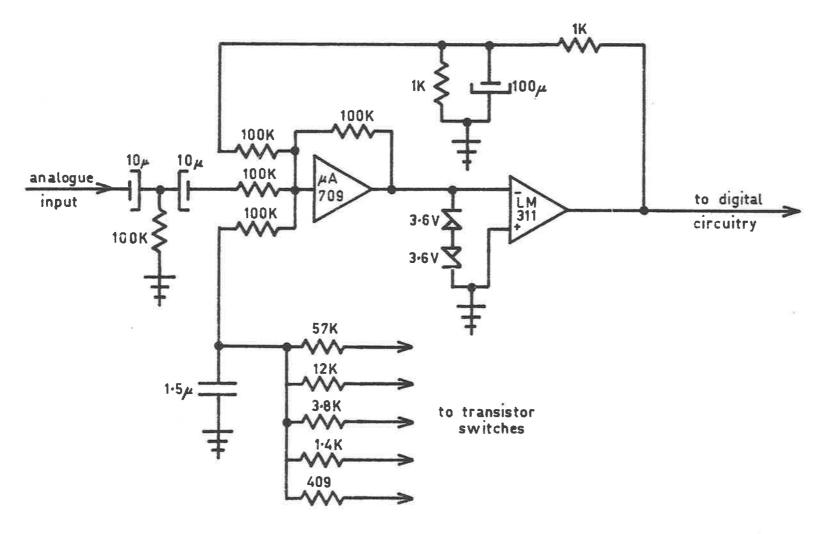

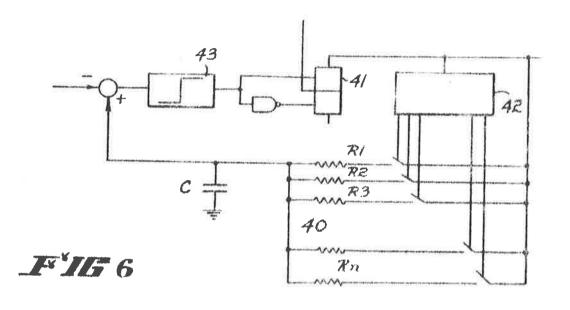

Because digital circuitry is used to select the step size, only a limited number of step sizes can be used. For DIDM at 800Hz and maximum amplitude, only 36 different step sizes are used, 18 positive step sizes and 18 negative step sizes, so that a finite number of step sizes can be used in practice. The local cemodulator can now be represented by the block diagram in fig 3.3.

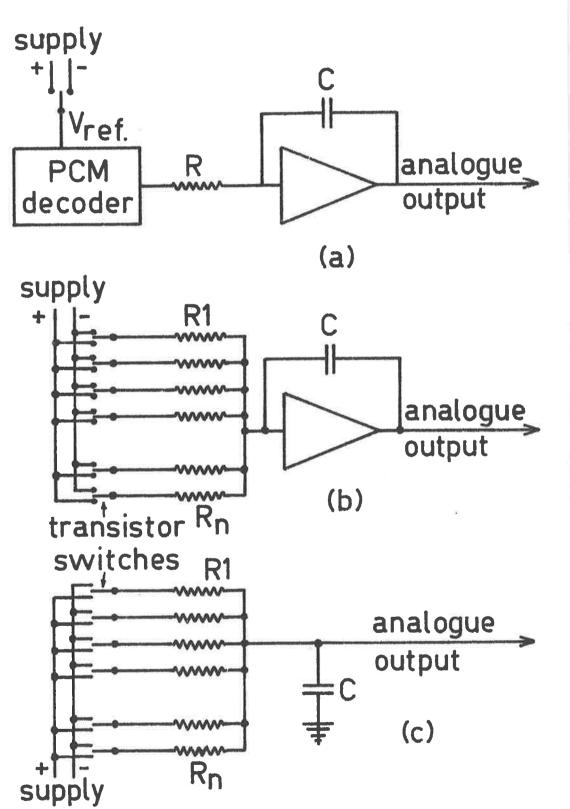

There are many practical ways by which this block diagram can be realized, 3 different methods are shown in fig 3.4. Referring to fig 3.4 (b) it can be seen that the step size is represented by a resistor, which is switched to either the positive or negative rail. Since each step size is represented by a resistor there are no limitations on step size and the step sizes can be optimized for the normal operating signal of the delta modulator, which is speech in this thesis.

Prediction will however generally no longer be sufficient to maintain stability. The stability of the delta modulator must thus be improved if the dynamic range is to be extended by this method.

## 3.2.4 Improvement of Stability

In section 3.2.1 it was stated that DIDM without prediction was unstable. A good test for stability is to

Block diagram of a demodulator with digital companding

FIG.3.3

Methods for obtaining digitally controlled companding FIG.3.4

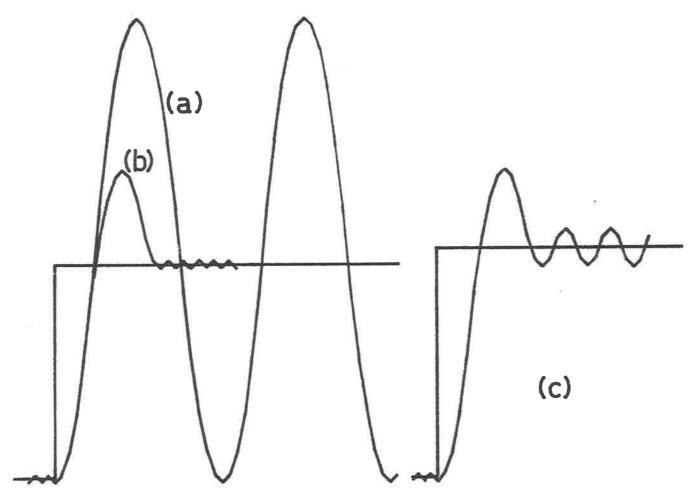

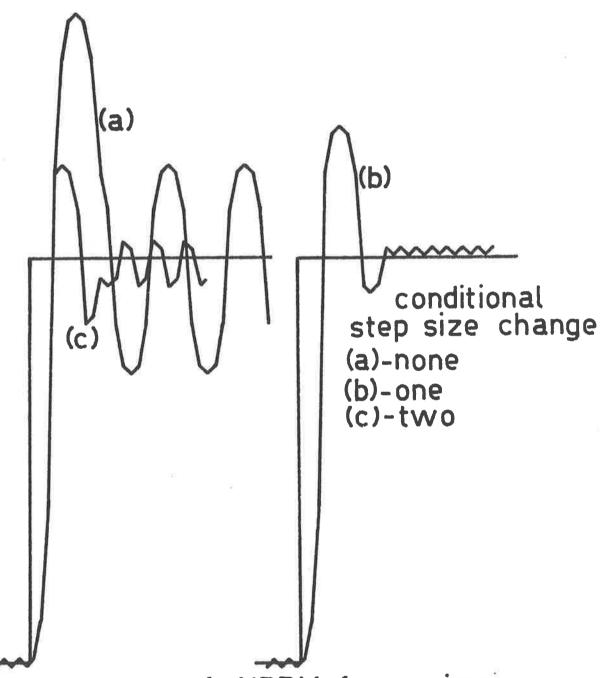

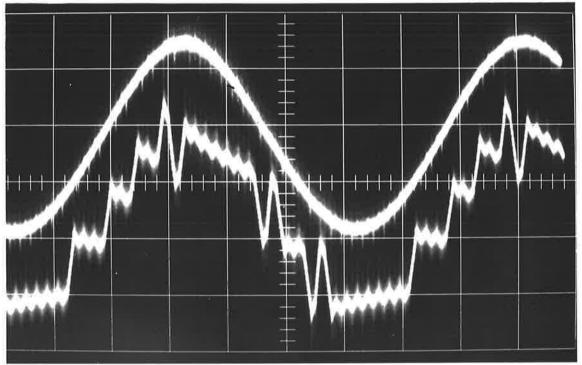

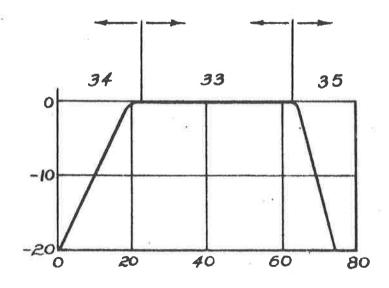

apply a step input to the delta modulator and observe the resulting demodulated output. Fig 3.5 (a) shows the step response of DIDM without prediction. It can be seen that the system is unstable. Fig 3.5 (b) shows the step response of DIDM with prediction. Oscillations can however still occur, as is shown in fig 3.5 (c)

In DIDM the step size is changed by a fixed amount during each sampling interval. The stability can be improved by changing the step size more than the normal 2 units when certain conditions occur.

From fig 3.5 (a) it can be seen that if the step size is reduced more quickly after the desired output voltage is obtained, i.e. after a change of the binary transmitted signal has occurred, the overshoot will be reduced. In other words if the step size is changed by X units, instead of 2 units, when a change of binary transmitted signal occurs, the stability of the delta modulator will be improved.

The idling pattern (10101010 etc.) has a change of binary signal occurring at every clockpulse. In order to minimize the quantization error, it is desirable to make this idling pattern correspond to the minimum step size, i.e. ± 1.

If the step size is changed by X units at every change in binary transmitted signal, the idling pattern will correspond to the step sizes  $\pm$  X/2 while the required step size is  $\pm$  1.

A further condition must thus be satisfied namely: If

Step response of double integration delta modulation,(a)-without prediction and,(b) and (c)-with prediction

FIG.3.5

the change in step size results in a step size of opposite sign to the previous step size, the new step size is the smallest step size of opposite sign to the previous step size.

If for instance the step size is + Y units and it is reduced by X units, where X)Y, a negative step size results and the step size used is not Y-X units but -1. This rule will achieve the required idling pattern.

Fig 3.6 shows the step response of DIDM with conditional nonlinearities when the step size is changed by 4,6,8 and 10 units when the previously mentioned conditions are satisfied. Comparing fig 3.6 with fig 3.5 (a) it can be seen that the stability has been increased. The step response in fig 3.6 is evaluated for nonlinear counting without prediction and oscillations can still occur. Absolute stability will be obtained if prediction is incorporated as well, enabling the companding described in section 3.2.3 to be implemented.

### 3.2.5 Error Performance

In a practical delta modulator system, transmission of cerrors will occur. It is desirable to minimize the effect of transmission errors. A compromise must however always be made. As the performance of the delta modulator is improved, the information contained in the binary signal must increase, so that the redundancy in the binary signal will decrease

Step response of DIDM with conditional nonlinearities. The conditional change is indicated by the numbers

FIG.3.6

and the effect of errors will increase.

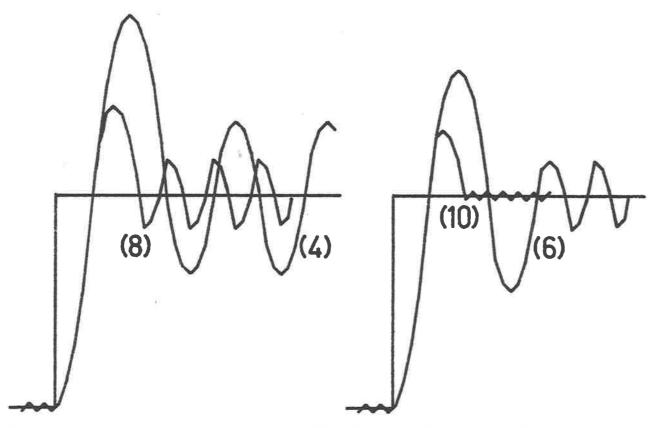

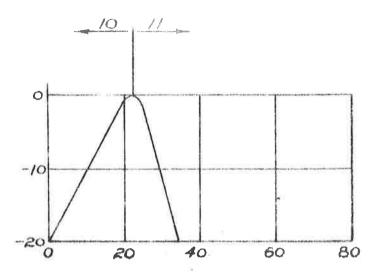

For the delta modulator to be useful however, the effect of a transmission error must diminish with time, i.e. the error caused by a single transmission error must not persist indefinitely. Fig 3.7 (b) shows the effect of a single transmission error on ideal SIDM and DIDM systems.

For SIDM the error causes a DC shift in the output signal, which will not produce a lasting audible effect since the ear is not sensitive to absolute pressure even if the reproducing system were capable of responding to it. For DIDM the error causes a bias on the step size, which causes the output to increase until limiting occurs in the hardware, making the system useless. The first integrator in the DIDM system must be leaky, so that the effect of errors diminish with time. Since it is intended to replace the first integrator with digital circuitry, leakyness must also be incorporated in the digital circuitry. Leakyness causes a gradual decrease in magnitude of the step size if a 1010 etc. binary pattern is applied, until the step size ± 1 are obtained. The required leakyness can be achieved by changing the step size by X units only when the magnitude of the step size is decreased as well as satisfying the previous requirement of a change in binary signal. This further requirement will not change the step response indicated in fig 3.6.

Fig 3.7 (b) shows that the effect of a transmission error decreases with time, as required. The resultant DC offset

Effect of a transmission error FIG.3.7

does not effect the performance markedly since firstly, the ear is insensitive to absolute pressure and secondly, the DC error will decay if analogue integrators are used for the second integrator, since all analogue integrators have a finite leakyness and thus a finite memory. Comparing fig 3.7 (b) and fig 3.7 (a) it can be seen that because each transmitted bit carries more information due to the companding, the effect of a transmission error for MDDM is worse than for SIDM.

The resulting system, incomporating the features mentioned in sections 3.2.3, 3.2.4 and 3.2.5 is called Monlinear Digital Delta Modulation (MDDM).

# 5.2.6 Summary of Companding Strategy

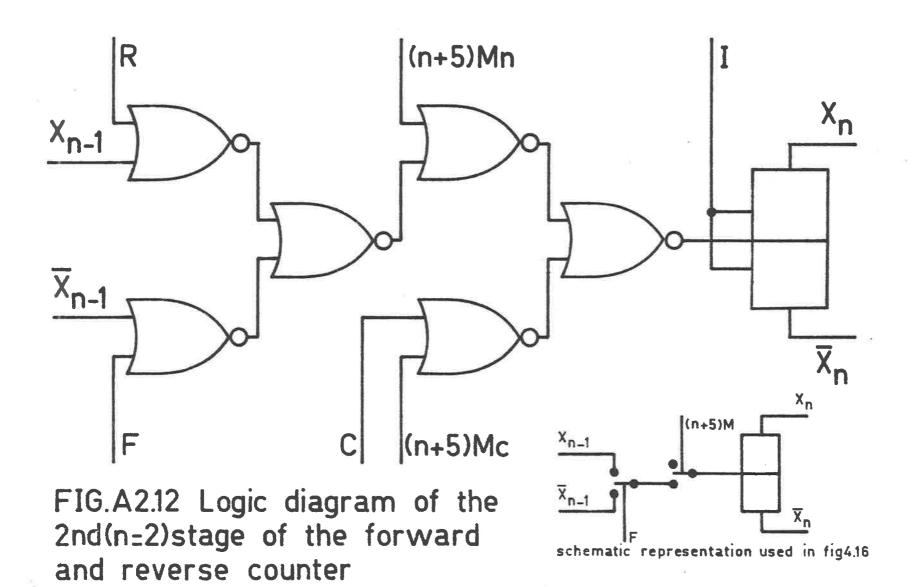

The requirements outlined in sections 3.2.4 and 3.2.5 can also be written in terms of step numbers instead of step sizes and it can be seen from table 3.1 that this has some advantages when the step sizes are varied as proposed in section 3.2.3. Changing the step size by X units now corresponds to changing the step number by  $N_{\rm X}$  units.

The companding strategy will now become as follows:

- (1) The step number is controlled by the binary transmitted signal.

- The step number is increased if the binary signal is a one and decreased if the binary signal is a zero.

- (2) The magnitude step number is increased by one if no

- change in binary transmitted signal occurs at the clockpulse concerned.

- (3) The step number is changed by  $N_{\rm X}$  units if a change in binary signal occurs and the magnitude of the step size is decreased as a consequence of this change, provided that if a change in the sign of the step size occurs, the new step size becomes the smallest step size of the opposite sign to the previous step size.

## 3.3 Optimization

# 3.3.1 Aims of Optimization

In the previous section a new type of delta modulator denoted as NDDM was proposed, removing some of the restrict restrictions placed on DIDM. There are 4 basic variables that must be chosen, each of these will have an effect on the performance. The following questions must be answered:

- 1) Prediction: Is prediction to be used and if so how much?

- 2) Stabilization: By how much does the step number have to change on a change of binary signal to obtain the best performance?

- 3) Step sizes: Which step sizes give the best performance?

- 4) Leakyness in the Integrator: How much leakyness is required for the best performance?

It is difficult to optimize all of these quantities, since each one will affect the other. For example if a large change in step size occurs, more stabilization is required to keep the system stable.

The relative ratio of the step sizes will depend on the specific application of the delta modulator.

A compromise between STR and dynamic range must be made and the optimization must then be carried out to maximize the performance according to the criteria specified.

For NDDM it was decided to use simulated speech and to optimize the step sizes such that a flat SNR curve is obtained over as wide a range as possible. Alternatively it is possible to select the step sizes such that the highest possible SNR is obtained from the delta modulator.

### 3.3.2 Selection of Parameters

#### 1) Prediction

Since prediction increases the stability of the delta modulator, without significantly affecting the performance of the delta modulator, prediction was used in MDDM. A prediction of one clockpulse was used, which is the same amount of prediction as is usually used in DIDM and means that the voltage across the prediction resistor corresponds to the step size, so that the output from the local demodulator is a stepsize more than the output from the demodulator at the receiver.

### 2) Stabilization

Increasing the stabilization by increasing the change in step number when a change in binary signal occurs, normally increases the grannulation noise i.e. the quartization noise. The increase in stabilization will however reduce the overshoot due to rapid changes of the slope of the input signal and will thus reduce the slope overload noise. A compromise must thus be made between slope overload and grannulation noise. For the optimization, a change of 2 steps on a change of binary sign was chosen since this gives sufficient stabilization without increasing the grannulation noise too much. After optimization of the step sizes, the above assumption can be checked to make sure that the best performance has been obtained.

### 3) Step Size

The step sizes were obtained by successive optimization.

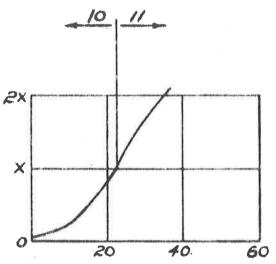

If the required step sizes are  $\pm$  1,  $\pm$  A,  $\pm$  B,  $\pm$  C,  $\pm$  D,  $\pm$  E, etc., one must find A,B,C,D, etc. such that the best performance is obtained. The constants A,B,C,D etc. are obtained by successive optimizations. This optimization was carried out using computer simulation, as described in chapter 5, with simulated speech, without syllabic variations of power, as input. A flat SER curve over as wide a dynamic range as possible was aimed for. This optimization resulted in the step sizes indicated in table 3.1. From the computer simulation it was found that each step size affected the

performance of the modulator only over a narrow range of input power and that there is little interaction between the step sizes, so that the optimum performance can be obtained by successive optimization. No improvement in performance could be obtained by using more than the 12 step sizes indicated. The step sizes ± 320 only resulted in a marginal increase in dynamic range (2dB) and were not incorporated in the hardware, because the extra complexity was not justified by the marginal increase in performance.

After the step sizes are obtained, one can check whether the correct stabilization is chosen. Fig 3.8 shows different stabilization applied to NDDM with the step sizes as in table 3.1. It can be seen that adequate stability is obtained if the step size is changed by two steps instead of one for a conditional nonlinearity, so that the initial assumption is correct.

## 4) Leakyness in the Second Integrator

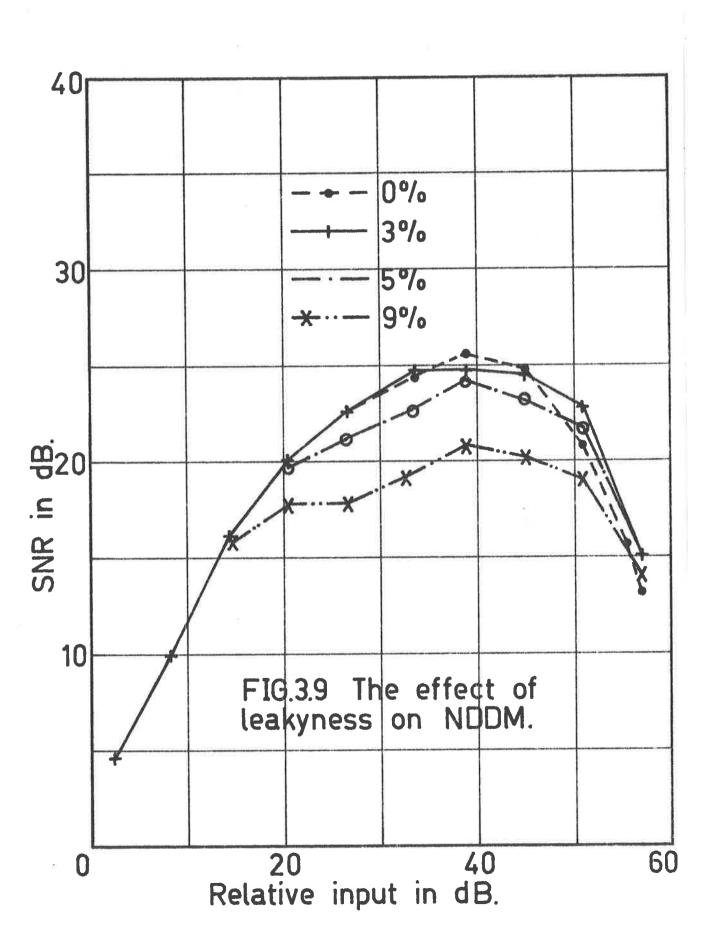

The optimum amount of leakyness in the analogue integrator must now be determined. This again must be a compromise. As leakyness is increased the performance will decrease but the tolerance to errors will increase. Fig 3.9 shows the effect of the leakyness on the performance.

The leakyness is expressed as a percentage, indicating the percentage decay during one sampling interval. A leakyness of 3% was chosen since this gives a good SNN and also a reasonable tolerance to errors.

Step response of NDDM for various nonlinearities FIG.3.8

#### 3.3.3 Accuracy Considerations

The optimization was carried out by means of computer simulation using the Control Data Corporation (CDC) 6400 at the University of Adelaide. Because of cost limitations, the program time was kept as short as possible. The simulation was carried out in the time domain, so that only a relatively small number of sampling intervals could be studied and from the performance of the delta modulator during this interval a judgement on the overall performance of the delta modulator could be made.

A compromise was necessary between the cost of running a longer program and the inaccuracy of the performance that a shorter program would give.

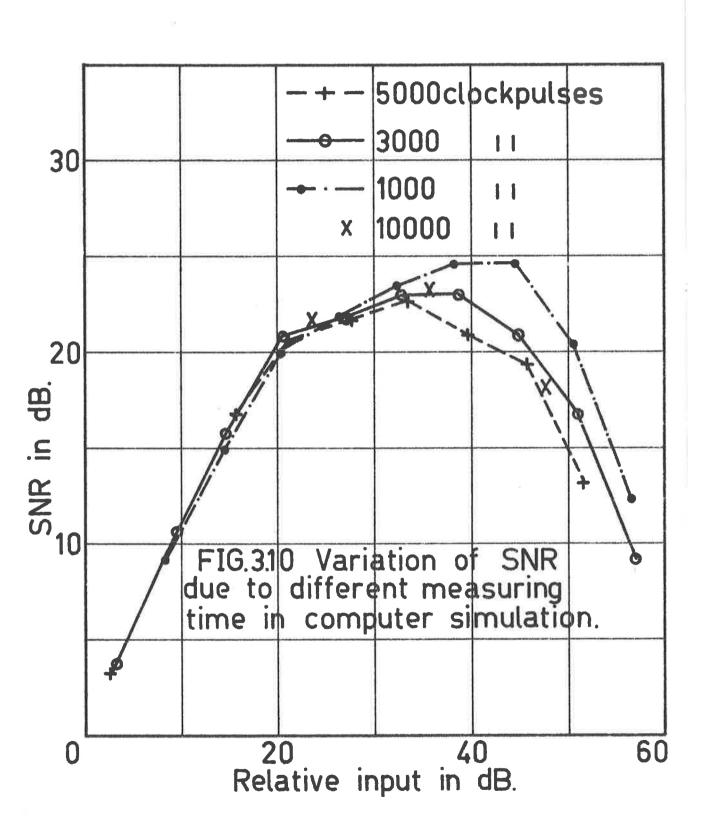

The program time can be split up in 2 sections, firstly, a period for initialisation, to allow the steady state performance to be obtained and secondly, the period during which the performance is evaluated. Fig 3.10 shows the effect of different intervals during which the performance is evaluated. It can be seen that 3000 clockpulses enable the performance to be evaluated with reasonable accuracy. Since 3000 clockpulses at 56 KHz sampling frequency corresponds to approximately 0.05 sec., one can expect variations of the SNR to occur.

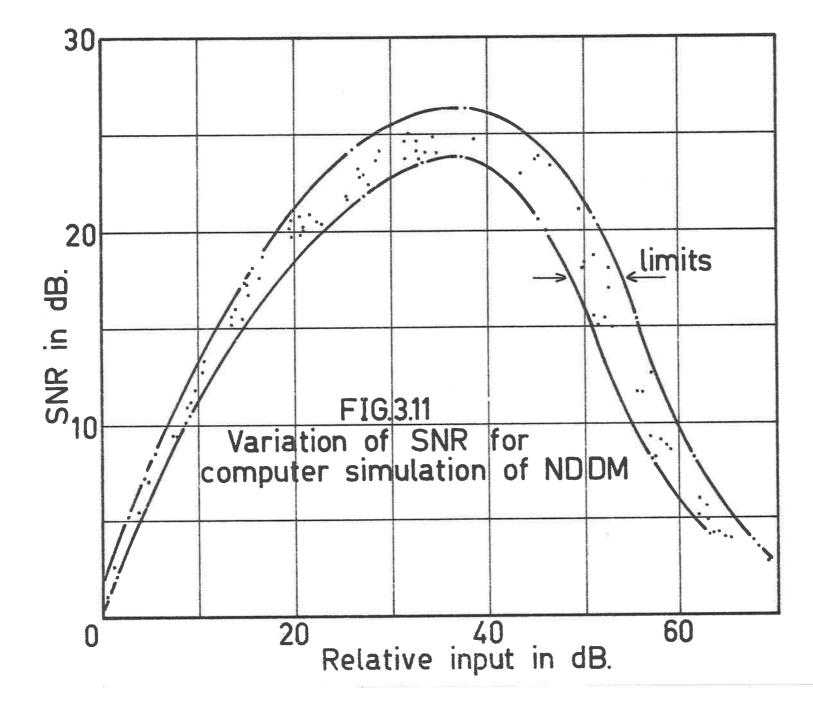

Fig 3.11 shows the variations in SIM that can be obtained when using 3000 clockpulses to calculate each point. It can be seen that for most of the dynamic range the results

are within  $\pm$  1dB of the mean SMR curve, while all points are within  $\pm$  2.5dB of the mean SMR curve.

From this wide variation in SIR due to different signal conditions it is apparent that no exact optimization can be carried out, since the optimization for one particular time segment will be different from the optimization for another time segment. It can however be seen that the optimization is sufficiently accurate to give a good performance over a wide dynamic range.

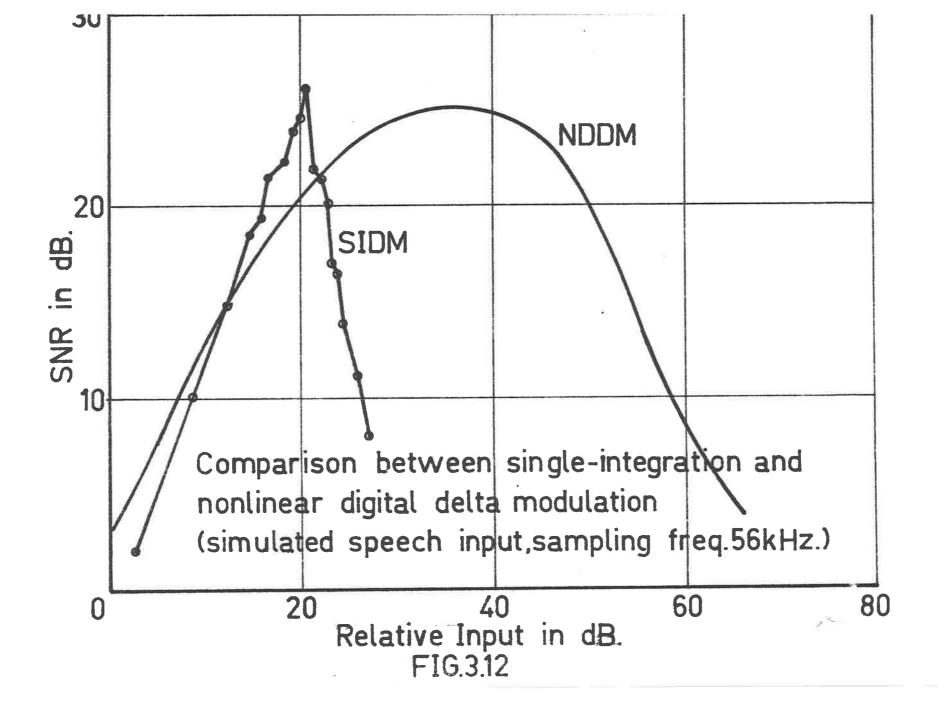

Fig 3.12 shows a comparison between SIDM and 1000M, obtained by computer simulation, when simulated speech is used as input for both. It can be seen that by using the instantaneous companding the dynamic range has been increased.

# 3.4 Practical Realisation

## 3.4.1 Hardware

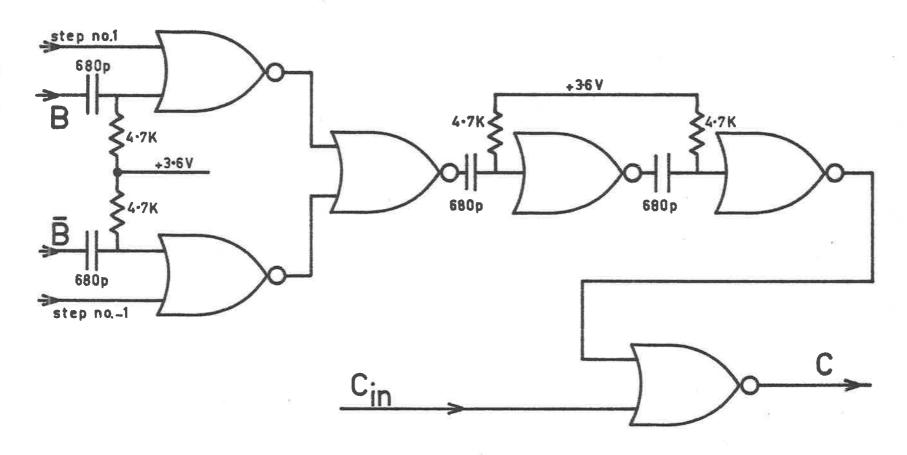

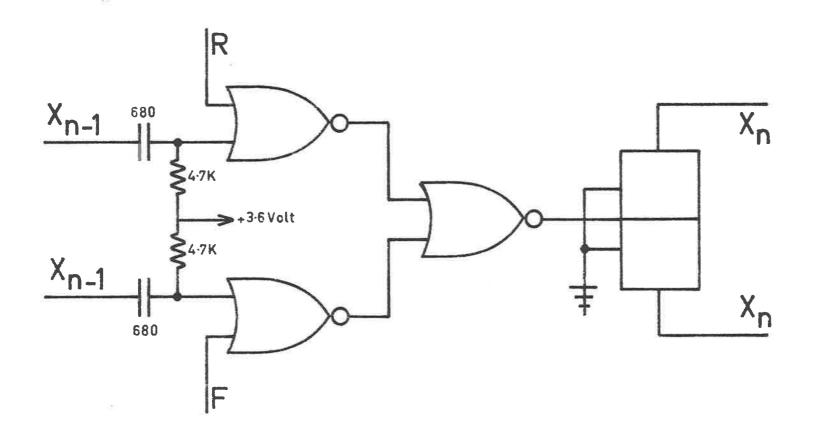

In the previous section the required switching strategy was stated as follows:

The step number is changed by 2 units instead of the normal one unit when a change in binary signal occurs and the magnitude of step size is reduced as a consequence of this, provided no change in sign of the step number occurs. The step number will be changed by one unit, if the above conditions are not fulfilled.

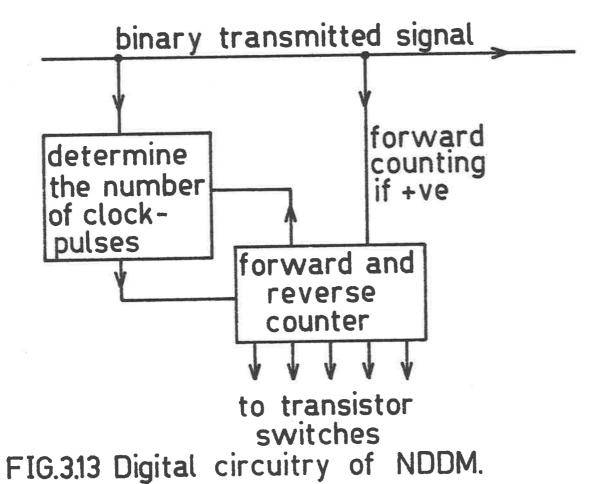

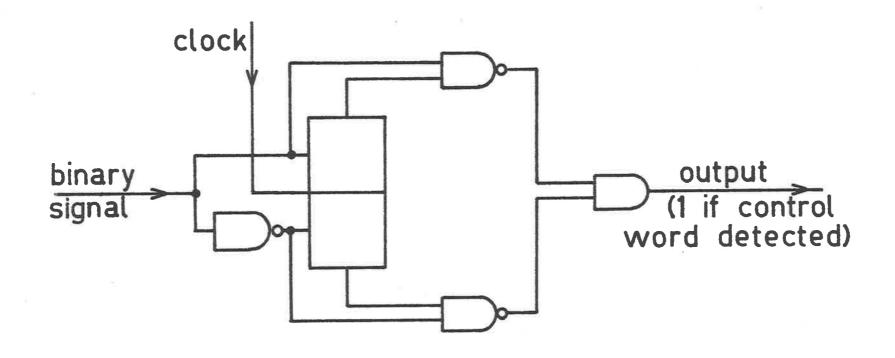

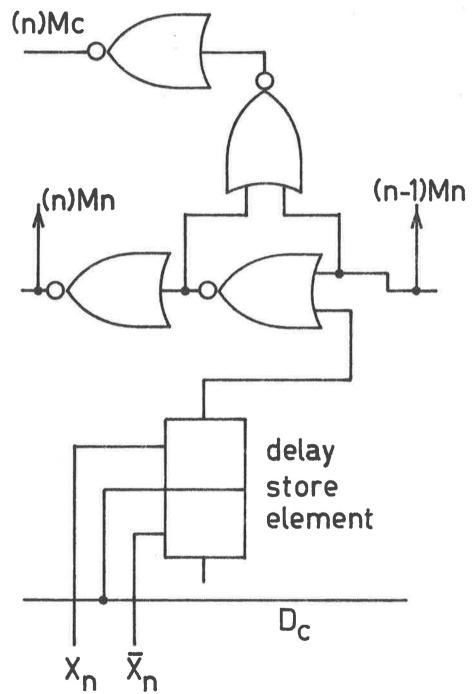

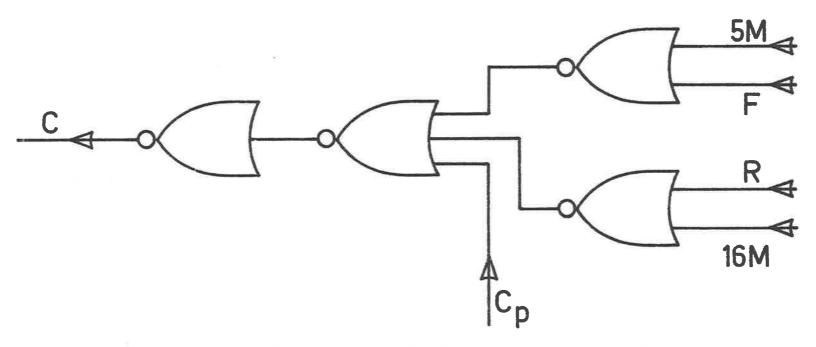

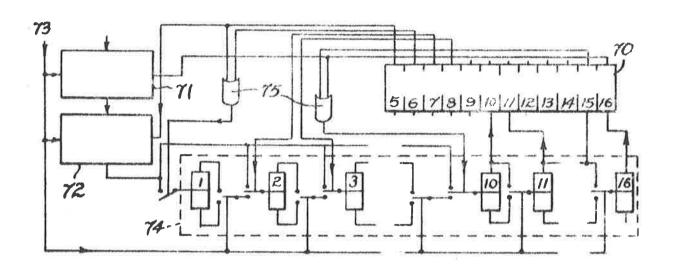

The block diagram of the digital circuitry is shown in

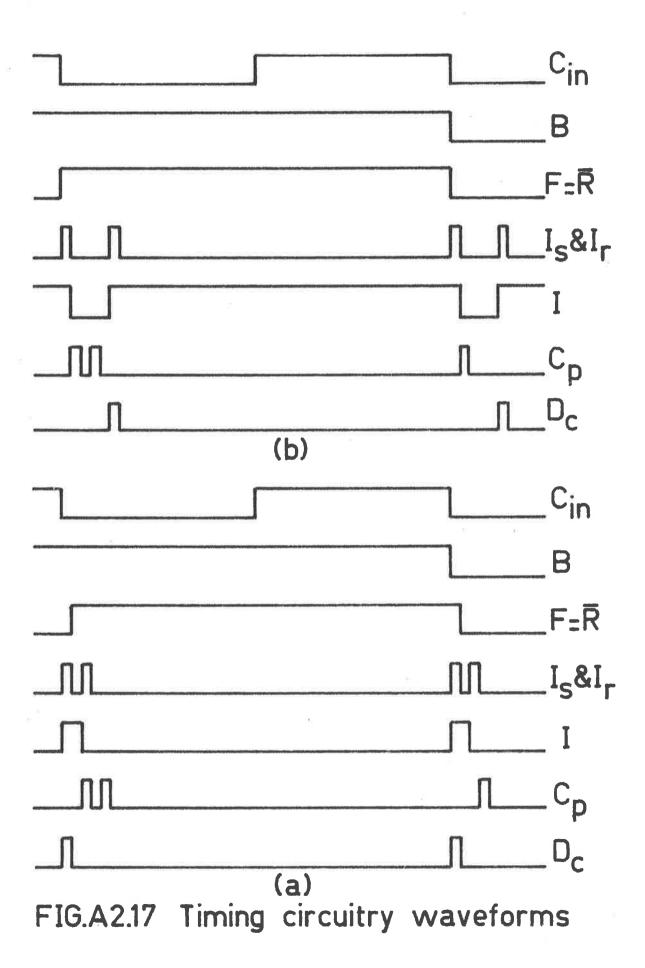

fig 3.13. The following action occurs at the sampling instant:

- 1) The binary transmitted signal is compared with the previous binary transmitted signal and a signal is produced if a change has occurred. The new binary transmitted signal also sets the counter to either forward or reverse counting.

- 2) A decision is made whether one or two step changes are required, this information is then stored in a .flipflop.

- 3) Two pulses are generated and depending on the condition of the flipflop mentioned in (2) one or both are passed into the counter, setting the new step size.

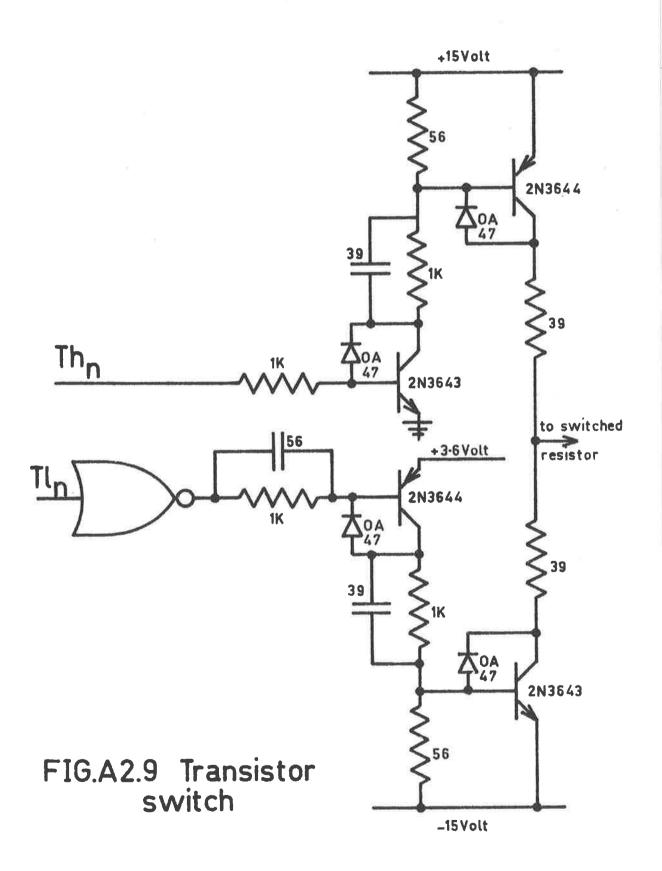

The decoders control the step sizes by means of transistor switches as indicated in fig 3.4(c). For proper operation, the time taken to do steps (1) to (3) above should be much smaller than the sampling interval.

The complete circuit diagram is given in Appendix 2.3.

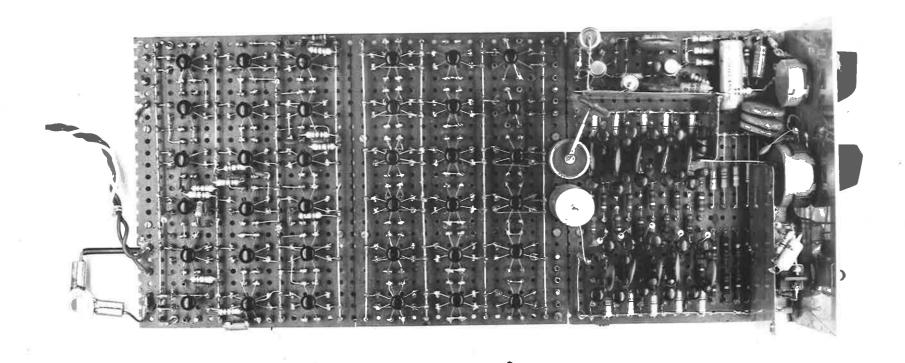

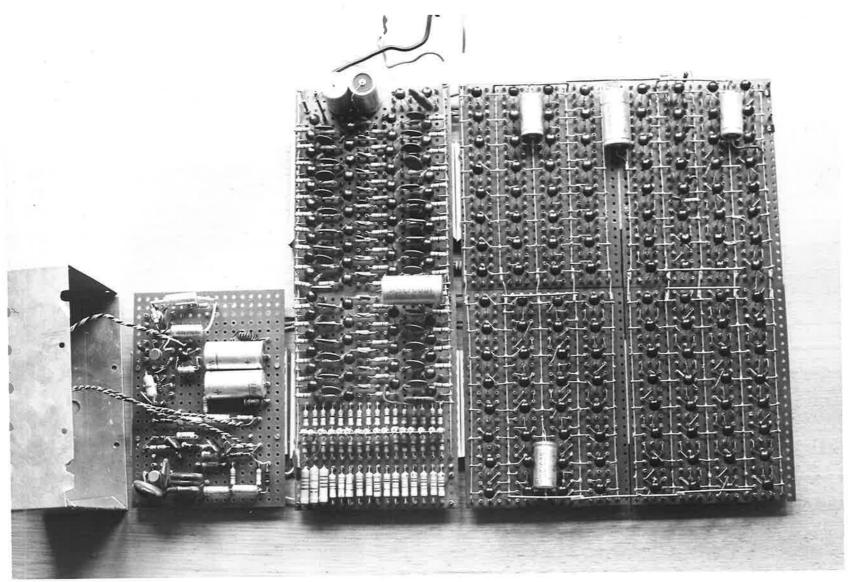

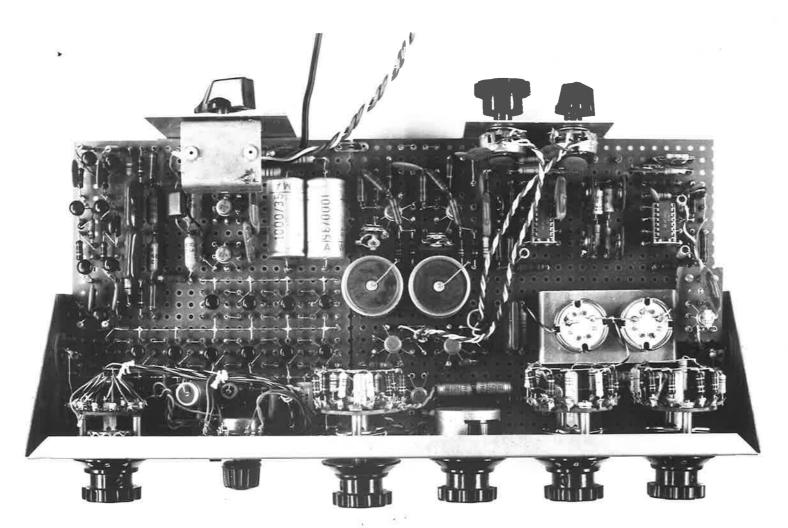

Fig 3.14 shows a photograph of the hardware for the modulator.

The demodulator is of similar complexity.

# 3.4.2 Results

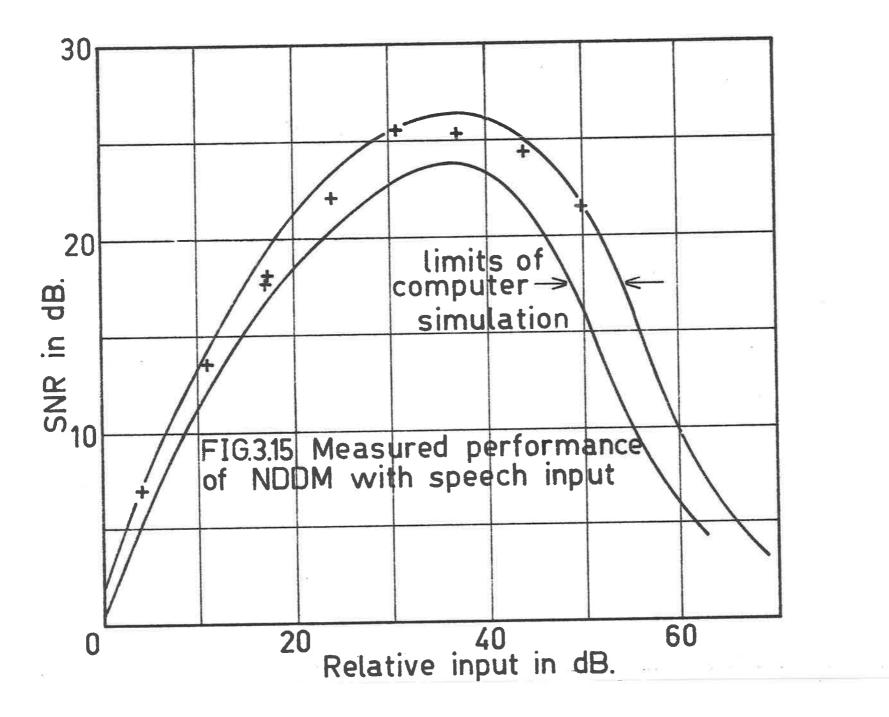

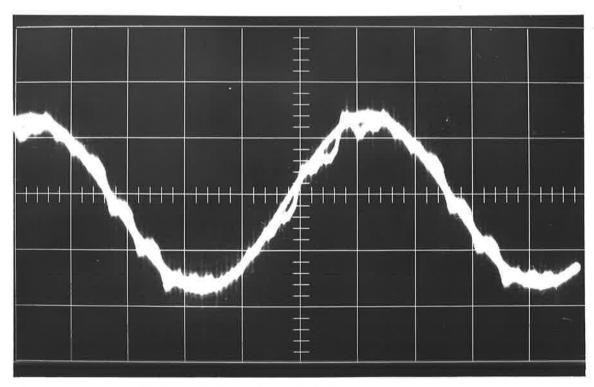

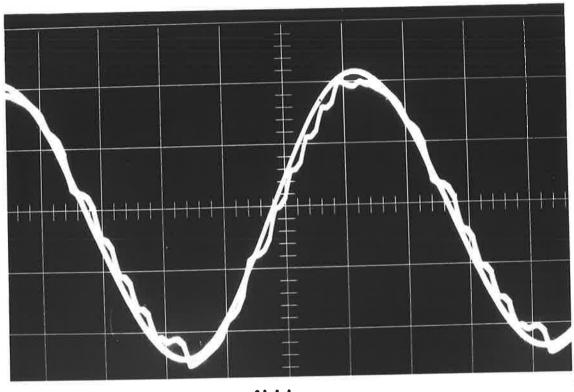

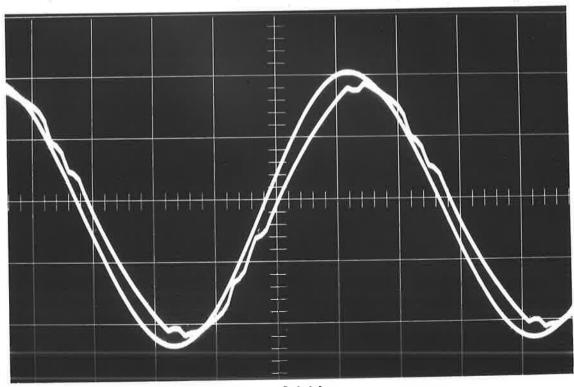

Fig 3.15 shows the measured performances when speech is used as input, obtained with the equipment described in chapter 2, together with the results obtained by computer simulation. It can be seen that the calculated and measured results agree remarkably well. Fig 2.10 shows the measured performance of NDDM for an 800Hz sinewave input. These

FIG.3.14 NDDM Hardware

diagrams show that the SMR for speech is quite different from the SMR for an 800Hz sinewave.

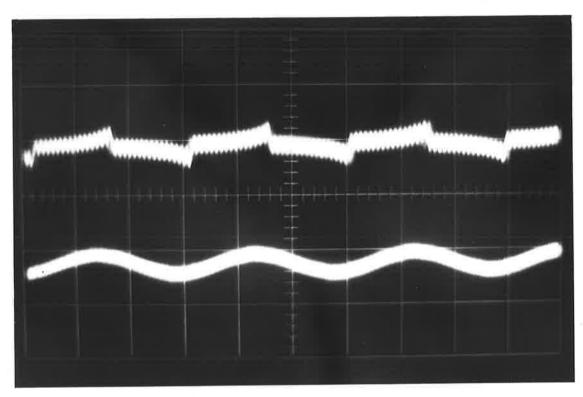

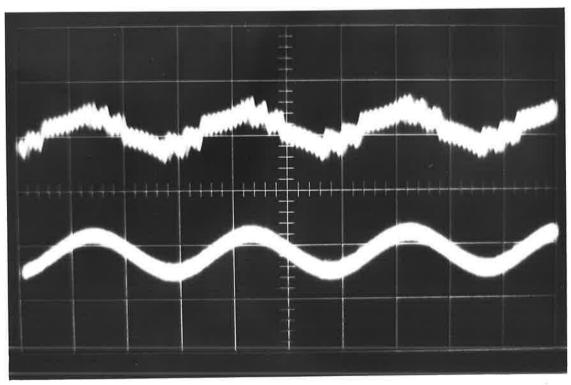

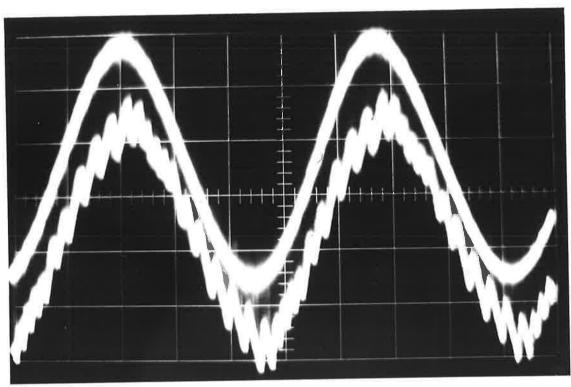

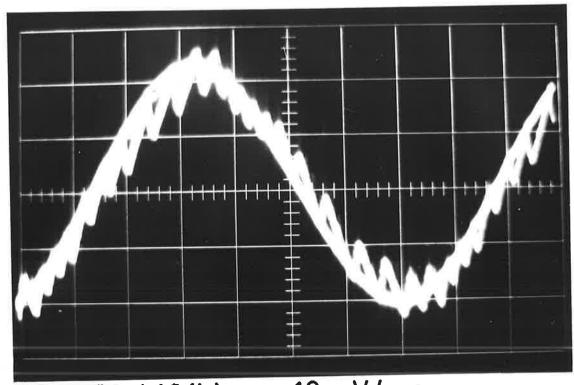

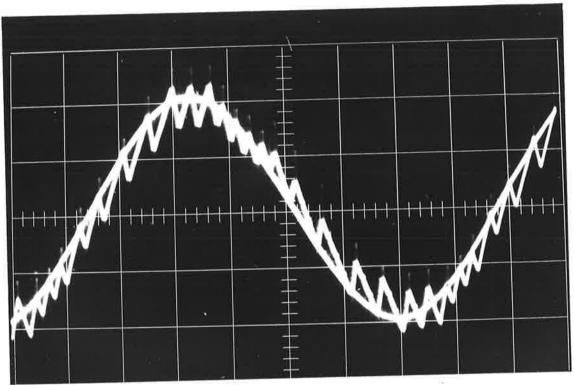

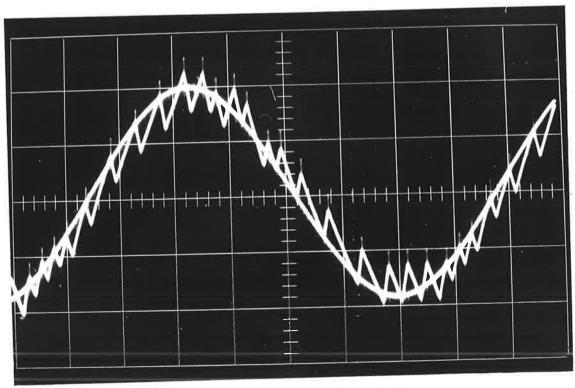

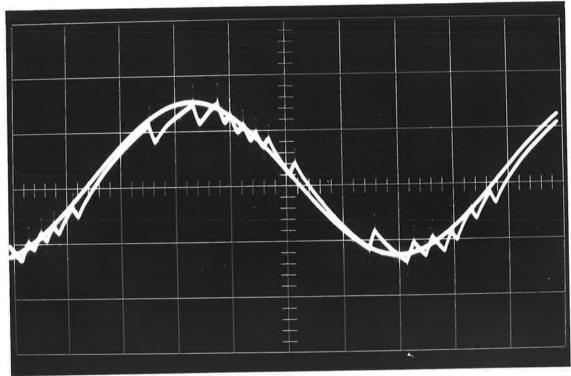

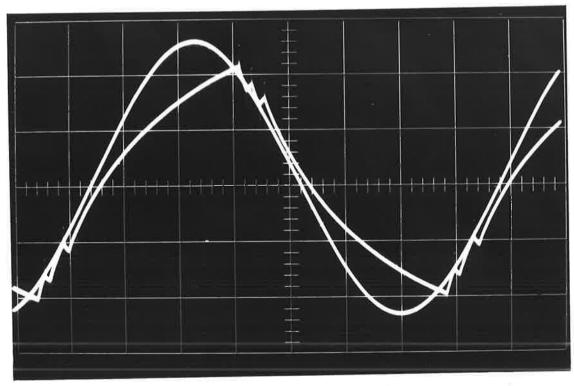

Fig 3.16 shows oscilloscope traces of the input and demodulated output waveforms, when an 875Hz sinewave is used as input. In order to obtain stationary oscilloscope traces, the input frequency was synchronised with the 56KHz sampling frequency.

## 3.5 Extensions

The NDDM system described in section 3.3 was optimized to give as flat a SMR over as wide a dynamic range as possible. The development of Digital Syllabic Companded Delta Modulation (DSCDM) as described in the next chapter, it is possible to obtain a wide dynamic range. Instantaneous companding can then be used to obtain a high SMR. A possible extension of this thesis is thus the optimization of MDDM to give a high SMR and combining this with syllabic companding to obtain a wide dynamic range as well. Such a delta modulator will have a better performance than any delta modulator developed previously, but it will however also be more complex.

A second extension which can be investigated is the further improvement of the stability. DIDM has a low quantization noise if no overshoot occurs but from the step responses in fig 3.6 it can be seen that a large oscillation results from a step response. When this overshoot occurs, a

20mV/cm

FIG.3.16(a) 100 mV/cm

1V/cm

FIG.3.16 (b) 2 V/c m

large series of consecutive ones or zero's are produced. These sequences can be detected and the stability can be increased by changing the step size by more than one step as indicated for NDDM. The above proposal gives yet another degree of freedom which can be optimized to obtain the best performance from the delta modulator.

#### 3.6 Conclusions

The investigation in instantaneous companding of delta modulation and the optimization of NDDM has shown that by using a nonlinear conditional companding law, excellent stability and a wide dynamic range can be obtained. The use of digital techniques to obtain this companding law makes the companding characteristic independant of temperature and supply voltage variations, enabling identical demodulated waveforms to be obtained at the transmitter and receiver.

#### CHAPTER 4

#### DIGITAL COMPANDED DELTA MODULATION

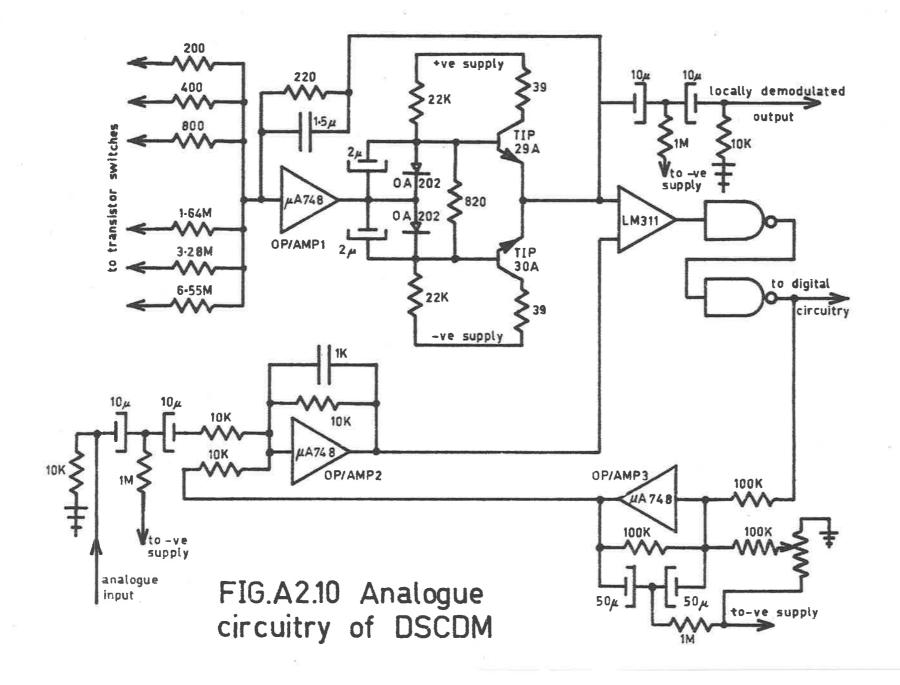

#### 4.1 Introduction

This chapter deals with the development, design criteria and the performance of digital syllabic companded delta modulation.

As indicated in chapter 1, many systems using syllabic companding have been designed by other workers. None of these have advantages that digital techniques can offer. It will be shown that the delta modulator using the digital syllabic companding developed by the author and described in this chapter has a companding ratio which exceeds that of previously known systems by about 25dB.

### 4.2 Syllabic Companding

A substantial improvement in performance of any modulation system can be obtained if the modulating signal is of such a power level that the modulator works at the optimum performance. This can be obtained by two different methods:

- (1) A reduction of the dynamic range by means of controlling the gath of the modulator and demodulator. This is known as companding with incomplete control.

- (2) Splitting the input signal into two components, firstly, a signal with a constant power indicating the waveform of the input signal and secondly, a signal denoting the average

power of the input signal. This is known as companding with complete control.

Each of these two types will later be described in more detail.

If speech is used, the average power varies with each syllable and the companding must be capable of following this variation, hence the name "syllabic companding".

Many of the principles of syllabic companding were investigated during the late thirties (13) when the Atlantic telephone cables were installed.

## 4.2.1 Companding with Incomplete Control

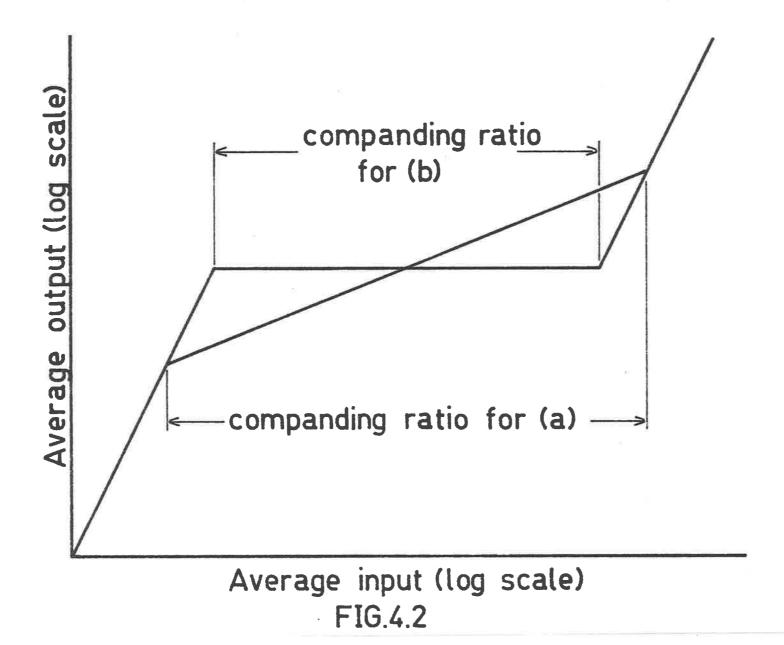

The block diagram of a modulator using companding with incomplete control is shown in fig 4.1. By means of gain control circuitry, the gain of the compressor is varied such that the dynamic range of the modulating signal is reduced. For incomplete control an increase in the input power will still provide a small increase in the modulating signal power so that there is a one to one relationship between the modulating signal power and the input signal power. Fig 4.2(a) shows a typical relationship between the power levels of the input and the modulating signals. Since there is 1:1 correspondence between the average input and output power levels at the compressor, the inverse relationship at the expander will restore the original power levels. There will however still be variations in modulation depth which means

FIG.4.1 Block diagram of a modulator with incomplete companding

that the modem will not always operate at its best performance. For example from fig 2.3 and fig 4.3 it can be seen that the peak performance of an uncompanded delta modulator occurs over a very narrow range of input signals. If the delta modulator is to work at its peak performance, the input power must be kept within narrow limits. For this reason companding with complete control is advantageous for delta modulation.

## 4.2.2 Companding with Complete Control

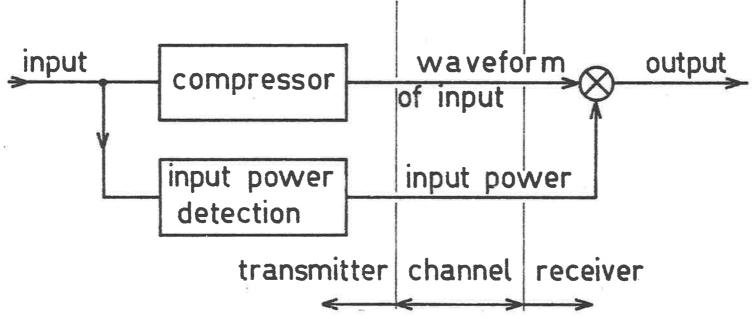

If the gain of the compressor is varied such that the modulating signal power is kept constant, companding with complete control is obtained. Since however there is no longer a one to one correspondence between the input power and modulation depth it is not possible to use the inverse characteristics to obtain the required output power at the expander. The information about the input power level must thus be transmitted separately as shown in fig 4.4. The companding characteristics of a compander with complete control is shown in fig. 4.2(b).

Since the rate of change of gain is normally small the bandwidth of the channel transmitting the gain does not have to be wide. In some cases the two channels are combined into one by means of frequency division multiplexing. In speech applications the bandwidth below 150Hz can easily be used to transmit the gain information.

FIG.4.4 Method by wich complete companding can be obtained

The system proposed by Greefkes and de Jager (15) applies this principle to delta modulation. Some of the other systems mentioned in chapter 1 (10,11,12,16) use incomplete control, so that both complete and incomplete control of companding have been used in delta modulation in an attempt to restrict the modulation depth to the narrow range required to give the optimum SNR.

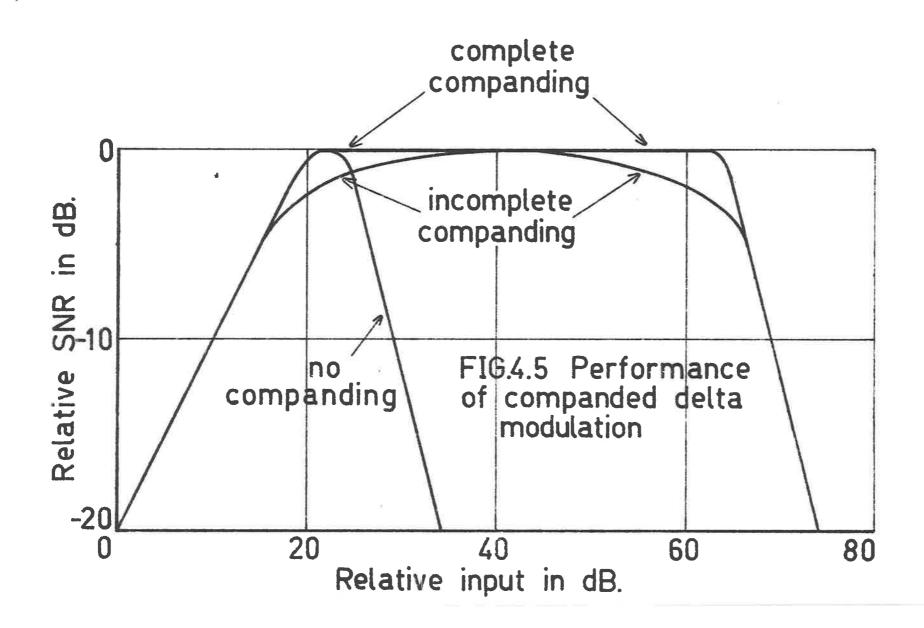

Fig 4.5 shows the difference in the performance of a delta modulator when complete or incomplete control of the companding is used. For incomplete control a region of the SNR curve of the uncompanded system is expanded, while for complete control a single point of the SNR curve is expanded horizontally. From fig 4.5 it can be seen that complete companding will give a better performance for delta modulation.

# 4.3 Companding with Complete Control, applied to Delta Modulation

The following section describes the theoretical principles involved in the design of digital syllabic companded delta modulation (DSCDM). These principles are also described in the Australian Patent No. C349663/71 and the U.S. Patent No. 193,410 (20) taken out by the author and the University of Adelaide. A copy of this patent is included in the thesis as Appendix 5.1

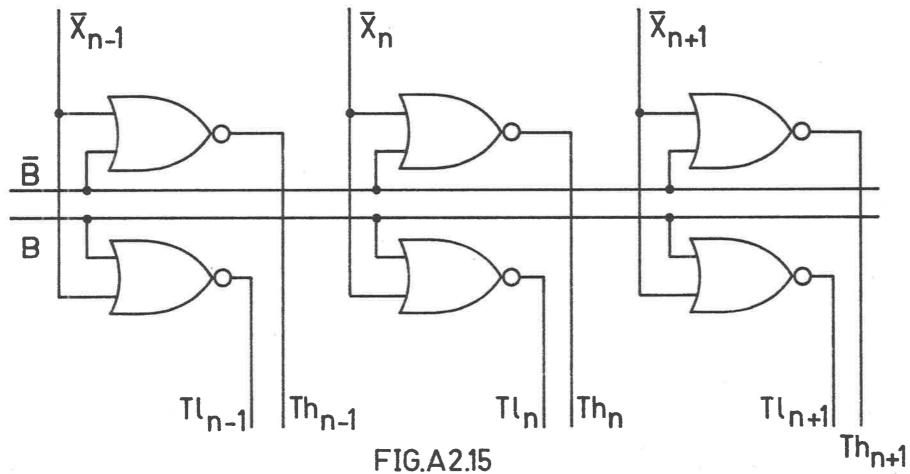

#### 4.3.1 Detection of Normalised Input Power

Fig 4.3 indicates the performance of SIDM for a variation of input power. From fig 1.2 it can be seen that if the step size is increased, the amount of input power required to obtain the optimum SNR will increase as well.

Similarly for a given input power, the optimum performance can be obtained from the delta modulator, by selecting a suitable step size. The ratio of input power to step size is thus an important parameter and is called the normalised input power.