# **OWNER'S MANUAL Model 2718** Serial / Parallel I / O Interface 6-

# CCS MODEL 2718

:

.

3

:

# PARALLEL/SERIAL INTERFACE

OWNER'S MANUAL

Rev. A

Manual #89000-02718 Copyright 1980 California Computer Systems 250 Caribbean Drive Sunnyvale CA 94086

#### TABLE OF CONTENTS

#### CHAPTER 1 THEORY OF OPERATION

| 1.1 | PORT ADDRESSING    | 1-1 |

|-----|--------------------|-----|

| 1.2 | THE PARALLEL PORTS | 1-4 |

| 1.3 | THE SERIAL PORTS   | 1-4 |

| 1.4 | STATUS REGISTERS   | 1-6 |

| 1.5 | CONTROL ROM        | 1-6 |

# CHAPTER 2 SET-UP

:

:

2

| 2.1 | JUMPERS                | 2-1 |

|-----|------------------------|-----|

| 2.2 | STATUS HEADER          | 2-8 |

| 2.3 | BUFFER POLARITY OPTION | 2-8 |

| 2.4 | CABLE CONSTRUCTION     | 2-8 |

#### CHAPTER 3 PROGRAMMING INFORMATION

| 3.1 | PARALLEL PORTS    | 3-1 |

|-----|-------------------|-----|

| 3.2 | SERIAL PORT A     | 3-2 |

| 3.3 | SERIAL PORT B     | 3-2 |

| 3.4 | BAUD RATE         | 3-7 |

| 3.5 | SOFTWARE EXAMPLES | 3-7 |

# APPENDIX A TECHNICAL INFORMATION

| A.1 | SPECIFICATIONS                         | A-2 |

|-----|----------------------------------------|-----|

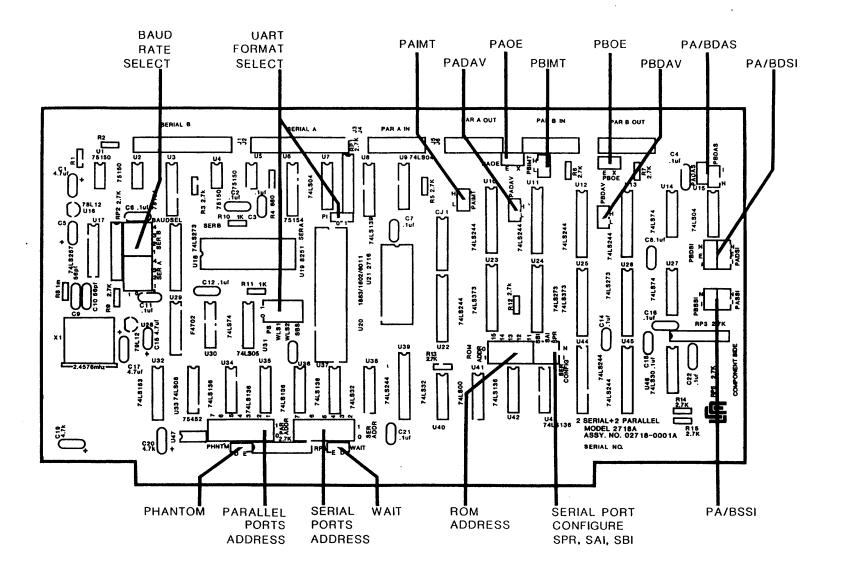

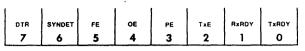

| A.2 | COMPONENT LAYOUT DIAGRAM               | A-3 |

| A.3 | PARTS LIST                             | A-4 |

| A.4 | RS-232-C INTERFACE CONFIGURATION TYPES | A-6 |

| A.5 | STANDARD INTERFACE CONFIGURATIONS      | A-6 |

|     | RS-232-C CONNECTOR PINOUT              |     |

|     | SERIAL CONNECTOR PINOUTS               |     |

|     | PARALLEL CONNECTOR PINOUTS             |     |

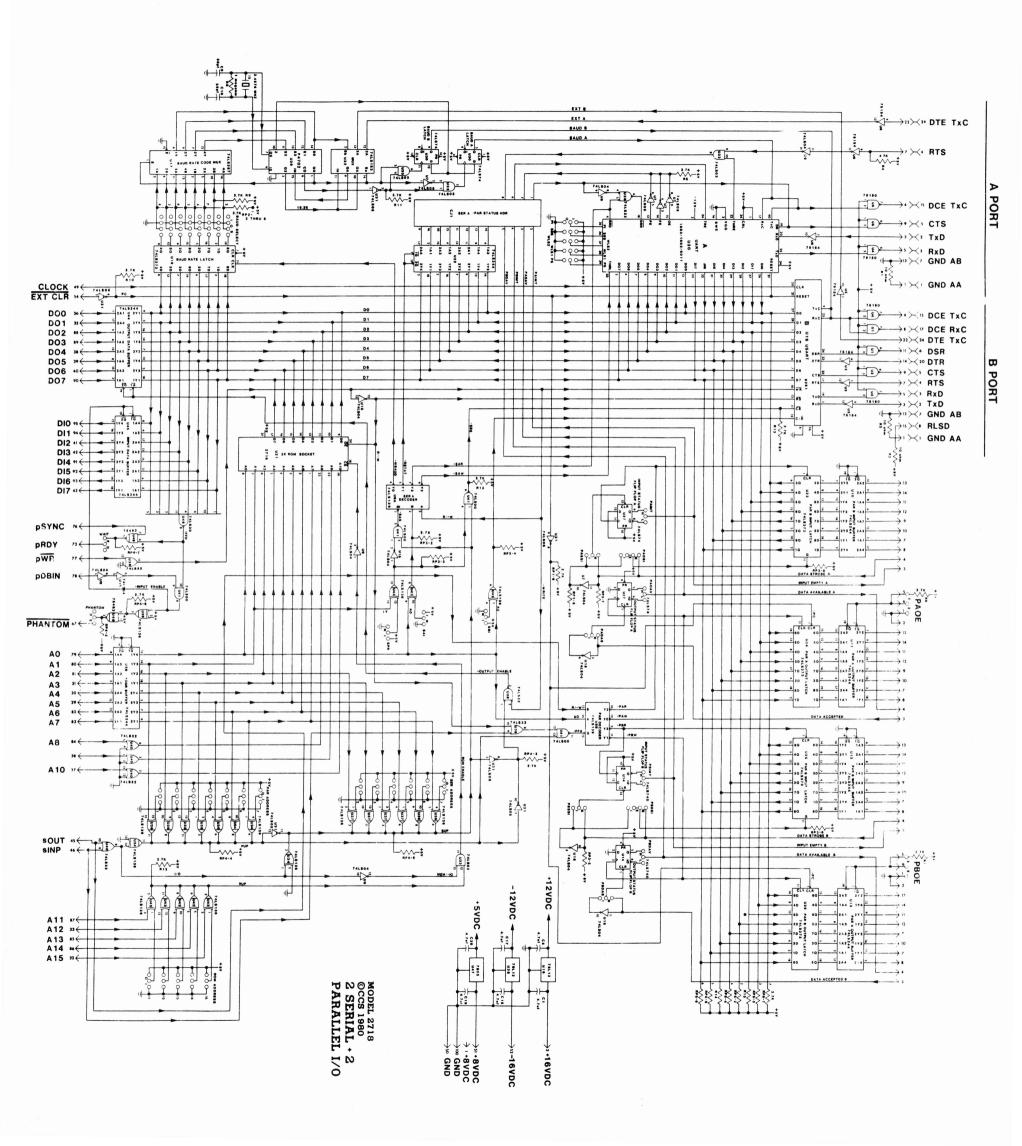

| A.9 | SCHEMATIC/LOGIC DIAGRAM A              | -11 |

# APPENDIX A UART/USART INTERNAL OPERATION

| B.1 | THE | UART  | R-1        |

|-----|-----|-------|------------|

| B.2 | THE | USART | <u>B-3</u> |

APPENDIX C LIMITED WARRANTY

# **CHAPTER 1**

# THEORY OF OPERATION

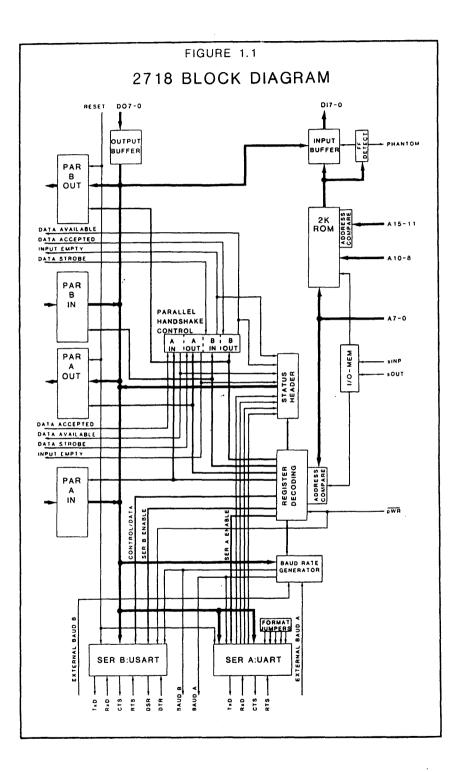

The CCS Model 2718 is a highly flexible I/O interface board featuring two serial ports and two parallel ports, with full handshaking for each port. Of the serial ports, one is asynchronous (a UART), while the other can be programmed to be synchronous or asynchronous (a USART). Both provide considerable format selectability, the UART through hardware, the USART through software. The interface for each serial port conforms to the EIA RS-232-C specifications, while each parallel port includes a full four-line handshaking scheme, with jumpers allowing selection of the sense polarity of the individual lines. The base addresses of the serial ports, the parallel ports, and an (user-supplied) 2K optional ROM are also jumper-selectable.

This chapter describes in general the circuitry of the 2718. For clarification and greater detail, see the schematic/logic diagram, Section A.9, and the block diagram on page 1-3. Throughout the manual, a low-active signal is indicated by an asterisk after the signal name/mnemonic (e.g., pWR\*), or by a bar over the name/mnemonic.

#### 1.1 PORT ADDRESSING

.

2

The PAR ADDR and SER ADDR jumpers allow selection of the base addresses of the 2718's parallel and serial ports. The serial ports occupy four sequential addresses, the base address being set on SER ADDR jumpers 2-7 to any multiple of 4 within the S-100's block of 256 I/O ports. The parallel ports occupy two sequential addresses, PAR ADDR jumpers 1-7 determining the base address at any multiple of 2 between 0 and 255. The internal signal PUP (Parallel Up) is active when address bits Al-A7 match the PAR ADDR jumper settings and the I/O signal (SINP ORed with sOUT) is high. If, when PUP is high, either pWR\* or SINP is high (indicating a data transfer operation), the Parallel Port Decoder (U8B) is enabled. AO then determines whether port A or port B is addressed, while sOUT determines whether an input or output latch is enabled (see Table 1.1.)

If address bits A2-A7 match the SER ADDR jumper settings while I/O is active and PUP is low, SUP (Serial Up) will be high. When SUP is high, the condition of A1 determines whether the UART or the USART is selected. Separate A0 and pWR/SOUT inputs control register addressing for each port (see Tables 1.2 and 1.3). Jumpers SPR, SAI, and SBI allow the sense polarity of A1 and the separate A0 inputs to each serial port to be inverted (see Sections 2.1.2 and 2.1.3). In the tables below and throughout this chapter it is assumed that A1 and A0 are not inverted.

| AO | sOUT | REGISTER     |

|----|------|--------------|

| 0  | 0    | Par A Output |

| 0  | 1    | Par A Input  |

| 1  | 0    | Par B Output |

| 1  | 1    | Par B Input  |

| AO | pWR | REGISTER         |

|----|-----|------------------|

| 0  | 0   | Baud Rate        |

| 0  | 1   | Ser A/Par Status |

| 1  | 0   | UART Transmitter |

| 1  | 1   | UART Receiver    |

| A0 | pWR | REGISTER          |

|----|-----|-------------------|

| 0  | 0   | USART Transmitter |

| 0  | 1   | USART Receiver    |

| 1  | 0   | USART Command     |

| 1  | 1   | USART Status      |

PARALLEL PORTS

TABLE 1.1

SERIAL PORT A

TABLE 1.2

SERIAL PORT B

When either SUP or PUP is high and I/O is high, OUTPUT ENABLE\* goes low, enabling the Output Data Buffer, which gates data from the S-100 bus. OUTPUT ENABLE\* high tri-states the Output Data Buffer.

PUP high forces SUP low, allowing the parallel ports to overlay one of the serial ports. If the parallel ports overlay the USART, parallel status information will still be available at the UART status address. This is accomplished when PAR ADDR 2-7 and SER ADDR 2-7 are set to the same value and PAR ADDR 1 is set to 1 (or 0 if Al is inverted by SPR). THEORY OF OPERATION

.

.

ł

Т

ţ

.

-

2

2

#### 1.2 PARALLEL PORTS

The 2718's two parallel ports provide bi-directional 8-bit interfacing with four-line handshaking. Each parallel port consists of separate buffered input and output registers. The Parallel Port Decoder decodes A0 and sOUT to activate one of the four register-enabling lines PAR\*, PAW\*, PBR\*, and PBW\* (Parallel A and B Read and Write). The input buffers are permanently enabled, while the output buffers can be enabled by the peripheral device or constantly enabled (see Section 2.1.9).

The register latches are controlled by the registerenable lines and the handshake inputs. DATA STROBE, by which the peripheral indicates that it has made valid data available, gates data into the Input Latch and clears the Input Status Flip-Flop to indicate that the port has data to be read; PAR\*/PBR\* enables Input Latch output to the 2718's internal data bus, from which it is gated to the processor through the Input Data Buffer by pDBIN active, and sets the Input Status Flip-Flop to indicate INPUT EMPTY. The Output Latches operate similarly. PAW\*/PBW\* clocks data into the latch and clears the Output Status Flip-Flop to indicate DATA AVAILABLE; when the peripheral toggles DATA ACCEPTED, the Output Status Flip-Flop is reset. If jumper PAOE/PBOE is set to X (External), data will be available to the peripheral only when it pulls pin 5 or pin 6 low (see Section 2.1.9). The Output Registers are cleared by EXT CLR\* low. The Status Flip-Flop outputs INPUT EMPTY A and B and DATA AVAILABLE A and B are also the parallel port status bits.

#### 1.3 SERIAL PORTS

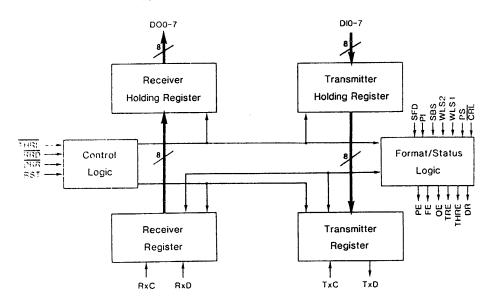

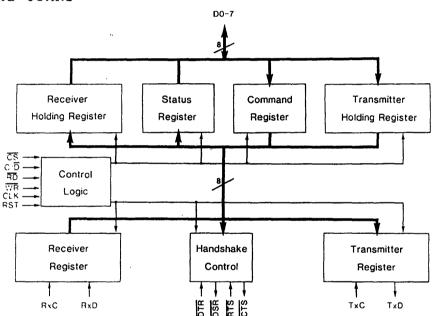

Because peripheral equipment that communicates serially can do so in a variety of formats, the 2718 incorporates two different serial interface chips: a Universal Asynchronous Receiver/Transmitter (UART), and a Universal Synchronous/ Asynchronous Receiver/Transmitter (USART). Together these chips allow interfacing with a wide variety of serial devices. A general description of their implementation in the 2718 follows. For a table of UART and USART inputs and outputs and a discussion of the internal operation of the chips, see Appendix B.

#### THEORY OF OPERATION

#### 1.3.1 SERIAL PORT A: THE UART

The UART translates parallel data to asynchronous serial data and vice versa according to jumper-determined format inputs (see Section 2.1.11). When transmitting, it arranges the parallel data serially in a 5- to 8-bit word, adds a start bit, a parity bit if parity is enabled, and 1, 1½, or 2 stop bits, then shifts the data onto TxD. When receiving, the UART strips the start and stop bits, checks parity if enabled, makes the data available in parallel on the 2718's internal data bus, and provides format error and status information. UART transmitting and receiving are controlled by the SAR\* and SAW\* (Serial A Read and Write) outputs of the Serial A decoder. A low on EXT CLR\*, inverted, resets the UART.

#### 1.3.2 SERIAL PORT B: THE USART

2

The USART is enabled by SBS\* (Serial B Select\*) when addressed. Command words program the USART to the mode and format desired, C/D\* (controlled by A0) high and WR\* (controlled by pWR\*) low selecting the command register; the commands themselves are given in Section 3.3. When mode and format have been programmed, a low on C/D\* enables data transmitting (pWR\* low) or receiving (pWR\* high). Like the UART, the USART is reset by EXT CLR\* low inverted high.

#### 1.3.3 BAUD RATE GENERATION

The serial port data transfer rates are controlled by BAUDA and BAUDB. Two sets of jumpers allow hardwiring or software-selection of the desired baud rates. If the software mode is selected, the baud rate byte, clocked into the Baud Rate Register by WBAUD\*, is input to the Baud Rate Select Multiplexer. If the jumpers are set for the hardware mode, the mux inputs are determined solely by the jumper positions, no matter what is written to the Baud Rate Latch.

A 4702 programmable bit rate generator provides thirteen different baud rates. In addition, a multiplexed input (IM) allows externally-generated baud rates (input from the peripherals along with the handshake lines) to be output by the 4702. Multiplexer U32 provides either a 19.2K baud rate or multiplexed ExtA and ExtB baud rates for input through IM. The output of the 4702 reflects the multiplexing of the inputs. Two AND gates, an inverter, and two flip-flops form a two-bit addressable latch which demultiplexes the output into the separate signals BAUDA and BAUDB.

#### 1.4 STATUS REGISTERS

The 2718 has two status registers. One is addressed at Serial Port B as shown in Table 1.3, and is internal to the USART. The other, addressed at Serial Port A as shown in Table 1.2, consists of four bits each of UART and Parallel Port status. The UART status bits are described in Section 3.2; the Parallel Ports' status bits reflect their handshake outputs INPUT EMPTY and DATA AVAILABLE. Enhancing the flexibility of the 2718, the Status Select Header allows user formatting of the Ser A/Par status register. This permits emulation of other boards, providing compatibility with pre-existing software.

#### 1.5 CONTROL ROM

Provision is made on-board the 2718 for a 2K EPROM, in which may be stored the peripheral driver programs. Driver software must be supplied by the user; see Chapter 4 for examples. If the driver routines are to be stored elsewhere in the system, the 2718's ROM socket may be used for 2K of general purpose ROM, or may be left empty, in which case it will occupy no memory space. FF Detect Circuitry allows programming of the EPROM on a byte-by-byte basis. The open collector output of the NANDing of the data lines (FFD\*) is pulled low when the internal data bus lines are all 1's (FFh); FFD\* low disables the Input Data Buffer. Thus 2718 ROM locations will not conflict with other memory locations having the same addresses if the 2718 locations are left in the unprogrammed (all 1's) state.

The ROM is enabled when both PRUP (PROM Up) and MEM/IO\* are high. PRUP is high when ROM ADDR jumpers 15-11 match address bits A15-A11, allowing location of the ROM at any 2K boundary within 64K. ROM output is enabled only when pWP\* is high. Phantom Circuitry allows the 2718 ROM to overlay other system memory that is disabled by PHANTOM\*. For example, if on-board 2718 driver routines are used with a CCS 2810 CPU, the ROM base address should be set to F000h

#### THEORY OF OPERATION

and the PHNTM jumper should be set to E. When an address common to the Monitor and a routine on the 2718 ROM is put on the address bus, the 2718 pulls PHANTOM\* low to disable the CPU ROM. The 2718 ROM retains control until an unprogrammed location is addressed, a jump out of the routine is executed, or the top address on the ROM has been read. When an empty location is addressed, the low on FFD\* forces PHANTOM\* high, allowing program control to default to the Monitor ROM.

# **CHAPTER 2**

# SET-UP

#### 2.1 JUMPERS

1

A number of features on the 2718 must be jumper-configured. Figure 2.1 shows the locations of the jumpers on the board. To set a jumper, firmly seat a blue Berg jumper plug over the two header pins corresponding to the desired setting.

#### 2.1.1 PARA ADDR 1-7, SER ADDR 2-7

The seven most significant bits of the parallel ports' base address are set on the PAR ADDR jumpers. The six most significant bits of the serial ports' base address are set on the SER ADDR jumpers. Jumper 7 sets the most significant bit in each case. Table 2.1 gives the binary form of all possible port addresses.

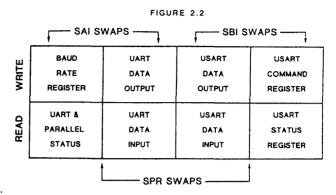

#### 2.1.2 SPR

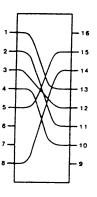

The Serial Ports Reverse jumper inverts the Al signal that enables either the Serial A or Serial B port. When the SPR jumper is set to N (non-inverted), SER A is selected by a Al=O and SER B by Al=1. Setting the SPR jumper to I (inverted) causes SER A to be selected by Al=1 and SER B by Al=O. See Figure 2.2.

# TABLE 2.1

# POSSIBLE PORT ADDRESSES

|    | A                                       | DDRI                                    | ESS                                     | BI                                       | ГS                                                                   |                                          | PORT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ADDRESS                                                          |

|----|-----------------------------------------|-----------------------------------------|-----------------------------------------|------------------------------------------|----------------------------------------------------------------------|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|

| Α7 | A6                                      | A5                                      | A4                                      | A3                                       | A2                                                                   | A1*                                      | HEX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | DECI                                                             |

|    | 000000000000000000000000000000000000000 | 000000000000000011111111111111000000000 | 000000011111111100000000111111110000000 | 0000111110000111110000111110000111110000 | 00110011001100110011001100110011001100110011001100110011001100110011 | 0101010101010101010101010101010101010101 | 002468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE0248ACE0248ACE0248ACE0248ACE0248ACE0248ACE0248ACE0248ACE0248ACE0248ACE0248ACE0248ACE0248ACE0248ACE0248ACE0248ACE0248ACE0248ACE0248ACE0248ACE0248ACE0248ACE0248ACE0248ACE0248ACE0248ACE0248ACE0248ACE0248ACE0248ACE0248ACE0248ACE0248ACE0248ACE0248ACE0248ACE0248ACE0248ACE0248ACE0248ACE0248ACE0248ACE0248ACE0248ACE0248ACE0248ACE0248ACE0248ACE0248ACE0248ACE0248ACE0248ACE0248ACE0248ACE0248ACE0248ACE0248ACE0248ACE0248ACE0248ACE0248ACE0248ACE0248ACE0248ACE0248ACE0248ACE0248ACE0248ACE0248ACE0248ACE0248ACE0248ACE0248ACE0248ACE0248ACE0248ACE0248ACE0248ACE0248ACE0248ACE0248ACE0248ACE0248ACE | 0<br>2468<br>102116<br>12022468024680246802468024680246802468024 |

| *A1  | of   | Serial  | Ports' | Base | Address |  |

|------|------|---------|--------|------|---------|--|

| mus1 | t ed | jual 0. |        |      |         |  |

|    | A                                       | DDR                                     | ESS                                     | 81                                       | TS                                                                   |                                          | PORT                                                                                                     | DDRESS                                                                 |

|----|-----------------------------------------|-----------------------------------------|-----------------------------------------|------------------------------------------|----------------------------------------------------------------------|------------------------------------------|----------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|

| A7 | A6                                      | Α5                                      | A4                                      | A3                                       | A2                                                                   | A1                                       | HEX                                                                                                      | DECI                                                                   |

|    | 000000000000000000000000000000000000000 | 000000000000000000000000000000000000000 | 000000011111111100000000111111110000000 | 0000111110000111110000111110000111110000 | 00110011001100110011001100110011001100110011001100110011001100110011 | 0101010101010101010101010101010101010101 | 02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE02468ACE | $\begin{array}{c} 128\\ 132\\ 132\\ 132\\ 132\\ 132\\ 132\\ 132\\ 132$ |

1-

# **2718 JUMPER POSITIONS**

SET-UP

2-3

#### 2.1.3 SAI, SBI

The Serial A Invert jumper inverts the AO signal that selects between the data and baudrate/status registers of the UART. The data registers are selected by AO=1 when the SAI jumper is set to N, and by AO=0 when the jumper is set to I.

The Serial B Invert jumper similarly swaps the addresses of the command and data registers of the USART. The data registers are addressed by AO=1 when the SBI jumper is set to N, and by AO=0 when the jumper is set to I. The effects of SAI and SBI are shown in Figure 2.2.

#### 2.1.4 PADSI, PBDSI

STROBE

ACTIVE

LOW

LOW

HIGH

HIGH

PxSSI

SET TO

Ν

1

N

ł

STATUS STROBE INVERT JUMPERS

TABLE 2.2

CLEAR WHEN

STROBE IS

ACTIVE

INACTIVE

INACTIVE

ACTIVE

The Parallel A and B Data Strobe Invert jumpers control the polarity of the peripheral-generated DATA STROBE signals used to gate the Parallel Port Input Latches. Output follows input when the gate input (G) is high; output is latched by G going low. To latch data on the trailing edge of DATA STROBE, set a jumper to N if the signal is active high and to I if it is active low. The E position enables constant data flow (no latching) by holding G permanently high.

#### 2.1.5 PASSI, PBSSI

A read to a parallel port (PAR\* or PBR\* low) sets the port's Input Status Flip-Flop to indicate that data has been taken. The Parallel A and B Status Strobe Invert jumpers control the polarity of the DATA STROBE signals used to clear the Input Status Flip-

Flops, which indicates that new data is available. If DATA STROBE is active high, set the SSI jumper to I; if it is active low, set the jumper to N.

SSI

SET-UP

2.1.6 PAIMT, PEIMT

The Parallel A and B Input Empty jumpers determine the sense polarity of the Input Empty handshake outputs. A setting of H produces a high-active signal; L produces a low-active signal.

#### 2.1.7 PADAS, PBDAS

A write to a parallel port (PAW\* or PBW\* low) clears that port's Output Status Flip-Flop. The Parallel A and B Data Accepted Strobe jumpers reverse the polarity of the DATA ACCEPTED handshake signals used to clear the Output Status flip-flops. Thus a flip-flop is cleared when DATA ACCEPTED goes low if its jumper is set to N, and when DATA ACCEPTED goes high if its jumper is set to I.

2.1.8 PADAV, PBDAV

The Parallel A and B Data Available jumpers determine the polarity of the DATA AVAILABLE handshake outputs, which signify that new data is available to the peripheral device. Setting a jumper to H produces a high-active signal; L produces a low-active signal.

2.1.9 PAOE, PBOE

The Parallel A and B Output Enable jumpers allow external enabling of the parallel port output buffers. If a jumper is set to X, that port's output buffer will be enabled by a low to pin 5 or pin 6 of the output connector. If a jumper is set to E, the buffer's -Enable input is tied to ground and the buffer is constantly enabled.

#### 2.1.10 UART FORMAT JUMPERS

#### TABLE 2.3

| WLS<br>2 | WLS<br>1 | WORD<br>LENGTH |

|----------|----------|----------------|

| 0        | 0        | 5 bits         |

| 0        | 1        | 6 bits         |

| 1        | 0        | 7 bits         |

| 1        | 1        | 8 bits         |

ł

WORD LENGTH JUMPERS

These five jumpers control the format of serial data transfer by the UART. WLS 1 and 2 select the word length as indicated in Table 2.3. SBS selects the number of stop bits, a 0 selecting 1 stop bit and a 1 selecting 2 5-bit words). PI=1 inhibits (13 for parity generation/reading. If parity is not inhibited, PS=1 selects even parity, and PS=0 selects odd.

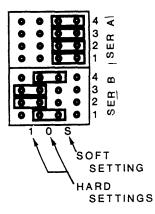

#### 2.1.11 BAUD SEL

FIGURE 2.3.

The Baud Rate Select jumpers determine the rates of data transfer by the serial ports. The UART's transmitter and receiver clocks are supplied by BAUD A, while BAUD B serves as clocks for the the USART. The baud rate for each port is determined by а four-bit code. If the BAUD SEL jumpers for a

port are set to S, the code is input Jumper positions 1 through software. and allow the code to be hard-wired. The 0 low-order bit of code, S0, is set on the #4. #1 jumper, the high-order bit on Figure 2.3 shows Serial Port A set for software control and Serial Port B set for 600 baud. The baud rate codes are given in Table 2.4.

TABLE 2.4

#### **BAUD RATE CODES**

| <b>S</b> 3 | <b>S</b> 2 | S 1 | SO | BAUD<br>RATE |

|------------|------------|-----|----|--------------|

| 0          | 0          | 0   | 0  | 19200        |

| 0          | 0          | 0   | 1  | EXT          |

| 0          | 0          | 1   | 0  | 50           |

| 0          | 0          | 1   | 1  | 75           |

| 0          | 1          | 0   | 0  | 134.5        |

| 0          | 1          | 0   | 1  | 200          |

| 0          | 1          | 1   | 0  | 600          |

| 0          | 1          | 1   | 1  | 2400         |

| 1          | 0          | 0   | 0  | 9600         |

| 1          | 0          | 0   | 1  | 4800         |

| 1          | 0          | 1   | 0  | 1800         |

| 1          | 0          | 1   | 1  | 1200         |

| 1          | 1          | 0   | 0  | 2400         |

| 1          | 1          | 0   | 1  | 300          |

| 1          | 1          | 1   | 0  | 150          |

| 1          | 1          | 1   | 1  | 110          |

#### 2.1.12 ROM ADDR

The five most significant bits of the base address of the on-board ROM are set on ROM ADDR jumpers 15-11. A15-A11 determine a 2K block; Al0-A0 address a specific location in the block. 2.5 Table aives the jumper settings for each 2K block.

#### 2.1.13 PHNTM

The PHANTOM\* line in the allows routines on-board ROM to overlav your monitor or other memory which is disabled by PHANTOM\* low. To enable the 2718's Phantom overlay capability, set the Phantom jumper to E. If the PHANTOM\* line is not needed, disable it by setting the jumper to D.

#### ADDRESS BITS ROM ADDRESS K=1024 A15 A14 A13 A12 A11 HEX 0K 2K 4K 6K 00 0000 0000000011 0 00000 ò 1000 1 0 0 1800 ò Ò 10000111100000 Ĩ Ò 0011001 8K Ò 10 26K 10 1000000001 1001100110011 1 30K 1 0 1 0 38k 1 Ĩ 11000001 10 46K 48k 50K 10 10 54K ò 56K 58k 10 Ē000 60K F800 1

#### TABLE 2.5

#### 2.1.14 WAIT

The processor samples pRDY in T2 of each instruction cycle and, if pRDY is low, inserts a wait state. The 2718 initiates a wait state, if the Wait jumper is set to E, in each cycle in which the board is active by pulling pRDY low when both pSYNC and FFD\* (FF Detect: see Section 1.5) are high. Because the 2718 data bus is held high when inactive, qualifying pSYNC with FFD\* allows wait state generation only when the 2718 is active. No wait states are initiated by the 2718 if the Wait jumper is set to D. Whether or not wait states will be necessary depends on the ROM and CPU speeds involved; the I/O devices do not require wait states.

#### ROM ADDRESS TABLE

#### 2.2 STATUS HEADER

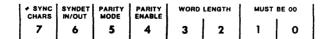

DR 16 DR D4 PAIMT 15 PADAV 14 DO PBIMT 13 DI PBDAV 12 D2 TRE 11 - D3 ERROR 10 - D5 THRE D7 SERIAL & STATUS HEADER

FIGURE 2.4

The Ser A/Par Status Header allows the user to format the Serial A/Parallel status byte. Fig. 2.4 shows header inputs and outputs by pin number. Fig. 2.5 illustrates a sample configuration in which UART status bits DR and THRE emulate USART status bits 1 (RxRDY) and 0 (TxRDY), Parallel Port A status is in bits 2-3, Parallel Port B status is in bits 4-5, and UART status TRE and ERROR are not made bits available.

FIGURE 2.5

#### 2.3 BUFFER POLARITY OPTION

The Parallel Port Input and Output Buffers, the System Bus Input and Output Buffers, the Address Buffer, and the Ser A/Par Status Buffer are non-inverting 74LS244's. Users who wish to invert any address, data, or status byte may do so by replacing the appropriate non-inverting buffer with a 74LS240 inverting buffer.

#### 2.4 CABLE CONSTRUCTION

Because peripherals compatible with the 2718 use a wide variety of connector configurations, no cables are included Each parallel port requires a cable with a with the board. polarized female 14-pin connector (T&B/Ansley 609-1403, AMP 88389-2) at the 2718 end and the appropriate connector at the mainframe end. serial cable requires a polarized Each female 26-pin connector (T&B/Ansley 609-2603, or AMP 88423-5) at the 2718 end and usually a female DB-25S connector at the 9-inch and an 18-inch serial cable are mainframe end. Α available separately from CCS (Products 7325A and 2000A). A parallel cable will be offered soon; the product number is not available as of this writing, however.

Please note that the Serial Port B connector is at the far left of the board (J1), and that the Serial Port A connector is the next connector to the right (J2). Sections A.7 and A.8 show the parallel and serial connector pinouts.

# CHAPTER 3

# **PROGRAMMING INFORMATION**

This chapter gives the 2718 register formats and discusses UART and USART programming. The actual addresses of the registers depend on the settings of several jumpers. Section 1.1 discusses how the various registers are addressed, while Sections 2.1.1-2.1.3 deal with the jumpers involved. Table 3.1 on page 3-3 shows the relative addresses of the serial port registers for all possible combinations of SPR, SAI, and SBI jumpers.

#### 3.1 PARALLEL PORTS

Parallel data transfer and handshaking are initiated by a read or write to a parallel port address; no other handshaking control is needed. Parallel port status can be read from the Serial Port A status register. Four status bits are available:

> PAIMT PBIMT } reflect the INPUT EMPTY handshake outputs. PADAV PBDAV } reflect the DATA AVAILABLE handshake outputs.

3.2 SERIAL PORT A

UART data transfer is initialized by a write to or read from a Serial Port A data register. All necessary handshaking is generated by the UART. Status can be read from the Serial A status register. There are four Serial A status bits:

TRE TRANSMITTER REGISTER EMPTY = 1 indicates that the TxR is empty.

DR

- DATA RECEIVED = 1 indicates that data has been received and transferred to the RxHR.

- THRE TRANSMITTER HOLDING REGISTER EMPTY, the result of the ANDing of the RTS handshake from the peripheral and the THRE output of the UART, indicates when set that a character may be loaded into the UART for transmission.

- ERROR ERROR = 1 indicates that no parity, overrun, or framing error has occurred.

#### 3.3 SERIAL PORT B

The USART is initialized by 2, 3, or 4 control words written to the command register. The Mode Word comes first. It is followed by the Command Word if the asynchronous mode is selected. If the synchronous mode is selected, one or two Sync Words will separate the Mode Word and the Command Word. After a reset, which puts the USART in an idle state and clears its registers, the USART must be reinitialized.

The Mode Word has one of the following formats, depending on whether the synchronous or asynchronous mode is selected:

SYNC CONTROL WORD FORMAT

FIGURE 3.1

3-2

| TABLE 3.1. JUMPER-DETERMINED SERIAL REGISTER ADDRESSES |                         |                         |                         |                         |                                |                                |                                |                              |

|--------------------------------------------------------|-------------------------|-------------------------|-------------------------|-------------------------|--------------------------------|--------------------------------|--------------------------------|------------------------------|

|                                                        |                         |                         |                         | JUMPER S                | ETTINGS                        |                                |                                |                              |

| REGISTER<br>ADDRESSED                                  | SPR=N<br>SAI=N<br>SBI=N | SPR=N<br>SAI=N<br>SBI=I | SPR=N<br>SAI=I<br>SBI=N | SPR=N<br>SAI=I<br>SBI=I | SPR=  <br>SA   = N<br>SB   = N | SPR= 1<br>SA I = N<br>SB I = I | SPR= 1<br>SA I = 1<br>SB I = N | SPR=  <br>SA   =  <br>SB   = |

| BAUD RATE                                              | BASE                    | BASE                    | BASE+1                  | BASE+1                  | BASE+2                         | BASE+3                         | BASE+2                         | BASE+                        |

|                                                        | WRITE                   | WRITE                   | WRITE                   | WRITE                   | WRITE                          | WRITE                          | WRITE                          | WRITE                        |

| SER A/PAR                                              | BASE                    | BASE                    | BASE+1                  | BASE+1                  | BASE+2                         | BASE+3                         | BASE+2                         | BASE+:                       |

| STATUS                                                 | READ                    | READ                    | READ                    | READ                    | READ                           | READ                           | READ                           | READ                         |

| SERIAL A                                               | BASE+1                  | BASE+1                  | BASE                    | BASE                    | BASE+3                         | BASE+2                         | BASE+3                         | BASE+                        |

| DATA OUT                                               | WRITE                   | WRITE                   | WRITE                   | WRITE                   | WRITE                          | WRITE                          | WRITE                          | WRITE                        |

| SERIAL A                                               | BASE+1                  | BASE+1                  | BASE                    | BASE                    | BASE+3                         | BASE+2                         | BASE+3                         | BASE+                        |

| DATA IN                                                | READ                    | READ                    | READ                    | READ                    | READ                           | READ                           | READ                           | READ                         |

| SERIAL B                                               | BASE+2                  | BASE+3                  | BASE+2                  | BASE+3                  | BASE                           | BASE                           | BASE+1                         | BASE+                        |

| COMMAND                                                | WRITE                   | WRITE                   | WRITE                   | WRITE                   | WRITE                          | WRITE                          | WRITE                          | WRITE                        |

| SERIAL B                                               | BASE+2                  | BASE+3                  | BASE+2                  | BASE+3                  | BASE                           | BASE                           | BASE+1                         | BASE+                        |

| STATUS                                                 | READ                    | READ                    | READ                    | READ                    | READ                           | READ                           | READ                           | READ                         |

| SERIAL B                                               | BASE+3                  | BASE+2                  | BASE+3                  | BASE+2                  | BASE+1                         | BASE+1                         | BASE                           | BASE                         |

| DATA OUT                                               | WRITE                   | WRITE                   | WRITE                   | WRITE                   | WRITE                          | WRITE                          | WRITE                          | WRITE                        |

| SERIAL B                                               | BASE+3                  | BASE+2                  | BASE+3                  | BASE+2                  | BASE+1                         | BASE+1                         | BASE                           | BASE                         |

| DATA IN                                                | READ                    | READ                    | READ                    | READ                    | READ                           | READ                           | READ                           | READ                         |

|                                                        |                         |                         |                         |                         |                                |                                |                                |                              |

•

۰.

3-3

•

.

-

| BITS 1,0 | 00 = synchronous mode                                                                                                                                        |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BITS 3,2 | 00 = 5 bits per character<br>01 = 6 bits per character<br>10 = 7 bits per character<br>11 = 8 bits per character                                             |

| BIT 4    | 0 = disable parity<br>1 = enable parity                                                                                                                      |

| BIT 5    | 0 = odd parity<br>1 = even parity                                                                                                                            |

| BIT 6    | 0 = SYNDET, pin 16, output<br>1 = SYNDET input<br>(Please note that because<br>the 2718 does not use pin<br>16, this bit must always<br>be programmed to 0.) |

| BIT 7    | 0 = two SYNC characters<br>1 = one SYNC character                                                                                                            |

ASYNC CONTROL WORD FORMAT

.

FIGURE 3.2

| BITS 1,0 | 01 = asynchronous, 1 x baud rate<br>10 = asynchronous, 16 x baud rate<br>11 = asynchronous, 64 x baud rate       |

|----------|------------------------------------------------------------------------------------------------------------------|

| BITS 3,2 | 00 = 5 bits per character<br>01 = 6 bits per character<br>10 = 7 bits per character<br>11 = 8 bits per character |

| BIT 4    | 0 = disable parity<br>1 = enable parity                                                                          |

| BIT 5    | 0 = odd parity<br>1 = even parity                                                                                |

| BITS 7,6 | 00 invalid<br>01 = 1 stop bit<br>10 = 1.5 stop bits<br>11 = 2 stop bits                                          |

#### PROGRAMMING INFORMATION

If the synchronous mode has been selected, the Mode Word is followed by one or two sync characters (as specified by bit 7 of the Mode Word). These characters must precede all data transmitted or received by the USART.

The Command Word initiates specific USART functions, such as resetting flags and searching for sync characters. Commands may be issued at any point in a program by a write to the USART's command address. Command Words have the following format:

|  | EH | IR | CTS | ER | SBRK | RxEN | DSR | TXEN |  |

|--|----|----|-----|----|------|------|-----|------|--|

|  | 7  | 6  | 5   | 4  | 3    | 2    | 1   | 0    |  |

COMMAND WORD FORMAT

FIGURE 3.3

۰.

| T×EN | TRANSMITTER  |           |        | be | 1 | for |

|------|--------------|-----------|--------|----|---|-----|

|      | transmission | to be ena | abled. |    |   |     |

DSR DATA SET READY = 1 forces the DSR handshake line high.

- RxEN RECEIVER ENABLE = 1 enables RxRDY output, pin 14, which is NOT USED BY THE 2718. When RxE is low, the OE flag is usually set; therefore we recommend that RxE be programmed to 1.

- SBRK SEND BREAK = 1 forces TxD output low until a subsequent Command word resets SBRK.

- ER ERROR RESET = 1 clears the error flags.

- CTS CLEAR TO SEND determines the polarity of CTS; a 1 forces CTS to 1. CTS is used for handshaking only, and has no effect on the transmission of data.

- IR INTERNAL RESET = 1 forces the USART into the idle mode; re-initializing is required before any forther operation is performed.

- EH ENTER HUNT = 1 causes the receiver to search for the sync word(s). The Hunt mode continues until the sync characters are found, a Command is sent in which EH = 0, or the USART is reset (externally or by IR = 0). This bit does not affect asynchronous operation.

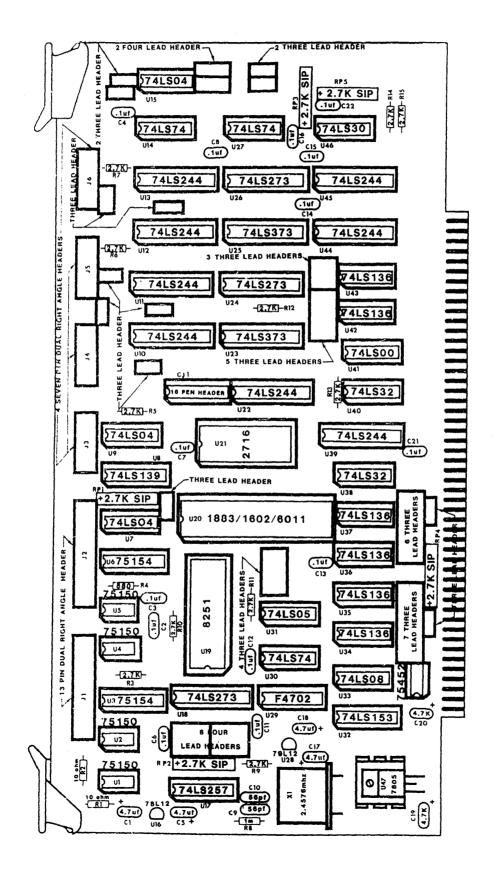

USART status can be read from the status register. The status byte has the following format:

\_\_ \_\_ \_

USART STATUS BYTE FORMAT

. . . . . . . . .

FIGURE 3.4

| I XRD Y | TRANSMITTER READY = 1 Indicates that the Transmitter Holding Register is empty.                                                                                                                       |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R×RDY   | RECEIVER READY = 1 indicates that a character is present in the Receiver Holding Register.                                                                                                            |

| Τ×Ε     | TRANSMITTER EMPTY = 1 indicates that the Transmitter Register is empty.                                                                                                                               |

| PE      | PARITY ERROR = 1 indicates an incorrect<br>number of 1's in a received character.                                                                                                                     |

| OE      | OVERRUN ERROR = 1 indicates that a character has been overwritten in the RxHR.                                                                                                                        |

| FE      | FRAMING ERROR = 1 indicates that an<br>improperly-formatted async character has<br>been received in the RxHR.                                                                                         |

| SYNDE⊤  | SYNC DETECTION reflects synchronous mode<br>control bit 6, indicating either<br>internal or external synchronization.<br>The 2718 uses internal sync; therefore<br>the SYNDET bit should always be 0. |

| DTR     | DATA TERMINAL READY is set by the DTR handshake signal to indicate that the peripheral is ready.                                                                                                      |

#### DECERAMMING INFORMATION

,

If the BAUDSEL jumpers for the UART and/or USART are set to S, the corresponding baud rate(s) are programmed by a write to Serial Port A's baud rate register, the low nibble of the baud rate byte determining the UART (Ser A) baud rate, the high nibble determining the USART (Ser B) baud rate, as illustrated in Figure 3.5. Table 3.1 gives the baud rate codes.

BAUD RATE CODES

| \$3 | 52 | 1 51 | 30 | 53 | 52 | 51 | ) Si |

|-----|----|------|----|----|----|----|------|

| 7   | 6  | 5    | 4  | 3  | 2  | 1  | d    |

FIGURE 3 5

#### **3.8.** SOFTWARE EXAMPLES

:

The following code sequences initialize and control Serial Port B of the 2718 as an interface for a Diablo Hi-Type printer. They may be used as is by owners of the CCS 2422 Disk Controller with CCS-modified CP/M, and as examples by those using other software.

;THIS CODE INITIALIZES PORT B (THE USART) OF THE 2718 ;  $I/\emptyset$  BOARD FOR ASYNCHRONOUS, 8-BIT, NO-PARITY DATA ;TRANSFER.

|      |    | /  |     |        |                           |

|------|----|----|-----|--------|---------------------------|

| ØØØØ | AF |    | XRA | А      | ;CLEAR A                  |

| ØØØl | D3 | Ø3 | OUT | LISTS  | ;ENSURE COMMAND MODE      |

| ØØØ3 | D3 | Ø3 | OUT | LISTS  | ;                         |

| ØØØ5 | D3 | Ø3 | OUT | LISTS  | ;                         |

| ØØØ7 | 3E | 4Ø | MVI | А,Ø4ØН | ;SOFTWARE RESET           |

| ØØØ9 | D3 | Ø3 | OUT | LISTS  | ;                         |

| ØØØB | 3E | CE | MVI | A,ØCEH | ;MODE WORD IS 11001110    |

| ØØØD | ГЗ | Ø3 | OUT | LISTS  | ;                         |

| 000F | 3E | 37 | MVI | А,Ø37Н | ;COMMAND WORD IS ØØ11Ø111 |

| 0011 | D3 | Ø3 | OUT | LISTS  | ;                         |

|      |    |    |     |        |                           |

| • |   |   |   |              |

|---|---|---|---|--------------|

| 4 | 3 | 2 | 1 | BAUD<br>RATE |

| 0 | 0 | 0 | 0 | 19200        |

| 0 | 0 | 0 | 1 | EXT          |

| 0 | 0 | 1 | 0 | 50           |

| 0 | 0 | 1 | 1 | 75           |

| 0 | 1 | 0 | 0 | 134.5        |

| 0 | 1 | 0 | 1 | 200          |

| 0 | 1 | 1 | 0 | 600          |

| 0 | 1 | 1 | 1 | 2400         |

| 1 | 0 | 0 | 0 | 9600         |

| 1 | 0 | 0 | 1 | 4800         |

| 1 | 0 | 1 | 0 | 1800         |

| 1 | 0 | 1 | 1 | 1200         |

| 1 | 1 | 0 | 0 | 2400         |

| 1 | 1 | 0 | 1 | 300          |

| 1 | 1 | 1 | 0 | 150          |

| 1 | 1 | 1 | 1 | 110          |

TABLE 3.1

;LINE PRINTER DRIVER FOR CP/M LIST DEVICE USING ;CCS MODEL 2718 I/O BOARD AND DATA TERMINALS ; CORPORATION MODEL 300/S (DIABLO HITYPE 1). ; THIS DRIVER PROVIDES A SIMPLE LST: INTERFACE ; TO CCS'S CCBIOS PORTION OF CP/M VERSION 2.2, USING PORT B (THE 8251 USART) OF THE 2718. ; THE DATA TERMINAL READY (DTR) SIGNAL ON RS-232-C ; PIN 20 (REFLECTED BY BIT 7 OF THE USART'S STATUS ; REGISTER) IS HONORED TO PREVENT OVERRUNNING OF ;THE PRINTER'S BUFFER. ; ; LIST: 1000 CD 5A F8 CALL LPSTAT ; RETRIEVE PRINTER PORT STATUS 1003 B7 ORA ;SET THE ZERO FLAG ON STATUS А 1004 CA 4F F8 JZLIST ;LOOP ON BUSY STATUS 1007 79 A,C ; PUT PASSED CHARACTER IN A MOV 1008 D3 02 LISTD ;OUTPUT CHARACTER TO PORT OUT 100A C9 RET **;**RETURN TO CALLER ; THE LPSTAT ROUTINE PROVIDES COMPATIBILITY WITH ;DIGITAL RESEARCH'S "DESPOOL" UTILITY AND COMPLIES ;WITH CP/M 2.2 CONVENTIONS. IT RETURNS TO THE ;CALLER WITH THE ACCUMULATOR EITHER RESET TO ZERO, ; IF THE PRINTER IS BUSY, OR SET TO ØFFH, IF THE ; PRINTER IS READY TO ACCEPT ANOTHER CHARACTER. ; ; LPSTAT: :INPUT PRINTER STATUS LISTS 100B DB 03 IN 100D E6 01 ANI ØlH ;MASK USART'S TXRDY BIT AND SET ZERO FLAG ON STATUS 100F C8 :RETURN TO CALLER WITH ZERO FLAG RZ ;SET IF TX BUFFER FULL--ELSE, 1010 DB 03 LISTS ; INPUT PRINTER STATUS IN ;MASK OUT DTR BIT AND SET ZERO FLAG 1Ø12 E6 8Ø Ø8ØH ANI 1014 EE 80 XRI Ø8ØH ; PASS STATUS BACK TO CALLER 1016 C9 RET

# APPENDIX A

-

# **TECHNICAL INFORMATION**

-

-

ł

.

#### A.1 SPECIFICATIONS

SIZE

|               | 10"   x 5" w                                 |

|---------------|----------------------------------------------|

| Connector:    | 6.35"   x .3" w (2.125" from right of board) |

| Component Ht: | less than .5"                                |

#### POWER SUPPLY

+8, +16, -16 Volts Regulated On-Board to +5, +12, -12 Volts .75 Amps at +8 Volts .05 Amps at +16 Volts .05 Amps at -16 Volts Consumption 110 gram-calories/minute .45 BTU/minute Heat Burden

#### ENVIRONMENTAL REQUIREMENTS

| Temperature: | 0°C. to +70°C.    |

|--------------|-------------------|

| Humidity:    | up to 90%         |

| Humidity:    | up to 90 <b>%</b> |

#### INTERFACING

Parallel: Full Bi-Directional Handshaking TTL-Compatible Outputs Hardware-Programmable Data and Strobe Polarity Hardware-Programmable Status Bit Positions Jumper-Selectable Base Address

Serial:

| Meets | s RS-232-0 | C Specifications<br>able Base Address |    |

|-------|------------|---------------------------------------|----|

| Jumpe | er-Selecta | able Base Address                     |    |

| Stand | jard Baud  | Rates from 75 to 19.2K Plus External  | s  |

| Baud  | Rates Ha   | rdware- and/or Software-Programmable  |    |

| 1602  | UART: I    | Hardware-Programmable Statuš and Asyn | ۱C |

|       | Data For   |                                       |    |

| 8251  | USART:     | Software-Programmable Sync/Async Dat  | s  |

|       | Formats    |                                       |    |

MEMORY

Circuitry For 2716-Type 2K ROM Jumper-Selectable Base Address FF Detect for 1 Byte to 2K Byte Memory Size Jumper-Selectable Phantom Output Jumper-Selectable Wait State

ADDITIONAL FEATURES

Reliable, easy-to-use Berg jumper plugs Low-power Schottky and MOS devices for minimum power consumption Sockets for all ICs Fiberglass epoxy (FR-4) PC board Solder-mask on both sides Gold-plated connector fingers Silk-screened component outlines, part designation, reference numbers reference numbers

1

#### A.2 COMPONENT LAYOUT DIAGRAM

# A.3 PARTS LIST

,

| QTY    | REF                          | DESCRIPTION                          | CCS PART #  |

|--------|------------------------------|--------------------------------------|-------------|

| Integr | rated Circuits               |                                      |             |

| 4      | U1-2,U4-5                    | 75150 RS232C line drvr               | 30300-00150 |

| 2      | U3,U6                        | 75154 RS232C line rcvr               | 30300-00154 |

| 3      | U7,U9,U15                    | 74LSO4 hex inverters                 | 30000-00004 |

| 1      | U8                           | 74LS139 dual 2:4 decoder             | 30000-00139 |

| 8      | U10-13,U22,<br>U39,U44-55    | 74LS244 3-state octal buffers        | 30000-00244 |

| 3      | U14,U27,U30                  | 74LS74 dual D flip-flops             | 30000-00074 |

| 1      | U16                          | 78L12 +12v regulator                 | 32000-17812 |

| 1      | U17                          | 74LS257 quad 3-state mux             | 30000-00257 |

| 3      | U18,U24,U26                  | 74LS273 octal d flip-flops           | 30000-00273 |

| 1      | U 1 9                        | 8251 USART                           | 31200-08251 |

| 1      | U2 <b>0</b>                  | 1602 UART                            | 31200-01602 |

| 2      | U23,U25                      | 74LS373 octal D latches              | 30000-00373 |

| 1      | U28                          | 79L12 -12v regulator                 | 32000-17912 |

| 1      | U29                          | 4702 prog bit rate generator         | 31000-04702 |

| 1      | U31                          | 74LSO5 hex inverters, OC             | 30000-00005 |

| 1      | U32                          | 74LS153 dua! 4:1 mux                 | 30000-00153 |

| 1      | U33                          | 74LSO8 quad 2-in AND                 | 30000-00008 |

| 6      | U34-37,U42-43                | 74LS136 quad EX-OR                   | 30000-00136 |

| 2      | U38,U40                      | 74LS32 quad 2-in OR                  | 30000-00032 |

| 1      | U 4 1                        | 74LSOO quad 2-in NAND                | 30000-00000 |

| 1      | U <b>4</b> 1                 | 74LS30 8-in NAND                     | 30000-00030 |

| 1      | 347                          | 7805 +5v regulator                   | 32000-07805 |

| 1      | U48                          | 75 <b>452 dual per</b> iph NAND drvr | 30300-00452 |

| Capac  | itors                        |                                      | ,           |

| 6      | C1,C5,C17-20                 | Tantalum, 4.7uf, 35v, 20\$           | 42804-54756 |

| 14     | C2-4,C6-8,<br>C11-16,C21,C22 | Mono, .1uf, 50v, 20\$                | 42034-21046 |

| 2      | C11-18,C21,C22<br>C9,C10     | Mica. 56pf, 500v, 10\$               | 42215-55605 |

•

•

-

| QTY   | REF                                         | DESCRIPTION                    | CCS PART #  |

|-------|---------------------------------------------|--------------------------------|-------------|

| Resis | tors                                        |                                |             |

| 2     | R1,R2                                       | 10 ohm, 1/4 W, 5%              | 40002-01005 |

| ç     | R3,R5-7,                                    | 2.7K ohm, 1/4 W, 5%            | 40002-02725 |

| ţ     | R9,R12-15<br>R4                             | 680 ohm, 1/4 W, 5%             | 40002-06815 |

| 1     | RS                                          | 1 megohm, 1/4 W, 5%            | 40002-01055 |

| 2     | R10,R11                                     | 1K ohm, 1/4 W, 5%              | 40002-01025 |

| 5     | RP1-5                                       | 2.7K ohm x 7, SIP, 20%         | 40930-72725 |

| Socke | ts                                          |                                |             |

| 5     | xu1,2,4,5,48                                | 8 pin                          | 58102-00080 |

| 1 S   | XU7,9,14,15,<br>27,30,31,33-<br>38,40-43,46 | 14 pin                         | 58102-00140 |

| 7     | XU3,6,8,17,                                 | 16 pin                         | 58102-00160 |

| 13    | 29,32,XCJ1<br>XU10-13,18,22-                | 20 pin                         | 58102-00200 |

| 1     | 26,39,44,45<br>XU21                         | 24 pin                         | 58102-00240 |

| 1     | XU19                                        | 28 pin                         | 58102-00280 |

| 1     | XU20                                        | 40 pin                         | 58102-00400 |

| Misce | llaneous                                    | ,                              |             |

| 1     | X 1                                         | Crystal, 2.4576 mHz            | 48132-45762 |

| 1     | CJ1                                         | Header, 16 Pin                 | 55000-10000 |

| 1     | CJI                                         | Header Cover, 16 Pin           | 55000-10001 |

| 4     | J3-6                                        | Conn, 2 x 7, rt angle          | 55000-02070 |

| 2     | J1,2                                        | Conn, 2 x 13, rt angle         | 55000-02130 |

| 48    |                                             | Conn, Molex, 1 x 3             | 56004-01003 |

| 10    |                                             | Conn, Mołex, 1 x 4             | 56004-01004 |

| 58    |                                             | Berg jumper plugs              | 56200-00001 |

| 1     | XU47                                        | Heatsink, 220 .5" blk anodized | 60022-00001 |

| 1     |                                             | Screw, 6-32 x 5/16"            | 71006-32051 |

| ,     |                                             | Nut, hex, KEP 6-32             | 73006-32001 |

| 1     |                                             | Extractor, PCB, non-locking    | 60010-00001 |

| 2     |                                             | the denoity foot, non focking  |             |

|       |                                             | Roll pin extractor mounting    | 60010-00000 |

•

A.4 DEFINITION OF RS-232-C INTERFACE CONFIGURATION TYPES

| A      | Transmit Only                                                                                                                                                                                                                                                                                               |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| в      | Transmit Only*                                                                                                                                                                                                                                                                                              |

| С      | Receive Only                                                                                                                                                                                                                                                                                                |

| D      | Half Duplex; or Duplex*                                                                                                                                                                                                                                                                                     |

| E<br>F | Full Duplex                                                                                                                                                                                                                                                                                                 |

|        | Primary Channel Transmit Only* /Secondary Channel Receive Only                                                                                                                                                                                                                                              |

| G      | Primary Channel Receive Only / Secondary Channel Transmit Only*                                                                                                                                                                                                                                             |

| Н      | Primary Channel Transmit Only / Secondary Channel Receive Only                                                                                                                                                                                                                                              |

| I      | Primary Channel Receive Only / Secondary Channel Transmit Only                                                                                                                                                                                                                                              |

| J      | Primary Channel Transmit Only* / Half Duplex Secondary Channel                                                                                                                                                                                                                                              |

| К      | Primary Channel Receive Only / Half Duplex Secondary Channel                                                                                                                                                                                                                                                |

| L<br>L | Half Duplex Primary Channel / Half Duplex Secondary Channel; or                                                                                                                                                                                                                                             |

| M      | Duplex Primary Channel* / Duplex Secondary Channel*<br>Duplex Primary Channel / Duplex Secondary Channel                                                                                                                                                                                                    |

| Z      | Special (Circuits specified by supplier)                                                                                                                                                                                                                                                                    |

| 2      | special (circuits specified by supplier)                                                                                                                                                                                                                                                                    |

|        | *Note the inclusion below of Reguest to Send in a Transmit Function,<br>where it would not ordinarily be expected, but could indicate a<br>non-transmit mode to the data communications equipment (DCE) to<br>permit it to remove a line signal or to send synchronizing or framing<br>signals as required. |

# A.5 STANDARD INTERFACE CONFIGURATIONS FOR RS-232-C

| In                                              | terchange Circuit                                                                                                                                                                                                                                                                                                      | А                 |             |             |                  |                  |                  |           |                  |             |                  |             | ic<br>L               |                  | z           |

|-------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-------------|-------------|------------------|------------------|------------------|-----------|------------------|-------------|------------------|-------------|-----------------------|------------------|-------------|

| АА<br>АВ                                        | Protective Ground<br>Signal Ground / Common Return                                                                                                                                                                                                                                                                     | -<br>x            | -<br>x      | -<br>x      | x                | -<br>x           | -<br>x           | x         | -<br>x           | -<br>x      | -<br>x           | x           | x                     | x                | ×           |

| BA<br>BB                                        | Transmitted Data<br>Received Data                                                                                                                                                                                                                                                                                      | x                 | х           |             |                  |                  |                  | х         |                  |             |                  |             | X<br>X                | X<br>X           |             |

| CA<br>CB<br>CC<br>CD<br>CE<br>CF<br>CG<br>CH/CI | Request to Send<br>Clear to Send<br>Data Set Ready<br>Data Terminal Ready<br>Ring Indicator<br>Received Line Signal Detector<br>Signal Quality Detector<br>Data Signalling Rate Selector (DTE/DCE)                                                                                                                     | X<br>S            | X<br>X<br>S | X<br>S<br>S | X<br>X<br>S<br>S | X<br>X<br>S<br>S | X<br>X<br>S<br>S | S<br>s    | X<br>X<br>S<br>S | X<br>S<br>s | X<br>X<br>S<br>S | X<br>S<br>s | X                     | X<br>X<br>S<br>S | 0<br>0      |

| DA/DB<br>DD                                     | Transmit Signal Element Timing (DTE/DCE)<br>Receiver Signal Element Timing (DCE)                                                                                                                                                                                                                                       | Т                 | Т           |             | T<br>T           | T<br>T           |                  |           | Т                | т           | Т                | T<br>T      | T<br>T                | T<br>T           | 0           |

| SBA<br>SBB<br>SCA<br>SCB<br>SCF                 | Secondary Transmitted Data<br>Secondary Received Data<br>Secondary Reguest to Send<br>Secondary Clear to Send<br>Secondary Received Line Signal Detector                                                                                                                                                               |                   |             |             |                  |                  |                  | x         |                  | x           | x<br>x<br>x      | x<br>x<br>x | ×<br>×<br>×<br>×<br>× | x<br>x           | 0<br>0<br>0 |

|                                                 | Notes:<br>Upper case indicates a line supported by<br>Lower case indicates a line not supporte<br>X = Basic interchange circuits, all syst<br>T = Additional interchange circuits requ<br>S = Additional interchange circuits requ<br>O = Specified by supplier as required<br>- = Optional; supported by the CCS 2718 | d 1<br>em:<br>ir( | s<br>ed     | t)<br>fo    | ne<br>or         | C(               | cs<br>yno        | 27<br>chi | roi              | 101         | us<br>sei        | cl<br>rv    | har                   | חח:<br>פ         | 21          |

A-6

•

•

,

# A.6 RS-232-C CONNECTOR PINOUT

.

| PROTECTIVE GROUND    | AA 🕚 1        | 0        |                |                            |

|----------------------|---------------|----------|----------------|----------------------------|

| TRANSMIT DATA        | BA ●2         |          | 14 SBA         | SEC TRANSMIT DATA          |

| TRANSMIT DATA        |               | 0        | 15 • DB        | TRANSMIT SIG ELE CLK (DCE) |

| RECEIVE DATA         | <u>₿</u> В ●3 | 0        | 16 SBB         | SEC RECEIVE DATA           |

| REQUEST TO SEND      | CA •4         | 0        |                | SEO RECEIVE DAIR           |

|                      |               | 0        | 17 O DD        | RECEIVE SIG ELE CLK (DCE)  |

| CLEAR TO SEND        |               | 0        | 18 —           | UNASSIGNED                 |

| DATA SET READY       | CC 06         | 0        |                |                            |

| SIGNAL GROUND        | AB •7         | 0        | 19 <u>SCA</u>  | SEC REQUEST TO SEND        |

|                      | _             | 0        | 20 <b>O CD</b> | DATA TERMINAL READY        |

| REC LINE SIG DET     | CF <b>0</b> 8 | 0        | 21 CG          | SIGNAL QUALITY DETECTOR    |

| RESERVED             | - 9           | $\odot$  |                |                            |

| RESERVED             | - 10          | © 0      | 22 <u>CE</u>   | RING INDICATOR             |

| RESERVED             | - 10          | <b>0</b> | 23 CH/CI       | DATA RATE SELECT           |

| UNASSIGNED           | - 11          | 0        |                | TRANSMIT SIG ELE CLK (DTE) |

| SEC REC LINE SIG DET | SCF 12        | 0        | 24 <b>D</b> A  | TRANSMIT SIG ELE CLK (DTE) |

|                      |               | 0        | 25 —           | UNASSIGNED                 |

| SEC CLEAR TO SEND    | SCB 13        | 0        |                |                            |

FRONT VIEW

DB-25S (FEMALE)

Supported by Ports A and B.

Supported by Port B only.

•

# A.7 SERIAL CONNECTOR PINOUTS

|                                 | i  |             |      |    |                               |

|---------------------------------|----|-------------|------|----|-------------------------------|

| PROTECTIVE<br>GROUND            | AA | <b>G</b> 1  | 2 O  |    |                               |

| TRANSMIT<br>DATA                | BA | • 3         | 4 0  | DB | TRANSMIT SIG<br>EL CLK (DCE)  |

| RECEIVE<br>DATA                 | BB | 05          | 6 0  |    |                               |

| REQUEST TO<br>SEND              | CA | 07          | 8 🔾  | DD | RECEIVE SIG<br>EL CLK (DCE) + |

| CLEAR TO                        | СВ | 09          | 10 🛛 |    |                               |

| <pre># DATA SET     READY</pre> | CC | • 11        | 12 🛛 |    |                               |

| SIGNAL<br>GROUND                | AB | • 13        | 14 O | CD | DATA TERMINAL<br>READY #      |

| # REC LINE<br>SIG DET           | CF | • 15        | 16 🛛 |    |                               |

|                                 |    | 0 17        | 18 👁 |    |                               |

|                                 |    | <b>O</b> 19 | 20 🛛 |    |                               |

|                                 |    | • 21        | 22 O | DA | TRANSMIT SIG<br>EL CLK (DTE)  |

|                                 |    | • 23        | 24 O |    |                               |

|                                 |    | • 25        | 26 🛛 |    |                               |

|                                 |    | L           |      |    |                               |

# Supported by Port B only.

.

•

# A.S. PARALLEL CONNECTOR PINOUTS

.

.

|               | (  | DUTF | TUY |    |                |

|---------------|----|------|-----|----|----------------|

|               |    |      |     |    |                |

| GROUND        | 1  | 0    | 0   | 2  | GROUND         |

| DATA ACCEPTED | 3  | 0    | 0   | 4  | DATA AVAILABLE |

| ENABLE        | 5  | •    | 0   | 6  | ENABLE         |

| D6            | 7  | 0    | 0   | 8  | D7             |

| D4            | 9  | 0    | 0   | 10 | D5             |

| D2            | n  | •    | 0   | 12 | D3             |

| DO            | 13 | e    | 0   | 14 | D 1            |

|               |    |      |     |    |                |

####

INPUT

| GROUND      | I  | 0 | • | 2  | GROUND      |

|-------------|----|---|---|----|-------------|

| INPUT EMPTY | 3  | 0 | 0 | 4  | DATA STROBE |

| NOT USED    | 5  | 0 | 0 | 6  | NOT USED    |

| D6          | 7  | 0 | 0 | 8  | D7          |

| D4          | 9  | 0 | 0 | 10 | D5          |

| D2          | 11 | 0 | 0 | 12 | D3          |

| DO          | 13 | 0 | 0 | 14 | D 1         |

|             |    |   |   |    |             |

TECHNICAL INFORMATION

.

# APPENDIX B

# UART/USART INTERNAL OPERATION

B.1 THE UART

FIGURE B 1

#### B.1.1 UART Transmitter Cycle

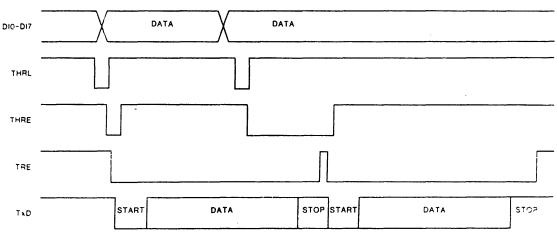

A UART transmitter cycle begins when the processor pulls SAW\* low. SAW\*, through THRL\*, shifts the character on the data bus into the Transmitter Holding Register (TXHF), and from there to the Transmitter Register (TXR) when transmission of the previous character has been completed. [For expansions of the signal mnemonics and descriptions of the signal functions, see Table B.1, pages B-4 and B-5.] When THRL\* goes high, THRE goes low. The transfer of data into the TxR is signaled by TRE going low and THRE going high again. TRE going low causes the generation of the start bit, the high-to-low transition of which signals the beginning of serial data transmission over TRO. TRE goes high again when the stop bit has been transmitted, enabling the transfer of the next character from the TxHR. The new character can be loaded into the TxHR anytime after THRE goes high, and so may be loaded before transmission of the previous character is completed.

UART TRANSMITTER TIMING

#### FIGURE B 2

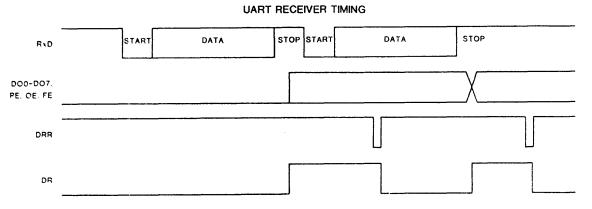

#### B.1.2 UART Receiver Cycle

The processor begins a receiver cycle by pulling SAR\* low. If the DR output is low, indicating that the RxHR is emoty, RTS will be forced high, signaling to the peripheral

#### UART/USART INTERNAL OPERATION