# Synergy Software Package (SSP)

Datasheet

Renesas Synergy<sup>™</sup> Platform Synergy Software SSP v1.2.0

All information contained in these materials, including products and product specifications, represents information on the product at the time of publication and is subject to change by Renesas Electronics Corp. without notice. Please review the latest information published by Renesas Electronics Corp. through various means, including the Renesas Electronics Corp. website (http://www.renesas.com).

Renesas Electronics www.renesas.com

Rev.1.38 May 2017

#### Notice

- 1. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation or any other use of the circuits, software, and information in the design of your product or system. Renesas Electronics disclaims any and all liability for any losses and damages incurred by you or third parties arising from the use of these circuits, software, or information.

- Renesas Electronics hereby expressly disclaims any warranties against and liability for infringement or any other disputes involving patents, copyrights, or other intellectual property rights of third parties, by or arising from the use of Renesas Electronics products or technical information described in this document, including but not limited to, the product data, drawing, chart, program, algorithm, application examples.

- 3. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 4. You shall not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part. Renesas Electronics disclaims any and all liability for any losses or damages incurred by you or third parties arising from such alteration, modification, copy or otherwise misappropriation of Renesas Electronics products.

- 5. Renesas Electronics products are classified according to the following two quality grades: "Standard" and "High Quality". The intended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below.

"Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots etc.

"High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control (traffic lights); large-scale communication equipment; key financial terminal systems; safety control equipment; etc.

Renesas Electronics products are neither intended nor authorized for use in products or systems that may pose a direct threat to human life or bodily injury (artificial life support devices or systems, surgical implantations etc.), or may cause serious property damages (space and undersea repeaters; nuclear power control systems; aircraft control systems; key plant systems; military equipment; etc.). Renesas Electronics disclaims any and all liability for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for which the product is not intended by Renesas Electronics.

- 6. When using the Renesas Electronics products, refer to the latest product information (data sheets, user's manuals, application notes, "General Notes for Handling and Using Semiconductor Devices" in the reliability handbook, etc.), and ensure that usage conditions are within the ranges specified by Renesas Electronics with respect to maximum ratings, operating power supply voltage range, heat radiation characteristics, installation, etc. Renesas Electronics disclaims any and all liability for any malfunctions or failure or accident arising out of the use of Renesas Electronics products beyond such specified ranges.

- 7. Although Renesas Electronics endeavors to improve the quality and reliability of Renesas Electronics products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please ensure to implement safety measures to guard them against the possibility of bodily injury, injury or damage caused by fire, and social damage in the event of failure or malfunction of Renesas Electronics products, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures by your own responsibility as warranty for your products/system. Because the evaluation of microcomputer software alone is very difficult and not practical, please evaluate the safety of the final products or systems manufactured by you.

- 8. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please investigate applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive carefully and sufficiently and use Renesas Electronics products in compliance with all these applicable laws and regulations. Renesas Electronics disclaims any and all liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 9. Renesas Electronics products and technologies shall not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations. You shall not use Renesas Electronics products or technologies for (1) any purpose relating to the development, design, manufacture, use, stockpiling, etc., of weapons of mass destruction, such as nuclear weapons, chemical weapons, or biological weapons, or missiles (including unmanned aerial vehicles (UAVs)) for delivering such weapons, (2) any purpose relating to the development, design, manufacture, or use of conventional weapons, or (3) any other purpose of disturbing international peace and security, and you shall not sell, export, lease, transfer, or release Renesas Electronics products or technologies to any third party whether directly or indirectly with knowledge or reason to know that the third party or any other party will engage in the activities described above. When exporting, selling, transferring, etc., Renesas Electronics products or technologies, you shall comply with any applicable export control laws and regulations promulgated and administered by the governments of the countries asserting jurisdiction over the parties or transactions.

- 10. Please acknowledge and agree that you shall bear all the losses and damages which are incurred from the misuse or violation of the terms and conditions described in this document, including this notice, and hold Renesas Electronics harmless, if such misuse or violation results from your resale or making Renesas Electronics products available any third party.

- 11. This document shall not be reprinted, reproduced or duplicated in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majority-owned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

Renesas Synergy<sup>™</sup> Platform

Synergy Software Package (SSP) v1.2.0

R01DS0272EU0138 Rev 1.38 May 5, 2017

## Contents

| 1. | Desc | criptio          | on of Renesas Synergy <sup>™</sup> Software Package1 | 2          |

|----|------|------------------|------------------------------------------------------|------------|

|    | 1.1  | Key              | / Features                                           | 13         |

|    | 1.2  | Intro            | oduction to this Software Datasheet                  | 15         |

|    | 1.2. | 1                | Memory Size Estimation                               | 15         |

|    | 1.2. | 2                | Software Quality Assurance and Test Data             | 16         |

| 2. | Thre | adX <sup>∉</sup> | <sup>®</sup> RTOS1                                   | 17         |

|    | 2.1  | Intro            | oduction to ThreadX and X-ware                       | 17         |

|    | 2.2  | Cor              | nponent Introduction                                 | 17         |

|    | 2.2. | 1                | ThreadX Certifications                               | 17         |

|    | 2.2. | 2                | ThreadX <sup>®</sup> API                             | 17         |

|    | 2.2. | 3                | Thread Services                                      | 18         |

|    | 2.2. | 4                | Message Queues                                       | 18         |

|    | 2.2. | 5                | Counting Semaphores                                  | 18         |

|    | 2.2. | 6                | Mutexes                                              | 18         |

|    | 2.2. | 7                | Event Flags                                          | 18         |

|    | 2.2. | 8                | Block Memory Pools                                   | 18         |

|    | 2.2. | 9                | Byte Memory Pools                                    | 18         |

|    | 2.2. | 10               | Application Timers                                   | 18         |

|    | 2.2. | 11               | ThreadX Core Scheduler                               | 18         |

|    | 2.3  | Esti             | imated Memory Requirements                           | 19         |

| 3. | NetX | <sup>™</sup> E   | mbedded TCP/IP and UDP Stacks                        | 20         |

|    | 3.1  | Cor              | nponent Introduction                                 | 20         |

| 4. | NetX | (™ [             | Duo™ Dual IPv4/IPv6 Stack2                           | 21         |

|    | 4.1  | Cor              | nponent Introduction2                                | 21         |

|    | 4.2  | Esti             | imated Memory Requirements                           | 22         |

| 5. | NetX | (™ A             | pplications Bundle                                   | 23         |

|    | 5.1  | Cor              | nponent Introduction                                 | 23         |

|    | 5.2  | Esti             | imated Memory Requirements2                          | <u>2</u> 4 |

| 6. | NetX | Duc              | o <sup>™</sup> Applications Bundle2                  | 25         |

|    | 6.1  | Cor              | nponent Introduction                                 | 25         |

|     | 6.2   | Estimated Memory Requirements                | 26 |

|-----|-------|----------------------------------------------|----|

| 7.  | FileX | <sup>(®</sup> Embedded File System           | 27 |

|     | 7.1   | Component Introduction                       | 27 |

|     | 7.2   | Estimated Memory Requirements                | 28 |

| 8.  | GUI   | K™ GUI Development Toolkit                   | 29 |

|     | 8.1   | Component Introduction                       | 29 |

|     | 8.2   | Estimated Memory Requirements                | 30 |

| 9.  | USB   | Χ™                                           | 32 |

|     | 9.1   | Component Introduction                       | 32 |

|     | 9.2   | Estimated Memory Requirements for USBX Stack | 33 |

| 10. | laaA  | ication Frameworks                           | 35 |

|     | 10.1  | Introduction                                 |    |

|     | 10.2  | Audio Playback Framework                     | 35 |

|     | 10.2  | 2.1 Overview of the SSP Audio Playback Stack | 35 |

|     | 10.2  | 2.2 Component Introduction                   | 36 |

|     | 10.2  | 2.3 Estimated Memory Requirements            | 37 |

|     | 10.3  | Inter-Thread Messaging Framework             | 37 |

|     | 10.3  | 3.1 Component Introduction                   | 37 |

|     | 10.3  | 3.2 Estimated Memory Requirements            | 38 |

|     | 10.4  | I2C Framework                                | 38 |

|     | 10.4  | 4.1 Component Introduction                   | 38 |

|     | 10.4  | 4.2   Estimated Memory Requirements          | 39 |

|     | 10.5  | Touch Panel I <sup>2</sup> C Framework       | 39 |

|     | 10.5  | 5.1 Component Introduction                   | 39 |

|     | 10.5  | 5.2 Estimated Memory Requirements            | 40 |

|     | 10.6  | External Interrupt Framework                 | 40 |

|     | 10.6  | 6.1 Component Introduction                   | 40 |

|     | 10.6  | 6.2 Estimated Memory Requirements            | 41 |

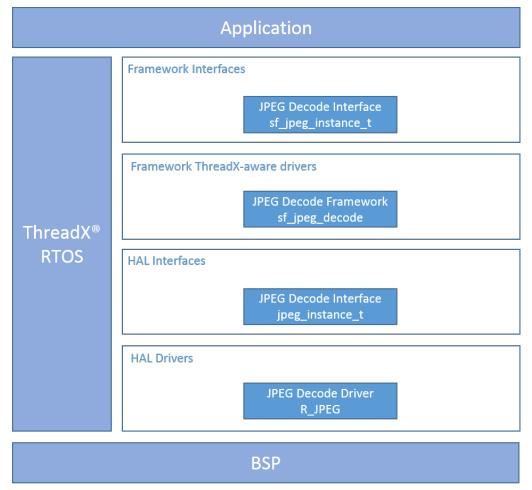

|     | 10.7  | JPEG Decode Framework                        | 42 |

|     | 10.7  |                                              |    |

|     | 10.7  | 7.2 Estimated Memory Requirements            | 42 |

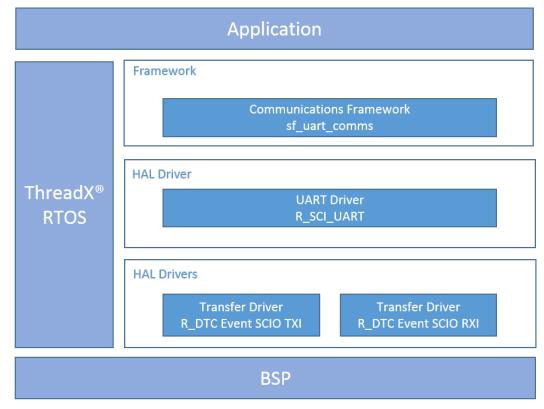

|     | 10.8  | UART Framework                               | 43 |

|     | 10.8  |                                              |    |

|     | 10.8  | 3.2 Estimated Memory Requirements            | 43 |

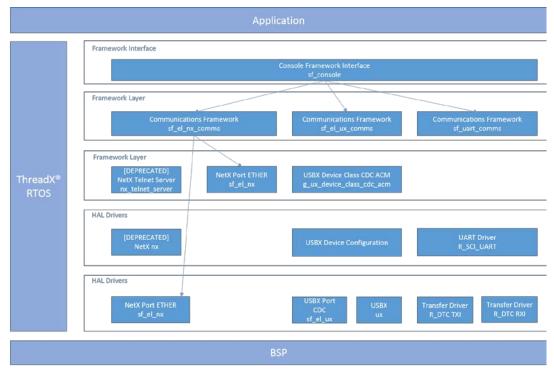

|     | 10.9  | Console Framework                            | 44 |

| 10.9.1    | Component Introduction                       | . 44 |

|-----------|----------------------------------------------|------|

| 10.9.2    | Estimated Memory Requirements                | . 45 |

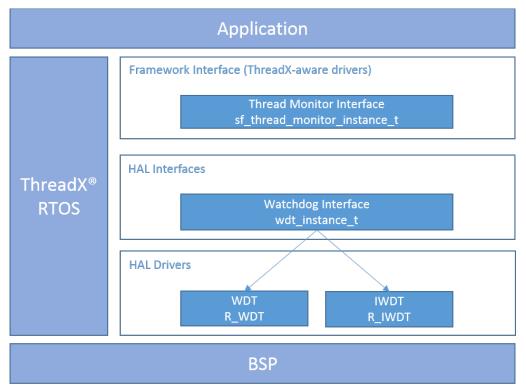

| 10.10 Thr | ead Monitor Framework                        | . 45 |

| 10.10.1   | Component Introduction                       | . 45 |

| 10.10.2   | Estimated Memory Requirements                | . 46 |

| 10.11 AD  | C Periodic Framework                         | . 46 |

| 10.11.1   | Component Introduction                       | . 46 |

| 10.11.2   | Estimated Memory Requirements                | . 47 |

| 10.12 Auc | lio Playback HW DAC Framework                | . 47 |

| 10.12.1   | Component Introduction                       | . 47 |

| 10.12.2   | Estimated Memory Requirements                | . 48 |

| 10.13 Auc | lio Playback HW I <sup>2</sup> S Framework   | . 48 |

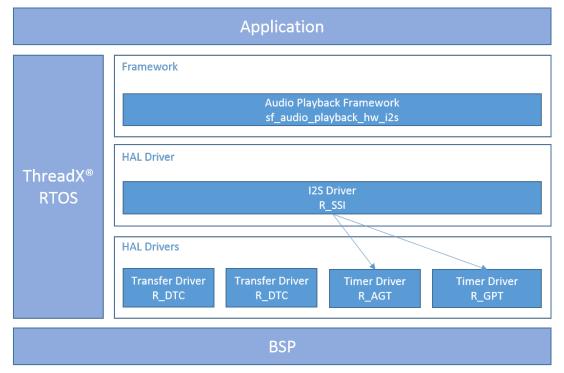

| 10.13.1   | Component Introduction                       | . 48 |

| 10.13.2   | Estimated Memory Requirements                | . 49 |

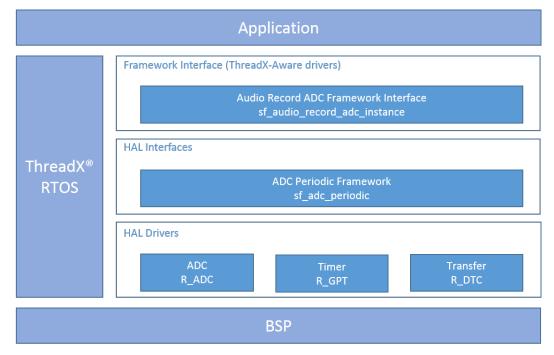

| 10.14 Auc | lio Record HW ADC Framework                  | . 49 |

| 10.14.1   | Component Introduction                       | . 49 |

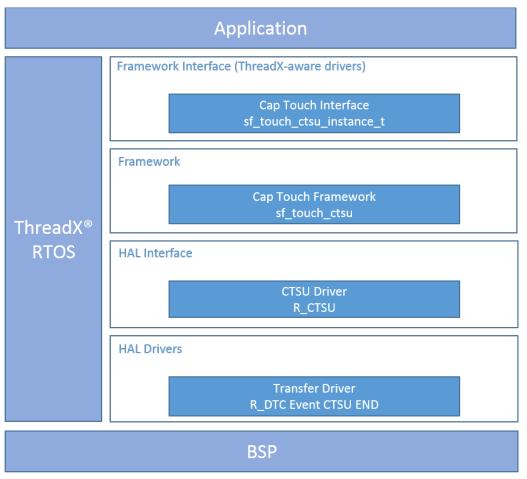

| 10.15 Cap | pacitive Touch Sensing Unit (CTSU) Framework | . 51 |

| 10.15.1   | Component Introduction                       | . 51 |

| 10.15.2   | Estimated Memory Requirements                | . 51 |

| 10.16 Cap | pacitive Touch Sensing Unit Button Framework | . 52 |

| 10.16.1   | Component Introduction                       | . 52 |

| 10.16.2   | Estimated Memory Requirements                | . 53 |

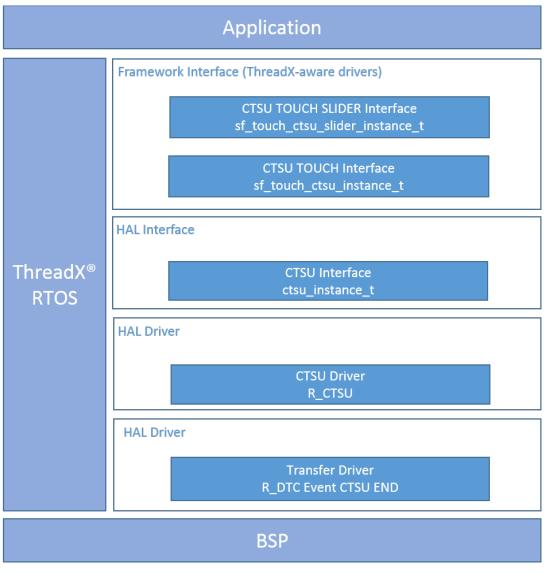

| 10.17 Cap | pacitive Touch Sensing Unit Slider Framework | . 54 |

| 10.17.1   | Component Introduction                       | . 54 |

| 10.17.2   | Estimated Memory Requirements                | . 55 |

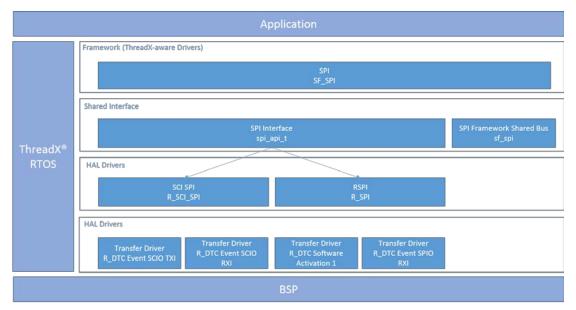

| 10.18 Ser | ial Peripheral Interface (SPI) Framework     | . 55 |

| 10.18.1   | Component Introduction                       | . 55 |

| 10.18.2   | Estimated Memory Requirements                | . 56 |

| 10.19 Pov | ver Mode Profile Framework                   | . 56 |

| 10.19.1   | Component Introduction                       | . 56 |

| 10.19.2   | Estimated Memory Requirements                | . 56 |

| 10.20 Syn | ergy FileX® Interface Framework              | . 57 |

| 10.20.1   | Component Introduction                       | . 57 |

| 10.20.2   | Estimated Memory Requirements                | . 57 |

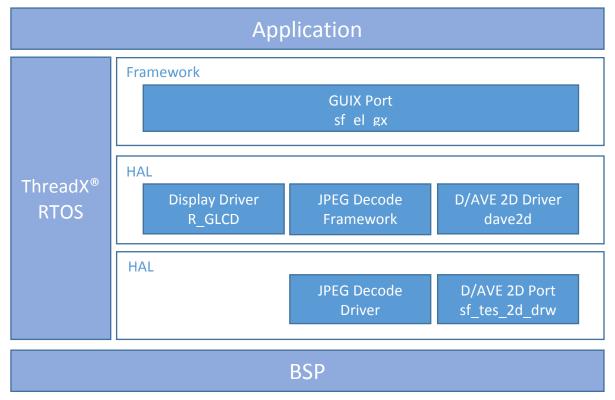

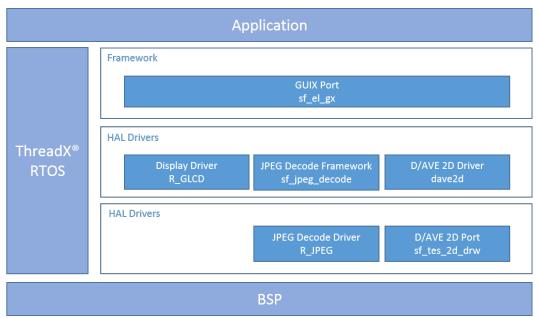

| 10.21 Syn | ergy GUIXTM Interface Framework              | . 57 |

| 10.21.1   | Component Introduction                       | . 57 |

| 10.21.2   | Estimated Memory Requirements                | . 58 |

|     | 10.22 Syn  | ergy NetXTM Communication Framework                                   | 58 |

|-----|------------|-----------------------------------------------------------------------|----|

|     | 10.22.1    | Component Introduction                                                | 58 |

|     | 10.22.2    | Estimated Memory Requirements                                         | 59 |

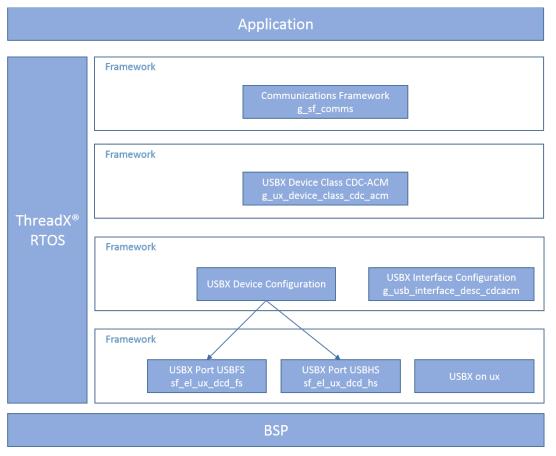

|     | 10.23 Syn  | ergy USBX Communication Framework                                     | 59 |

|     | 10.23.1    | Component Introduction                                                | 59 |

|     | 10.23.2    | Estimated Memory Requirements                                         | 60 |

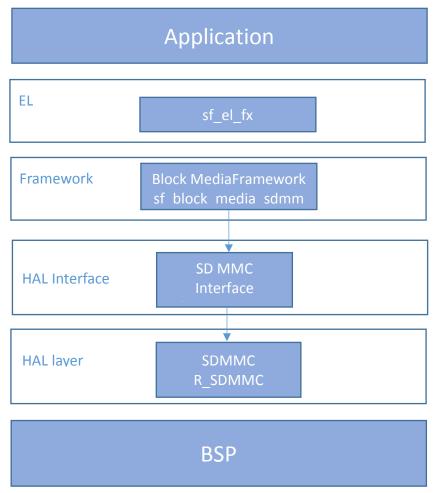

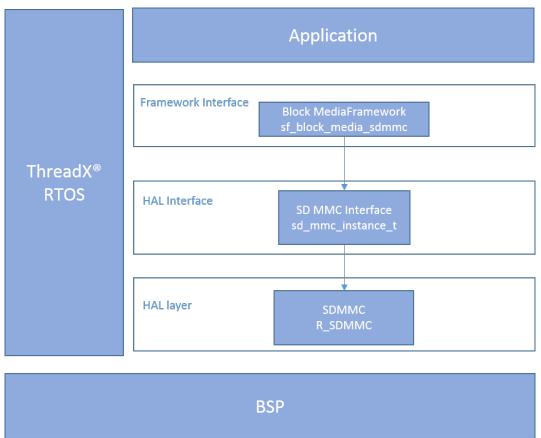

|     | 10.24 Bloc | ck Media Interface for SD/Multi Media Card                            | 60 |

|     | 10.24.1    | Component Introduction                                                | 60 |

|     | 10.24.2    | Estimated Memory Requirements                                         | 61 |

| 11. | Crypto Li  | brary                                                                 | 62 |

|     | 11.1 Cor   | nponent Introduction                                                  | 62 |

|     | 11.2 Esti  | mated Memory Requirements                                             | 63 |

| 12. | CMSIS D    | SP Library                                                            | 65 |

|     |            | nponent Introduction                                                  |    |

|     | 12.2 Esti  | mated Memory Requirements                                             | 65 |

| 13. | Hardware   | e Abstraction Layer (HAL) Modules                                     | 67 |

|     |            | oduction                                                              |    |

|     | 13.2 SD    | Multi Media Card (SDMMC)                                              | 67 |

|     | 13.2.1     | Component Introduction                                                |    |

|     | 13.2.2     | Estimated Memory Requirements                                         |    |

|     | 13.2.3     | SSP Supported Hardware Features: SD/MMC (SDIO)                        | 68 |

|     | 13.3 Clo   | ck Generation Circuit (CGC)                                           | 69 |

|     | 13.3.1     | Component Introduction                                                | 69 |

|     | 13.3.2     | Estimated Memory Requirements                                         | 70 |

|     | 13.3.3     | SSP Supported Hardware Features: Clock Generation Circuit (CGC)       | 70 |

|     | 13.4 Cap   | pacitive Touch Sensing Unit (CTSU)                                    | 71 |

|     | 13.4.1     | Component Introduction                                                | 71 |

|     | 13.4.2     | Estimated Memory Requirements                                         | 72 |

|     | 13.4.3     | SSP Supported Hardware Features: Capacitive Touch Sensing Unit (CTSU) | 72 |

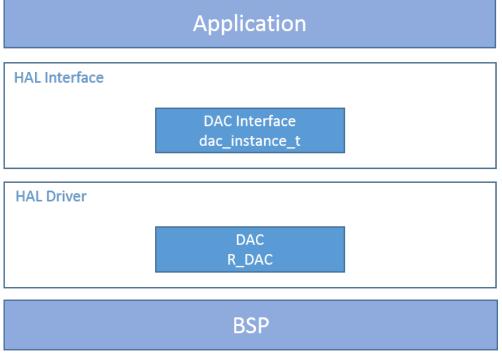

|     | 13.5 Digi  | ital to Analog convertor (DAC)                                        | 73 |

|     | 13.5.1     | Component Introduction                                                | 73 |

|     | 13.5.2     | Estimated Memory Requirements                                         | 74 |

|     | 13.5.3     | SSP Supported Hardware Features: Digital to Analog convertor (DAC)    | 74 |

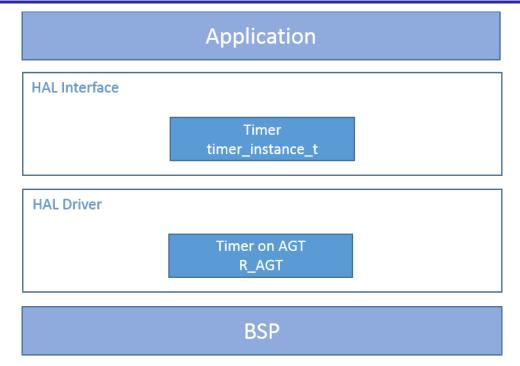

|     | 13.6 Asy   | nchronous General Purpose Timer (AGT)                                 | 74 |

|     | 13.6.1     | Component Introduction                                                | 74 |

|     | 13.6.2     | Estimated Memory Requirements                                         | 75 |

| 13.6.3    | SSP Supported Hardware Features: Asynchronous General Purpose Timer (AGT)   | . 75 |

|-----------|-----------------------------------------------------------------------------|------|

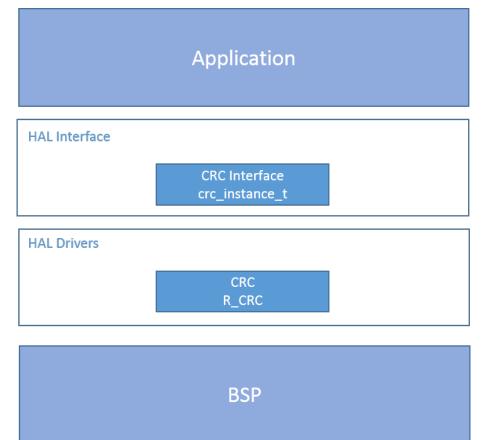

| 13.7 Cyc  | clic Redundancy Check calculator (CRC)                                      | . 76 |

| 13.7.1    | Component Introduction                                                      | . 76 |

| 13.7.2    | Estimated Memory Requirements                                               | . 77 |

| 13.7.3    | SSP Supported Hardware Features: Cyclic Redundancy Check calculator (CRC)   | . 77 |

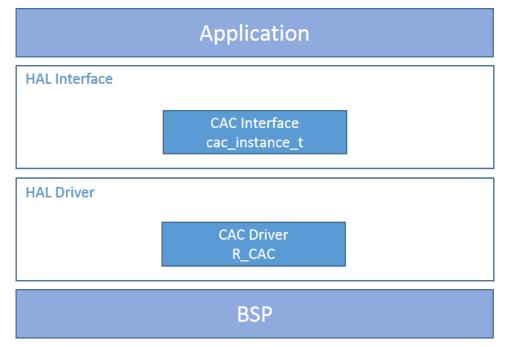

| 13.8 Clo  | ck Frequency Accuracy Measurement (CAC)                                     | . 77 |

| 13.8.1    | Component Introduction                                                      | . 77 |

| 13.8.2    | Estimated Memory Requirements                                               | . 78 |

| 13.8.3    | SSP Supported Hardware Features: Clock Frequency Accuracy Measurement (CAC) | . 79 |

| 13.9 RII  | C (I2C Full Featured)                                                       | . 79 |

| 13.9.1    | Component Introduction                                                      | . 79 |

| 13.9.2    | Estimated Memory Requirements                                               | . 81 |

| 13.9.3    | SSP Supported Hardware Features: RIIC                                       | . 81 |

| 13.10 Ser | ial Peripheral Interface (RSPI)                                             | . 82 |

| 13.10.1   | Component Introduction                                                      | . 82 |

| 13.10.2   | Estimated Memory Requirements                                               | . 83 |

| 13.10.3   | SSP Supported Hardware Features: RSPI                                       | . 83 |

| 13.11 Qua | ad SPI (QSPI)                                                               | . 84 |

| 13.11.1   | Component Introduction                                                      | . 84 |

| 13.11.2   | Estimated Memory Requirements                                               | . 85 |

| 13.11.3   | SSP Supported Hardware Features: QSPI                                       | . 85 |

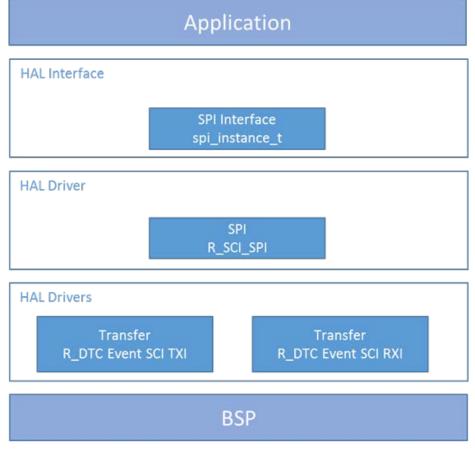

| 13.12 Rea | altime Clock (RTC)                                                          | . 86 |

| 13.12.1   | Component Introduction                                                      | . 86 |

| 13.12.2   | Estimated Memory Requirements                                               | . 87 |

| 13.12.3   | SSP Supported Hardware Features: Real Time Clock (RTC)                      | . 87 |

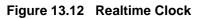

| 13.13 Seg | gment LCD (SLCDC)                                                           | . 88 |

| 13.13.1   | Component Introduction                                                      | . 88 |

| 13.13.2   | Estimated Memory Requirements                                               | . 89 |

| 13.13.3   | SSP Supported Hardware Features: Segment LCD (SLCD)                         | . 89 |

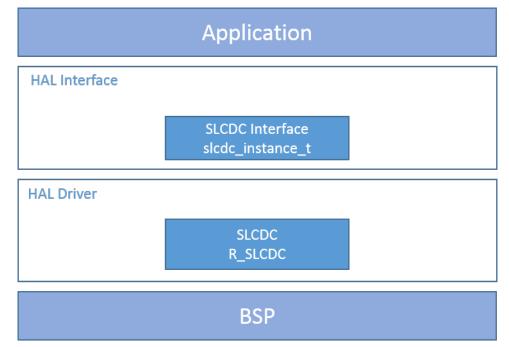

| 13.14 Ser | ial Communication Interface UART (SCI_UART)                                 | . 90 |

| 13.14.1   | Component Introduction                                                      | . 90 |

| 13.14.2   | Estimated Memory Requirements                                               | . 91 |

| 13.14.3   | SSP Supported Hardware Features: UART SCI                                   | . 92 |

| 13.15 Ser | ial Communication Interface I <sup>2</sup> C over SCI (SCI_I2C)             | . 92 |

| 13.15.1   | Component Introduction                                                      | . 92 |

| 13.15.2   | Estimated Memory Requirements                                               | . 93 |

| 13.15.3   | SSP Supported Hardware Features: I <sup>2</sup> C over SPI                  | . 93 |

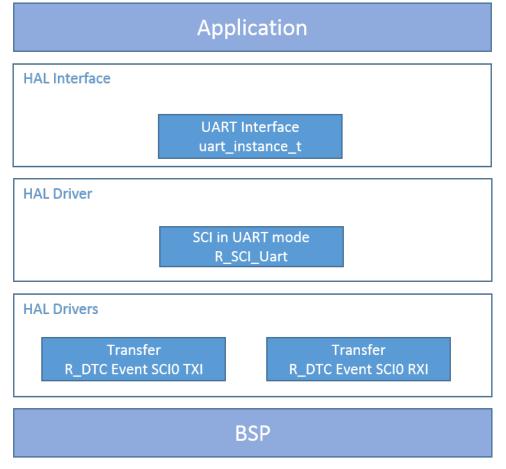

| 13.16 Ser | ial Communication Interface SPI (SCI_SPI)                                   | . 94 |

| 13.16.1    | Component Introduction                                                   |       |

|------------|--------------------------------------------------------------------------|-------|

| 13.16.2    | Estimated Memory Requirements                                            |       |

| 13.16.3    | SSP Supported Hardware Features: SCI_SPI                                 |       |

| 13.17 JPE  | EG Codec (JPEG Codec)                                                    |       |

| 13.17.1    | Component Introduction                                                   |       |

| 13.17.2    | SSP Supported Hardware Features: JPEG                                    |       |

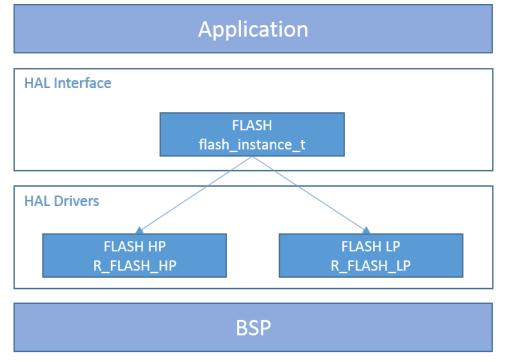

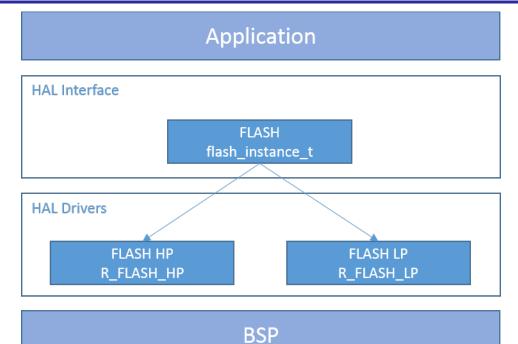

| 13.18 Flas | sh Memory-High Performance (FLASH_HP)                                    |       |

| 13.18.1    | Component Introduction                                                   |       |

| 13.18.2    | Estimated Memory Requirements                                            |       |

| 13.18.3    | SSP Supported Hardware Features: Flash Memory-High Performance (FLASH_HF | P) 99 |

| 13.19 Flas | sh Memory-Low Power (FLASH_LP)                                           |       |

| 13.19.1    | Component Introduction                                                   |       |

| 13.19.2    | Estimated Memory Requirements                                            | 100   |

| 13.19.3    | SSP Supported Hardware Features: Flash Memory-Low Power (FLASH_LP)       | 100   |

| 13.20 Dat  | a Transfer Controller (DTC)                                              | 100   |

| 13.20.1    | Component Introduction                                                   | 100   |

| 13.20.2    | Estimated Memory Requirements                                            | 101   |

| 13.20.3    | SSP Supported Hardware Features: DTC                                     | 101   |

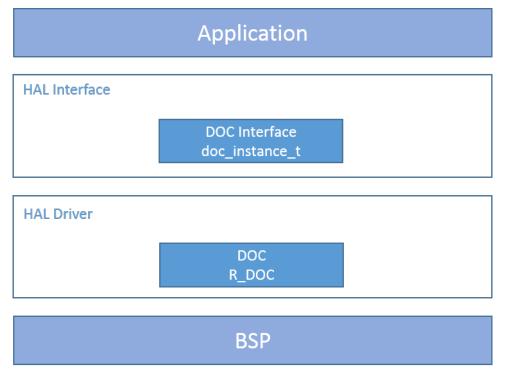

| 13.21 Dat  | a Operation Circuit (DOC)                                                | 102   |

| 13.21.1    | Component Introduction                                                   | 102   |

| 13.21.2    | Estimated Memory Requirements                                            | 103   |

| 13.21.3    | SSP Supported Hardware Features: DOC                                     | 103   |

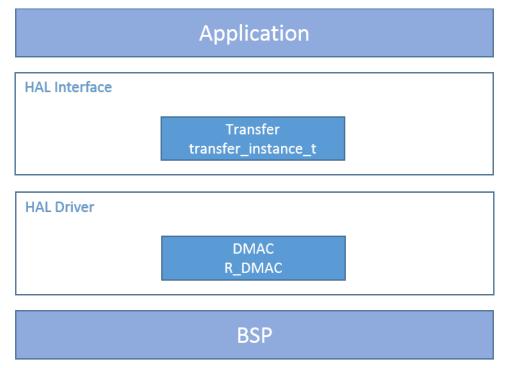

| 13.22 Dire | ect Memory Access Controller (DMAC)                                      | 103   |

| 13.22.1    | Component Introduction                                                   | 103   |

| 13.22.2    | Estimated Memory Requirements                                            | 104   |

| 13.22.3    | SSP Supported Hardware Features: DMAC                                    | 104   |

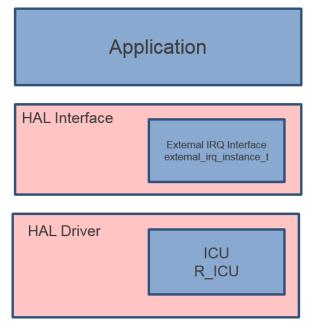

| 13.23 Inte | errupt Controller Unit (ICU)                                             | 105   |

| 13.23.1    | Component Introduction                                                   | 105   |

| 13.23.2    | Estimated Memory Requirements                                            | 105   |

| 13.23.3    | SSP Supported Hardware Features: ICU                                     | 106   |

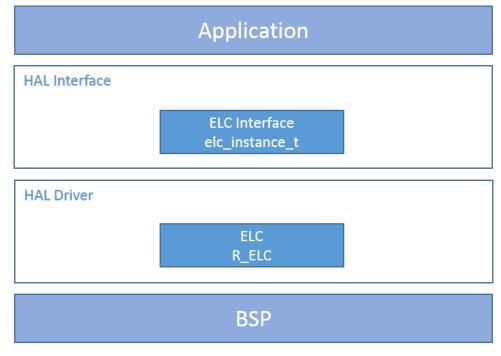

| 13.24 Eve  | ent Link Controller (ELC)                                                | 106   |

| 13.24.1    | Component Introduction                                                   | 106   |

| 13.24.2    | Estimated Memory Requirements                                            | 107   |

| 13.24.3    | SSP Supported Hardware Features: ELC                                     | 107   |

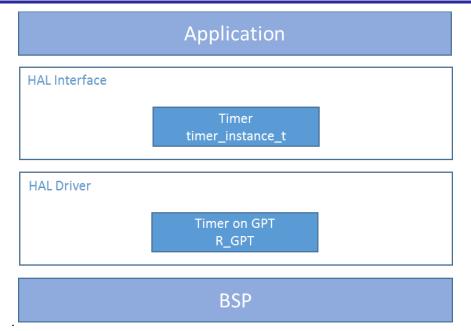

| 13.25 Ger  | neral Purpose Timer (GPT)                                                | 107   |

| 13.25.1    | Component Introduction                                                   | 107   |

| 13.25.2    | Estimated Memory Requirements                                            | 108   |

| 13.25.3    | SSP Supported Hardware Features: GPT                                     | 108   |

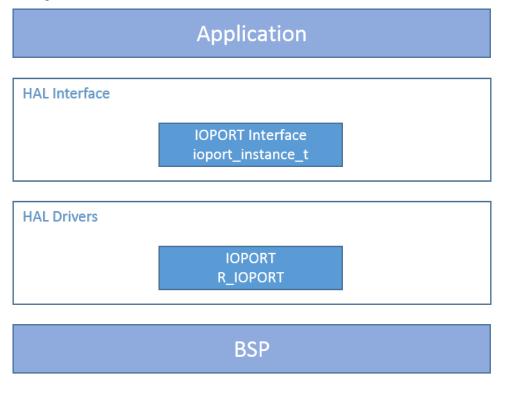

| 13.26 Ger  | neral Purpose I/O Port (GPIO / IOPORT) | 109   |

|------------|----------------------------------------|-------|

| 13.26.1    | Component Introduction                 | . 109 |

| 13.26.2    | Estimated Memory Requirements          | 110   |

| 13.26.3    | SSP Supported Hardware Features: GPIO  | . 110 |

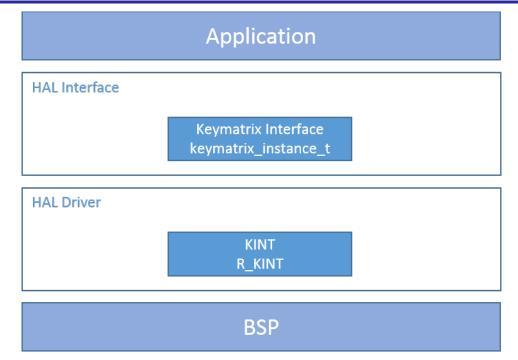

| 13.27 Key  | /board Interrupt Interface (KINT)      | 110   |

| 13.27.1    | Component Introduction                 | . 110 |

| 13.27.2    | Estimated Memory Requirements          | 111   |

| 13.27.3    | SSP Supported Hardware Features: KINT  | 111   |

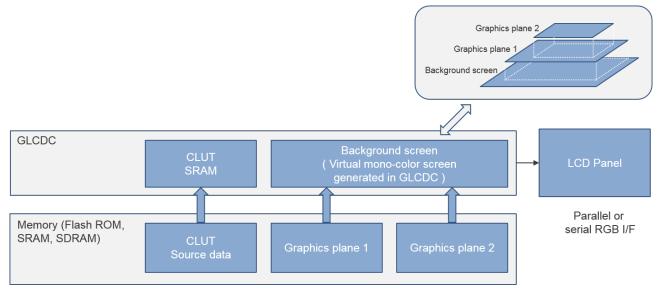

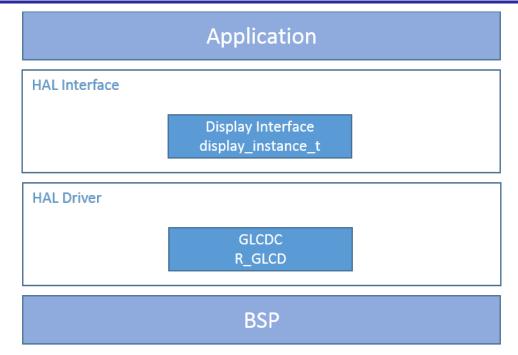

| 13.28 Gra  | phics LCD Controller (GLCD)            | 112   |

| 13.28.1    | Component Introduction                 | . 112 |

| 13.28.2    | Estimated Memory Requirements          | . 113 |

| 13.28.3    | SSP Supported Hardware Features: GLCD  | 113   |

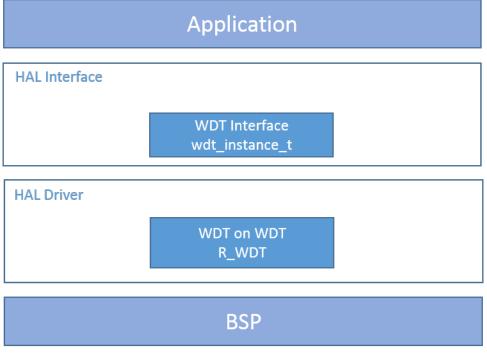

| 13.29 Wa   | tchdog Timer (WDT)                     | . 114 |

| 13.29.1    | Component Introduction                 | 114   |

| 13.29.2    | Estimated Memory Requirements          | 115   |

| 13.29.3    | SSP Supported Hardware Features: WDT   | . 115 |

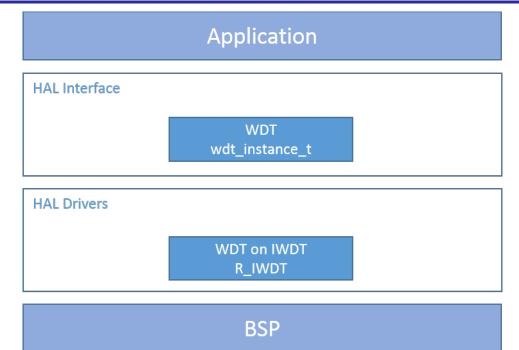

| 13.30 Inde | ependent Watchdog Timer (IWDT)         | . 115 |

| 13.30.1    | Component Introduction                 | 115   |

| 13.30.2    | Estimated Memory Requirements          | . 116 |

| 13.30.3    | SSP Supported Hardware Features: IWDT  | 116   |

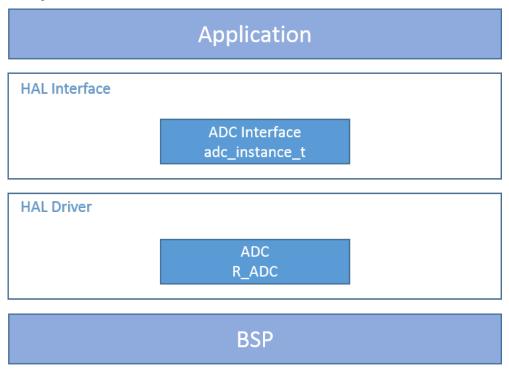

| 13.31 Ana  | alog to Digital Converter (ADC)        | 117   |

| 13.31.1    | Component Introduction                 | 117   |

| 13.31.2    | Estimated Memory Requirements          | . 118 |

| 13.31.3    | SSP Supported Hardware Features: ADC   | 118   |

| 13.32 Fac  | tory Microcontroller Information (FMI) | . 118 |

| 13.32.1    | Component Introduction                 | 118   |

| 13.32.2    | Estimated Memory Requirements          | 119   |

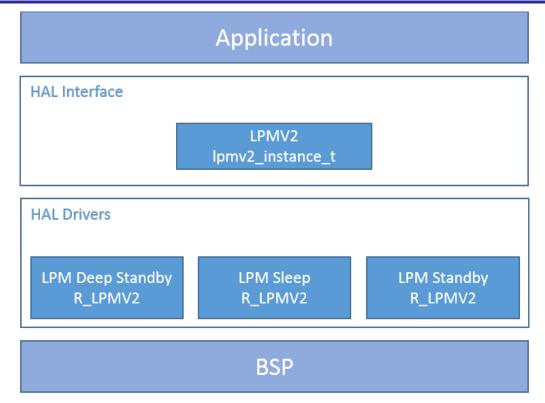

| 13.33 Low  | v Power Mode Version 2 (LPMV2)         | 119   |

| 13.33.1    | Component Introduction                 | . 119 |

| 13.33.2    | Estimated Memory Requirements          | 120   |

| 13.33.3    | SSP Supported Hardware Features: LPMV2 | . 121 |

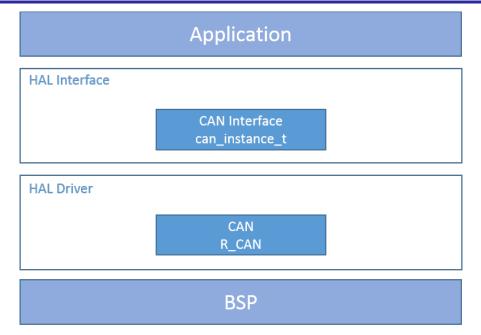

| 13.34 Cor  | ntroller Area Network (CAN)            | 121   |

| 13.34.1    | Component Introduction                 | 121   |

| 13.34.2    | Estimated Memory Requirements          | . 122 |

| 13.34.3    | SSP Supported Hardware Features: CAN   | 122   |

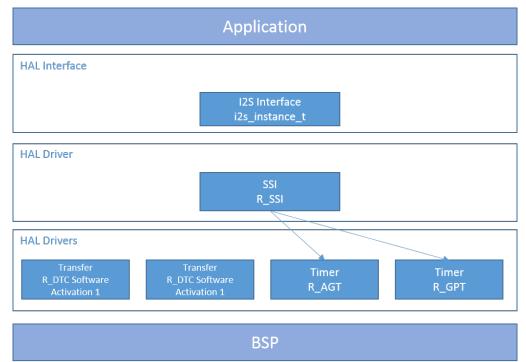

| 13.35 Ser  | ial Sound Interface (SSI)              | 123   |

| 13.35.1    | Component Introduction                 | 123   |

| 13.35.2    | Estimated Memory Requirements          | 124   |

|     | 13.35.3          | SSP Supported Hardware Features: SSI                                |     |

|-----|------------------|---------------------------------------------------------------------|-----|

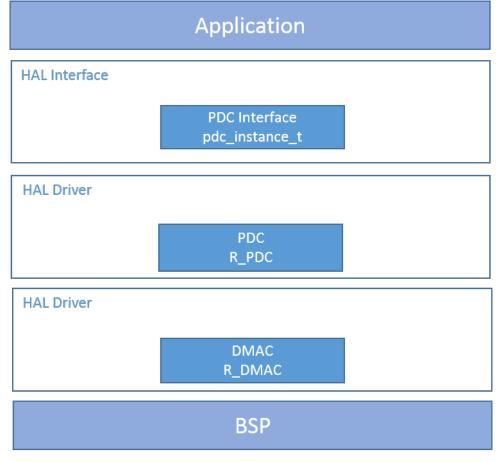

|     | 13.36 Para       | allel Data Capture Unit (PDC)                                       | 125 |

|     | 13.36.1          | Component Introduction                                              | 125 |

|     | 13.36.2          | Estimated Memory Requirements                                       | 126 |

|     | 13.36.3          | SSP Supported Hardware Features: PDC                                | 126 |

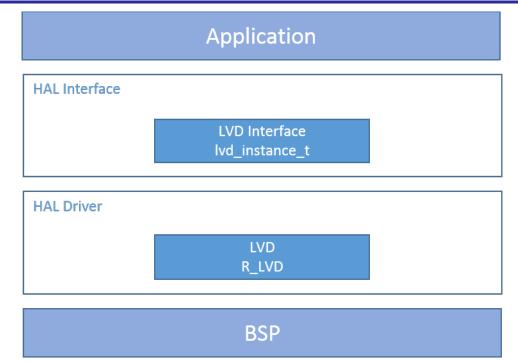

|     | 13.37 Low        | v Voltage Detection (LVD)                                           |     |

|     | 13.37.1          | Component Introduction                                              | 127 |

|     | 13.37.2          | Estimated Memory Requirements                                       |     |

|     | 13.37.3          | SSP Supported Hardware Features: LVD                                | 128 |

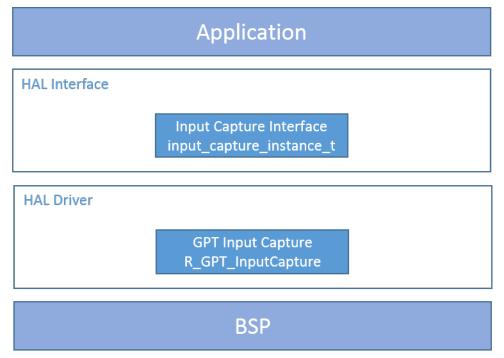

|     | 13.38 Ger        | neral PWM Timer with Input Capture (GPT_INPUT_CAPTURE)              | 129 |

|     | 13.38.1          | Component Introduction                                              |     |

|     | 13.38.2          | Estimated Memory Requirements                                       |     |

|     | 13.38.3          | SSP Supported Hardware Features: GPT_INPUT_CAPTURE                  |     |

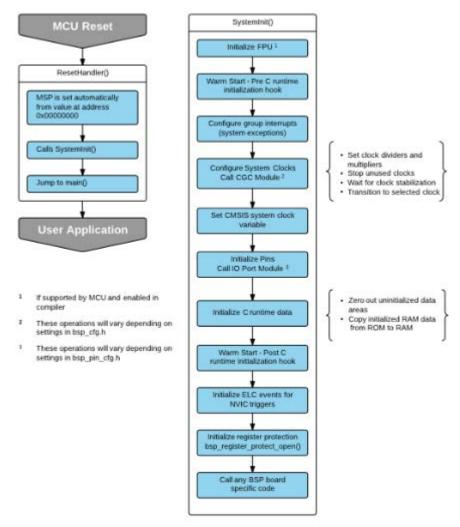

| 14. | Board Su         | pport Package (BSP)                                                 | 131 |

|     | 14.1 Con         | nponent Introduction                                                |     |

|     | 14.1.1           | Estimated Memory Requirements                                       |     |

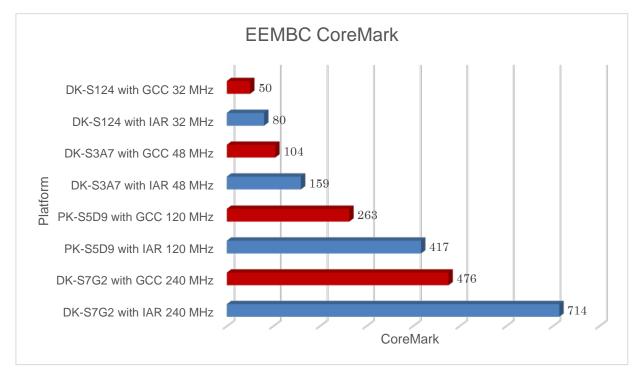

| 15. | SSP Syst         | tem Performance – Warranted                                         | 133 |

|     | 15.1 Tes         | t Environments                                                      |     |

|     | 15.2 MC          | U Measurements                                                      |     |

|     | 15.2.1           | EEMBC CoreMark <sup>®</sup>                                         |     |

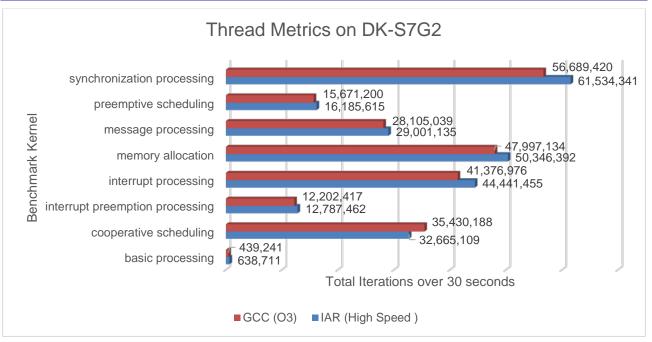

|     | 15.3 Ope         | erating System Performance Metrics.                                 | 135 |

|     | 15.3.1           | Thread-Metric Benchmarks                                            | 135 |

|     | 15.4 Net         | working Performance Metrics                                         | 140 |

|     | 15.4.1           | Metrics Covered by SSP Warranty                                     |     |

|     | 15.5 File        | System Performance Metrics                                          |     |

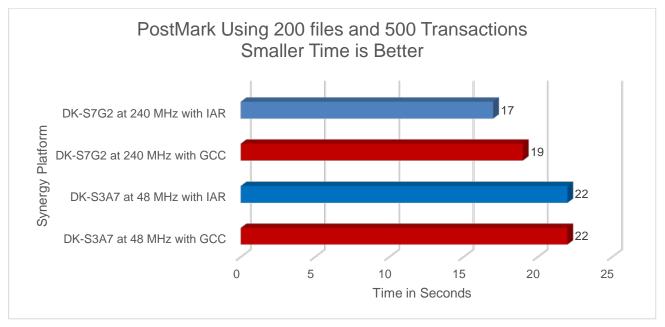

|     | 15.5.1           | Performance characterization on DK-S3A7 and DK-S7G2 kits            |     |

| 16  | SSP Svst         | tem Performance – Supplemental Reference Data (not warranted)       | 142 |

| 10. | -                | 3                                                                   |     |

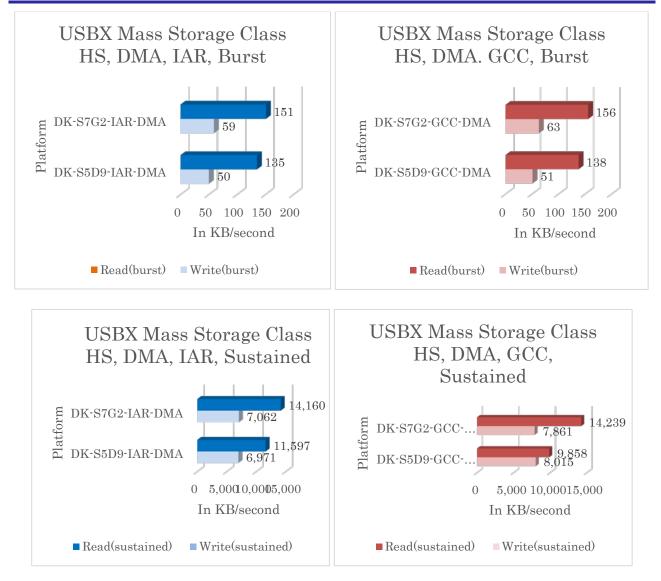

|     |                  | USBX Low Level Measurements                                         |     |

|     | 16.1.1<br>16.1.2 | USBX Low Level Measurements<br>USBX Small and Large File Operations |     |

|     |                  |                                                                     |     |

|     |                  |                                                                     |     |

|     |                  | _I2C HAL driver                                                     |     |

|     |                  | SCI_I2C Framework                                                   |     |

|     | 16.5 Cry         | ptography                                                           |     |

| Rev | ision Histo      | ory                                                                 | 147 |

| List of Figures                                                 |    |

|-----------------------------------------------------------------|----|

| Figure 1.1 Renesas Synergy™ Software Package                    | 12 |

| Figure 2.1 ThreadX <sup>®</sup> Features and Versions           | 17 |

| Figure 3.1 NetX <sup>™</sup> Stack Configuration                | 20 |

| Figure 4.1 NetX Duo <sup>™</sup> Stack Configuration            | 21 |

| Figure 7.1 FileX <sup>®</sup> Embedded File System              | 27 |

| Figure 8.1 GUIX™ Runtime Library                                | 29 |

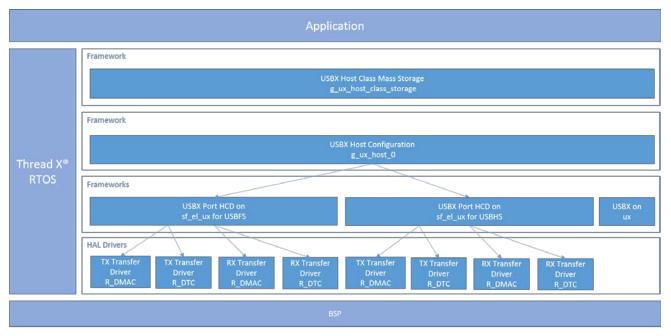

| Figure 9.1 USBX <sup>™</sup> Host Stacks for Mass Storage (MSC) |    |

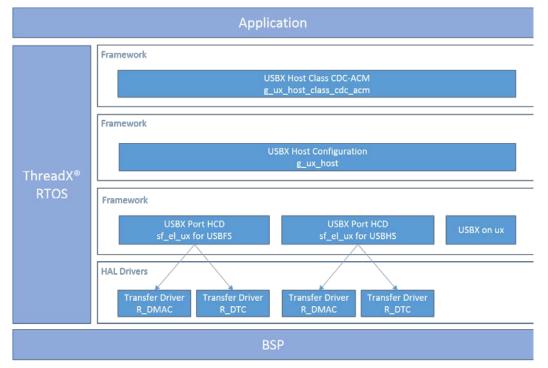

| Figure 9.2 USBX <sup>™</sup> Host Stacks for CDC ACM            | 33 |

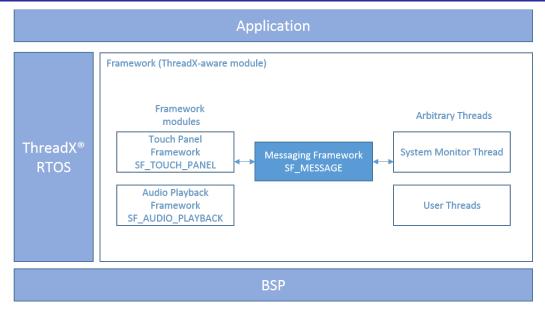

| Figure 10.1 Application Frameworks                              | 35 |

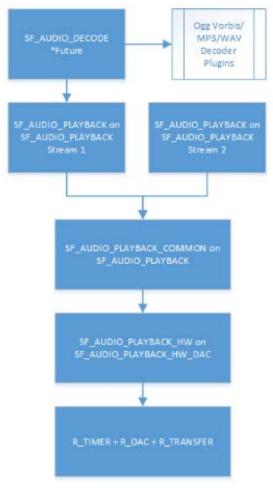

| Figure 10.2 Audio Playback Stack                                |    |

| Figure 10.3 Inter-Thread Messaging Framework                    |    |

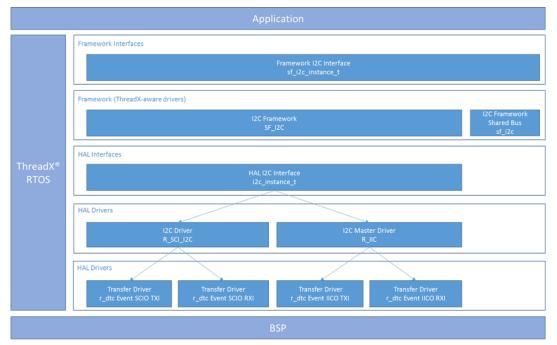

| Figure 10.4 I <sup>2</sup> C Framework                          | 39 |

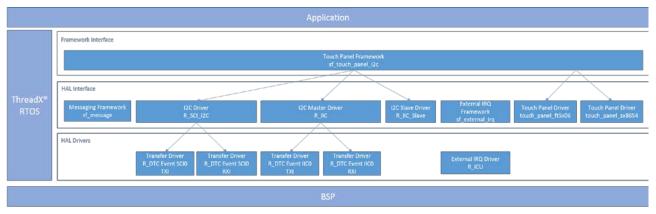

| Figure 10.5 Touch Panel I <sup>2</sup> C Framework              | 40 |

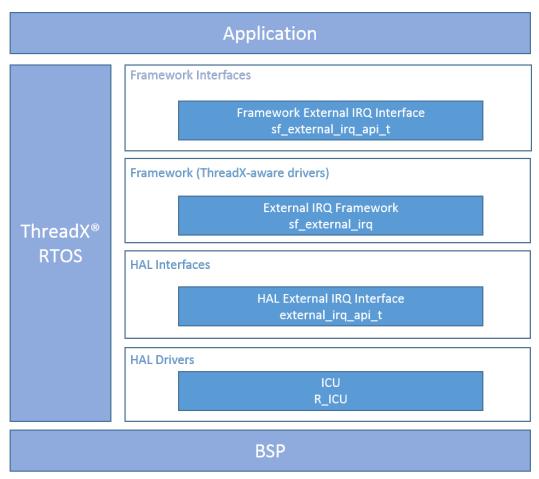

| Figure 10.6 External Interrupt Framework                        | 41 |

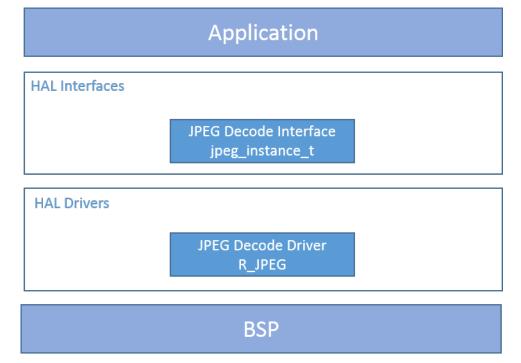

| Figure 10.7 JPEG Decode Framework                               | 42 |

| Figure 10.8 UART Framework                                      | 43 |

| Figure 10.9 Console Framework                                   | 44 |

| Figure 10.10 Thread Monitor Framework                           | 45 |

| Figure 10.11 Thread Monitor Timing Chart                        | 46 |

| Figure 10.12 Periodic Sampling ADC Framework                    | 47 |

| Figure 10.13 Audio Playback HW DAC Framework                    |    |

| Figure 10.14 Audio Playback HW I2S Framework                    | 49 |

| Figure 10.15 Audio Record HW ADC Framework                      | 50 |

| Figure 10.16 Capacitive Touch Sensing Unit Framework            | 51 |

| Figure 10.17 Capacitive Touch Sensing Unit Button Framework     | 53 |

| Figure 10.18 Capacitive Touch Sensing Unit Slider Framework     | 54 |

| Figure 10.19 Serial Peripheral Interface (SPI) Framework        | 55 |

| Figure 10.20 Synergy FileX <sup>®</sup> Interface Framework     | 57 |

| Figure 10.21 Synergy GUIX <sup>™</sup> Interface Framework      | 58 |

| Figure 10.22 Block Media Interface for SD Multi Media Card      | 61 |

| Figure 13.1 Hardware Abstraction Layer                          | 67 |

| Figure 13.2 SD Multi Media Card                                 | 68 |

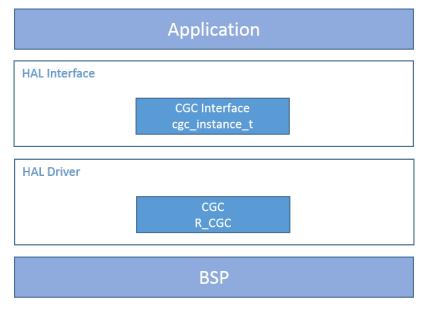

| Figure 13.3 CGC module                                          | 70 |

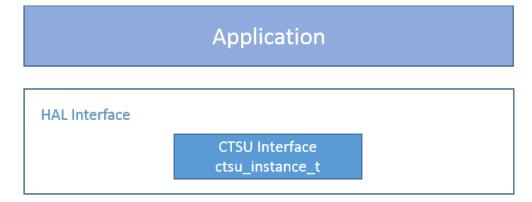

| Figure 13.4 Capacitive Touch Sensing Unit                       | 72 |

| Figure 13.5 Digital to Analog convertor                         | 73 |

| Figure 13.6 Asynchronous General Purpose Timer                  | 75 |

| Figure 13.7 Cyclic Redundancy Check calculator                  | 76 |

| Figure 13.8 Clock Frequency Accuracy Measurement                | 78 |

| Figure 13.9 RIIC                                                | 80 |

| Figure 13.10 Serial Peripheral Interface                        | 83 |

| Figure 13.11 Quad SPI                                           | 85 |

| Figure 13.12 Realtime Clock                                     | 87 |

| Figure 13.13 | Segment LCD                                    | 89    |

|--------------|------------------------------------------------|-------|

| Figure 13.14 | Serial Communication Interface UART            | 91    |

| Figure 13.15 | Serial Communication Interface SPI             | 95    |

| Figure 13.16 | JPEG Codec                                     | 97    |

| Figure 13.17 | Flash Memory-High Performance                  | 98    |

| Figure 13.18 | Event Link Controller                          | . 106 |

| Figure 13.19 | General Purpose Timer                          | . 108 |

| Figure 13.20 | GCLD Controller Data Flow                      | . 112 |

| Figure 13.21 | Watchdog Timer                                 | . 114 |

| Figure 13.22 | Analog to Digital Converter                    | . 117 |

| Figure 13.23 | Controller Area Network                        | . 122 |

| Figure 13.24 | Parallel Data Capture Unit                     | . 126 |

| Figure 14.1  | Board Support Package Flow of Events           | . 131 |

| Figure 15.1  | EEMBC CoreMark Across the Synergy Product Line | . 135 |

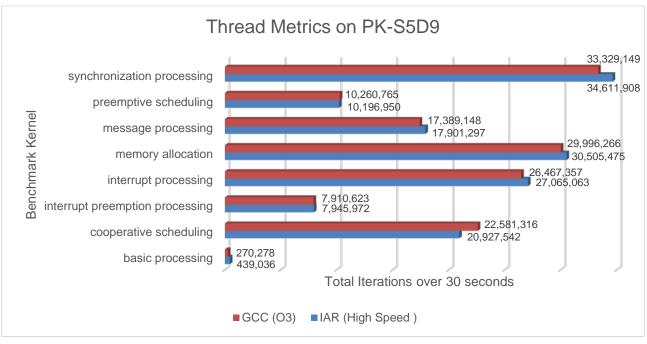

| Figure 15.2  | Thread Metric on DK-S7G2 kit                   | . 138 |

| Figure 15.3  | Thread Metric on PK-S5D9 kit                   | . 138 |

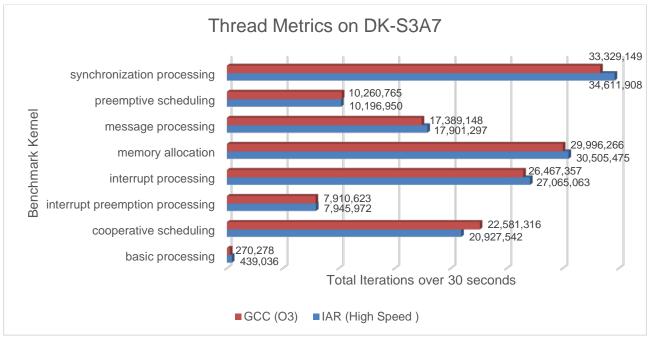

| Figure 15.4  | Thread Metric on DK-S3A7 kit                   | . 139 |

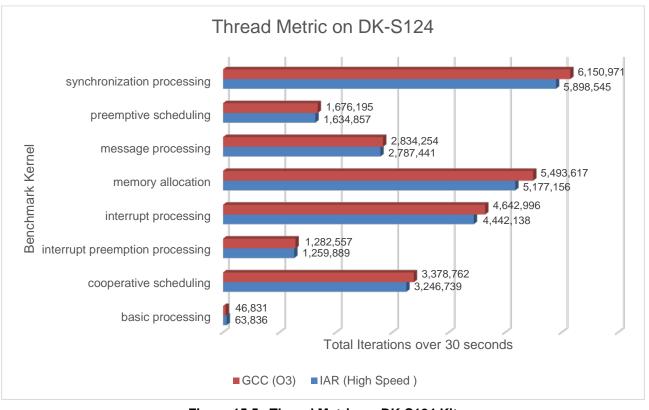

| Figure 15.5  | Thread Metric on DK-S124 Kit                   | . 139 |

| Figure 15.6  | PostMark Benchmark Characterization            | . 141 |

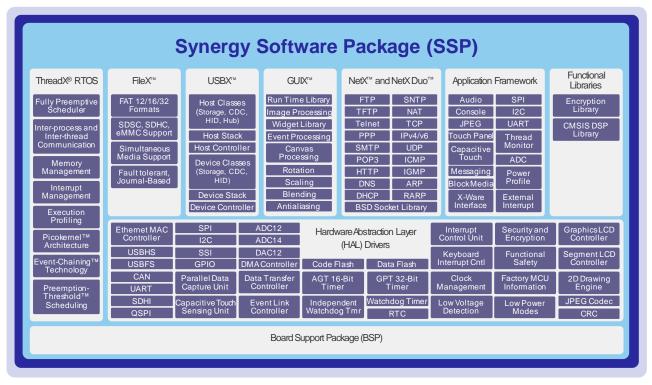

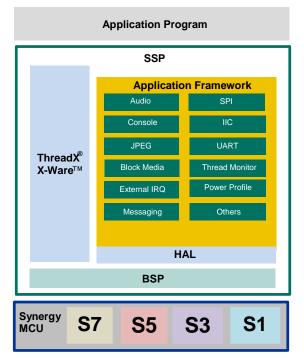

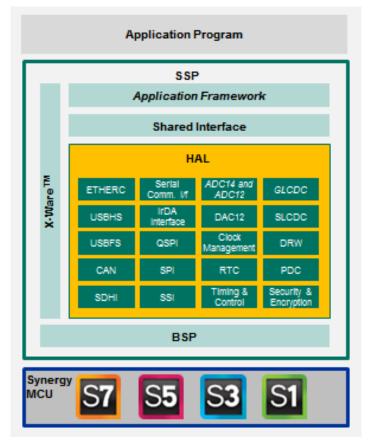

## 1. Description of Renesas Synergy<sup>™</sup> Software Package

The Synergy Software Package (SSP), the heart of the Synergy Platform, is a complete integrated software package that was created using industry best practices and tested to commercial standards.

The major components of the SSP include Express Logic's X-Ware<sup>TM</sup>. X-Ware includes the ThreadX<sup>®</sup> Real Time Operating System (RTOS) plus middleware and stacks including NetX<sup>TM</sup> IPv4 and NetX Duo<sup>TM</sup> IPv4/IPv6 compliant TCP/IP stacks respectively, USBX<sup>TM</sup> USB Host/Device protocol stack, FileX<sup>®</sup> MS-DOS compatible file system, and GUIX<sup>TM</sup> graphics runtime library.

Bundled in the Renesas SSP are additional libraries, a large set of Application Frameworks, Hardware Abstraction Layer (HAL) drivers, and Board Support Packages (BSPs) that are optimized for use with Synergy Microcontrollers (MCU). Developed according to the IEC/ISO/IEEE-12207 Software Life Cycle Process standard while using the MISRA C: 2012 coding guidelines, the complete SSP has been integrated, tested and validated. The SSP is supported and maintained by Renesas on a continuous basis, and Renesas warrants the SSP to include the features as specified in this datasheet.

Figure 1.1 Renesas Synergy™ Software Package

SSP works with Renesas  $e^2$  studio integrated development environment, featuring the GCC C/C++ Compiler Tool Chain, augmented and fortified with unique ISDE Software Configurators, and the IAR Embedded Workbench for Renesas Synergy – both are available as downloads at no additional charge from the Renesas Gallery.

## 1.1 Key Features

#### ThreadX<sup>®</sup> RTOS

- Multithreaded, deeply embedded, real-time systems

- Small, fast Picokernel<sup>TM</sup> architecture

- Multitasking capabilities

- Preemptive and cooperative scheduling

- Flexible thread priority support (32-1024 priority levels)

- Small memory footprint and fast response times

- Optimized interrupt handling

- Stack Pointer Overflow Monitor

#### **GUIX<sup>TM</sup> with 2D Drawing Engine**

- Supports 2D Graphics Acceleration in Hardware

- Unlimited objects (screens, windows, widgets)

- Dynamic object creation/deletion

- Alpha blending and anti-aliasing at higher color depths

Complete windowing support, including viewports and

- Z-order maintenance

- Multiple canvases and physical displays

- Window blending and fading

- Screen transitions, sprites, and dynamic animations

- Touchscreen and virtual keyboards

- Multilingual support with UTF8 string encoding

- Automatic size scaling

- 8-bit Color Lookup Table (CLUT) support

- Touch Rotation

- Radial Progress Bar

#### USBX<sup>TM</sup> - USB stack

- USB 2.0 Full Speed and High Speed support

- Device class: MSC, HID, CDC

- Host class: MSC, HID, CDC ACM

- Supports fast DMA transfers

#### FileX®

- MS-DOS compatible file system integrated with ThreadX

- FAT12, 16, 32-bit support

- Fault-tolerant file system (uses journaling)

- Multiple media instances

#### NetX<sup>тм</sup>

- Ethernet Driver

- IPv4 compliant TCP/IP Protocol Stack

- Integrated with ThreadX

- Zero-copy API

- UDP Fast Path Technology

- BSD-compatible socket layer

- RFC 791 Internet Protocol (IP)

- RFC 826 Address Resolution Protocol (ARP)

- RFC 903 Reverse Address Resolution Protocol (RARP)

- RFC 792 Internet Control Message Protocol (ICMP)

- RFC 3376 Internet Group Management Protocol (IGMP)

- RFC 768 User Datagram Protocol (UDP)

- RFC 793 Transmission Control Protocol (TCP)

- RFC 1112 Host Extensions for IP Multicasting

#### **Application Frameworks**

May 5, 2017

R01DS0272EU0138 Rev.1.38

• Periodic Sampling ADC framework

#### NetX Duo<sup>тм</sup>

- IPv4 and IPv6 compliant TCP/IP Protocol Stack

- Integrated with ThreadX

- Zero-copy API

- UDP Fast Path Technology

- BSD-compatible socket layer

- RFC 2460 IPv6 Specification

- RFC 4861 Neighbor Discovery for IPv6

- RFC 4862 IPv6 Stateless Address

- RFC 1981 Path MTU Discovery for IPv6

- RFC 4443 ICMPv6

- RFC 791 Internet Protocol (IP)

- RFC 826 Address Resolution Protocol (ARP)

- RFC 903 Reverse Address Resolution Protocol (RARP)

- RFC 792 Internet Control Message Protocol (ICMP)

- RFC 3376 Internet Group Management Protocol (IGMP)

- RFC 768 User Datagram Protocol (UDP)

- RFC 793 Transmission Control Protocol (TCP)

- RFC 1112 Host Extensions for IP Multicasting

#### NetX<sup>TM</sup> Applications (IPv4 Networking Services)

- DHCP Client and Server

- DNS Client

- HTTP Client and Webserver

- FTP Client and Server

- TFTP Client and Server

- Telnet Client and Server

- Auto IP

- NAT

- SMTP Client

- POP3 Client and Server

- SNTP Client

- PPP

# NetX Duo<sup>™</sup> Applications (IPv4/v6 Networking Services)

- DHCP Client and Server

- DNS Client

- HTTP Client and Webserver

- TFTP Client and Server

- Telnet Client and Server

- Auto IP

- NAT

- SMTP Client

- POP3 Client and Server

- SNTP Client

- PPP

RENESAS

#### Memory support

• Flash programming support via JTAG

Code and Data Flash drivers

External memory bus support

Human Machine Interface (HMI)

Graphics LCD controller driver

Segment LCD controller driver

Capacitive Touch Sensing Unit (CTSU)

Page 13 of 147

## Renesas Synergy<sup>™</sup> Platform

- Audio Playback framework

- Audio Record framework

- Audio Playback HW DAC framework

- Audio Playback HW I<sup>2</sup>S framework

- Audio Recording HW ADC framework

- Capacitive Touch Sensing Unit framework

- Capacitive Touch Sensing Unit Button framework

- Capacitive Touch Sensing Unit Slider framework

- Console framework

- External Interrupt framework

- I<sup>2</sup>C framework

- Inter-Thread Messaging framework

- JPEG Decode framework

- Power Mode Profile framework

- Synergy FileX<sup>®</sup> Interface framework

- Synergy GUIX<sup>TM</sup> Interface framework

- Synergy NetX Communication framework

- NetX Telnet Communications framework

- Synergy USBX Communication framework

- Thread Monitor framework

- UART framework

- SPI Framework

- Block Media Interface for SD Multi Media Card

- TES D/AVE 2D over I<sup>2</sup>C framework

- Touch Panel framework

#### Security Cryptographic Library

- True RNG (TRNG)

- SHA1, SHA224/SHA256

- AES 128, 192, and 256-bits

- 3DES, 192-bit key

- ARC4

- RSA up to 2048-bit keys

- DLP, DSA up to 2048-bit keys

#### **CMSIS DSP Library**

- Basic math functions

- Fast math functions

- Complex math functions

- Filters

- Convolution

- Matrix functions

- Transforms

- Motor control functions

- Statistical functions

- Support functions

- Interpolation functions

#### **Board Support Package (BSP)**

- Supports S124, S3A7, S5D9 and S7G2 Group MCUs

- Supports PE-HMI1, DK-S7G2, DK-S3A7, DK-S124,

- PK-S5D9, and SK-S7G2 Kits

- Creation of custom BSPs using e<sup>2</sup> studio

- System initialization and configuration during startup

- Software and hardware access control

- Register Write Protection

R01DS0272EU0138 Rev.1.38

May 5, 2017

#### Hardware Abstract Layer (HAL) Driver Modules

- Clock Generation Circuit (CGC)

- Capacitive Touch Sensing Unit (CTSU)

- Digital to Analog converter (DAC)

- Asynchronous General Purpose Timer (AGT)

- Cyclic Redundancy Check calculator (CRC)

- Clock Frequency Accuracy Measurement (CAC)

- I2IC (RIIC)

- Serial Peripheral Interface (SPI)

- Quad SPI (QSPI)

- Real Time clock (RTC)

- Segment LCD (SLCD)

- Serial Communication Interface UART (SCI\_UART)

- Serial Communication Interface I<sup>2</sup>C (SCI\_I2C)

- Serial Communication Interface SPI (SCI\_SPI)

- JPEG Codec

- Flash Memory-High Performance (FLASH\_HP)

- Flash Memory-Low Power (FLASH\_LP)

- Data Transfer Controller (DTC)

- SD Multi Media Card (SDMMC)

- Data Operation Circuit (DOC)

- Direct Memory Access Controller (DMAC)

- Interrupt Controller Unit (ICU)

- Event Link Controller (ELC)

- General Purpose Timer (GPT)

- General Purpose I/O Port (GPIO / IOPORT)

- Keyboard Interrupt Interface (KINT)

- Graphics LCD Controller (GLCD)

- Watchdog Timer (WDT)

- Independent Watchdog Timer (IWDT)

- Analog to Digital Converter (ADC) (12-bit, 14-bit)

- Factory Microcontroller Information (FMI)

- Low Power Mode (LPM)

- Controller Area Network Interface (CAN)

- Serial Sound Interface (SSI)

- Parallel Data Capture Unit (PDC)

- Low Voltage Detection (LVD)

- General PWM Timer with Input Capture (GPT\_INPUT\_CAPTURE)

#### System and Power Management

Clock Frequency Accuracy Measurement Circuit (CAC)

Page 14 of 147

- Low Power Modes driver

- Power Profiles

GPIO

RENESAS

Unique ID

RTC driver with calendar support

Data Transfer Controller (DTC) Clock Generation and Management

Stack Pointer Overflow Monitor

Messaging Configurator

**GPIO and Key Interrupts**

Key Interrupts module

GPIO module

- Event Link Controller (ELC)

- DMA Controller (DMAC)

## 1.2 Introduction to this Software Datasheet

This SSP Software Datasheet includes functional descriptions and provides performance data for the major software modules included in the Synergy Software Package (SSP).

This Software Datasheet is designed to give the Developer:

- An inventory of what components and layers are included in SSP.

- An overview of the various layers and components of SSP.

- A basic block diagram for each component (especially helpful for the Application Frameworks).

- Estimated Memory Requirements for each component.

- Tables indicating what the MCU hardware supports against what is supported (currently) in SSP for the Hardware Abstraction Layer (HAL) components.

- Performance Data and Characterizations.

Resources available in addition to this Software Datasheet are:

- SSP README.FIRST

- SSP Upgrade Guide

- SSP Software User's Manual

- SSP v1.2.0 Release Notes

- e<sup>2</sup> Studio Release Notes

- IAR Embedded Workbench for Synergy Release Notes

- Synergy Software Configurator Release Notes

- Application Projects with Application Notes.

The estimated memory requirements in this document specify the estimated memory consumption for each module. The requirements are as follows:

- Compiler: GNU ARM<sup>®</sup> compiler eabi-4\_9-2015q3-20150921-win32 (Option: -O2)

- Compiler: IAR Compiler version 7.71.1 Embedded Workbench for Renesas Synergy (Option: -Oh)

The memory usage for the modules includes:

• Flash Memory Usage = .text + .data

All performance tests in this document are included in Section 0, and were conducted and measured on specific Synergy hardware systems, typically a Synergy Development Kit. This section also specifies the test environment for each performance test that includes:

- SSP version

- Synergy hardware (Development Kit)

- When the Synergy hardware is specific, it also identifies which Synergy MCU is used, the operating frequency, and the MCU configuration settings

- Toolchain version (including complier optimization levels).

#### 1.2.1 Memory Size Estimation

Estimating memory size requirements for a design can be difficult. Design, coding, compiler options, and even errorchecking can affect the resultant binary's sizes as well as their runtime memory requirements. In the following sections various configurations and options are shown to give the Developer useful information so that they can judge how much Flash memory is required given the inclusion of certain features.

For ThreadX and the X-ware components, the ability to turn compiler-time error checking on, or off, affects memory sizes, so Renesas will show both conditions. Using ThreadX as an example, if error checking is turned off, the resultant Flash sizes are (for "event"):

| Name  | Flash |

|-------|-------|

| Event | 1156  |

If error checking is turned on, the following amounts need to be **added** to the Flash size (in bytes):

| Name  | Flash |

|-------|-------|

| Event | 360   |

Thus, the total bytes needed for Flash for this ThreadX function is 1516, if every function on the "event" directory is being used.

It would be nearly impossible from a datasheet perspective to turn on, or off, error checking for every single function, even if that is an option Developers have to fine-tune their own code. Therefore, memory size values shown are generally worst case in that they are the sum of all of the files under each directory. Please note that by default, error checking is turned on.

Also note that different compiler tool chains produce different memory sizes, and compiling for an ARM Cortex M4 architecture is different from compiling for an ARM Cortex M0+.

ARM Cortex M4 means MCU devices from S3A7, S5D9, and S7G2 Synergy MCU Groups.

ARM Cortex M0+ means devices from S124 Synergy MCU Group.

The process Renesas uses to calculate Flash memory size is as follows:

Compile source code to create the object file.

Generate the memory footprint using the following command:

arm-none-eabi-size --format=Berkeley <filename>.o

#### 1.2.2 Software Quality Assurance and Test Data

Renesas provides significant and detailed software quality assurance and test data on SSP and its components, modules, and libraries.

For an overview, please see: https://www.renesas.com/en-us/products/synergy/software/quality.html

The latest Synergy Software Quality Handbook and the latest Software Quality Summary can also be found on that page.

## 2. ThreadX<sup>®</sup> RTOS

## 2.1 Introduction to ThreadX and X-ware

ThreadX and X-ware (NetX/NetX Duo, USBX, FileX<sup>®</sup>, GUIX<sup>TM</sup>, and the Windows PC side tools TraceX<sup>®</sup> and GUIX<sup>TM</sup> Studio) are integrated into SSP.

| THREA               | DX API             | Component                   | Express<br>Logic<br>Version |

|---------------------|--------------------|-----------------------------|-----------------------------|

| THREAD SERVICES     | MESSAGE QUEUES     | ThreadX <sup>®</sup>        | 5.7                         |

| HILLER SERVICES     | MECONAL GOLOLO     | NetX <sup>™</sup>           | 5.9                         |

|                     |                    | NetX Duo™                   | 5.10 SP1                    |

| COUNTING SEMAPHORES | MUTEXES            | NetX Application bundle     | 5.9 SP2                     |

|                     |                    | NetX Duo Application bundle | 5.10 SP1                    |

| EVENT FLAGS         | BLOCK MEMORY POOLS | USBX <sup>™</sup> Host      | 5.7 SP7                     |

|                     |                    | USBX <sup>™</sup> Device    | 5.7 SP4                     |

| BYTE MEMORY POOLS   | APPLICATION TIMERS | FileX®                      | 5.4 SP2                     |

| BITE MEMORIT POOLS  | AFFEICATION TIMETS | GUIX™                       | 5.3.2                       |

|                     |                    | TraceX®                     | 5.2.0                       |

| THREADX COR         | E SCHEDULER        | GUIX™ Studio                | 5.3.2.2                     |

#### Figure 2.1 ThreadX<sup>®</sup> Features and Versions

## 2.2 Component Introduction

At the core of Synergy Software Package (SSP) is the Express Logic, Inc. ThreadX<sup>®</sup> RTOS. Optimized for MCUs in the Synergy Microcontroller family and tightly integrated with the SSP, ThreadX<sup>®</sup> includes an optimized, high-performance real-time kernel designed specifically for real-time embedded systems running on microcontrollers. ThreadX<sup>®</sup> provides a fast, sub-microsecond context switching time and a small footprint (as small as 2-KB Flash memory).

The key features of ThreadX<sup>®</sup> include:

- Picokernel<sup>TM</sup> design where services are not layered

- Preemptive and preemption-threshold scheduling

- Event-chaining

- Inter-task synchronization

- Highly optimized interrupt processing where only scratch registers are saved/restored upon ISR entry/exit, unless preemption is necessary

- Fast interrupt response time

- Fast context switching

- Low RTOS service overhead

- Stack pointer overflow monitor.

ThreadX<sup>®</sup> memory protection ensures that application threads and the ThreadX<sup>®</sup> kernel are protected against accidental read or write access from other threads. This prevents code or data corruption from latent application bugs, and eliminates one of the most common causes of application crashes.

#### 2.2.1 ThreadX Certifications

ThreadX<sup>®</sup> has been pre-certified by TUV and UL to IEC 61508 SIL 4, IEC 62304 Class C, ISO 26262 ASIL D, UL/IEC 60730, UL/IEC 60335, UL 1998, and SW-SIL EN 50128.

## 2.2.2 ThreadX<sup>®</sup> API

With an intuitive and consistent API naming convention (noun-verb naming, all API's have a leading "tx\_" to easily identify the call as a ThreadX call), the ThreadX API provide the foundation on which multi-threaded, real-time Internet of Things (IoT) applications can be built.

Blocking API's have an optional thread timeout feature to defeat dead-hangs, and many API's are directly available from application interrupt service routines (ISRs).

#### 2.2.3 Thread Services

With dynamic thread creation, Thread Services allows for an unlimited number of threads (based on available hardware resources and real-time demands)

#### 2.2.4 Message Queues

Like Thread Services, Messages queues allow for dynamic queue creation and there are no limits on the number of queues (based on available hardware resources and real-time demands). Messages can be copied by value or by reference via pointer. Message sizes are from 1 to 16, 32-bit words. Optional thread suspension on empty and full, and optional timeout on all suspensions, helps to avoid lock-ups.

#### 2.2.5 Counting Semaphores

With dynamic semaphore creation and no limits on the number of semaphores, these 32-bit semaphores provide interthread coordination services. Both consumer-producer and resource-protection models are included. Optional thread suspension when the semaphore is unavailable and optional timeout on suspension increase robustness.

#### 2.2.6 Mutexes

Another form of inter-thread communication synchronization, there are no limits to the number of mutexes you can have (based on available hardware resources) and allowing for dynamic mutex creation, this system supports nested resource protection. Optional priority inheritance is supported, and Optional thread suspension when the mutex is unavailable are supported as well.

#### 2.2.7 Event Flags

As with other ThreadX<sup>®</sup> resources, dynamic event flag group creation and no limits on event flag groups (as always, based on available hardware resources), event flags allow synchronization of one thread or multiple threads. Atomic "get" and "clear" is supported, as is optional multi-thread suspension on AND/OR set of events and optional timeout on all suspension.

#### 2.2.8 Block Memory Pools

Dynamic block pool creation, and no limits on the number of block pools (except for physical memory limits), there are no limits on the size of fixed-size blocks or the size of the pool. The fastest possible memory allocation/deallocation is supported, and features like optional thread suspension on empty pool and optional timeout on all suspension are available.

#### 2.2.9 Byte Memory Pools

Dynamic byte pool creation, and no limits on the number of byte pools (except for physical memory limits), there are no limits on the number of byte pools managed. This is the most flexible variable-length memory allocation/deallocation, and allocation size locality is supported. Includes optional thread suspension on empty pool and optional timeout on all suspension are available.

#### 2.2.10 Application Timers

ThreadX<sup>®</sup> offers Dynamic timer creation, no limits on the number of timers, and periodic or one-shot timers are supported. Periodic timers may have different initial expiration value, and there is no searching on timer activation or deactivation.

#### 2.2.11 ThreadX Core Scheduler

ThreadX<sup>®</sup> offers as low as a minimal 2KB flash footprint, 1KB RAM footprint capability, but the most important feature of the Scheduler is very fast, sub-microsecond context switch times. Fully deterministic regardless of the number of threads, this priority-based, fully pre-emptive Scheduler has 32 default priority levels (optionally up to 1024). In addition to pre-emptive scheduling, it can also perform cooperative scheduling within a priority level (FIFO). Preemption-threshold technology prevents thread inversion. Optional time services include:

- Per-thread optional time-slice

- Optional time-out on all blocking APIs Requires on hardware time interrupt.

Execution profiling to help tune your application is offered, as well as system-wide trace.

## 2.3 Estimated Memory Requirements

| ThreadX <sup>®</sup><br>ARM Cortex<br>GCC | M4 with        | ThreadX <sup>®</sup><br>ARM Cortex<br>IAR | M4 with          | ThreadX <sup>®</sup><br>ARM Cortex<br>GCC          | M0+ with        | ThreadX <sup>®</sup><br>ARM Cortex M0+ with<br>IAR |       |  |

|-------------------------------------------|----------------|-------------------------------------------|------------------|----------------------------------------------------|-----------------|----------------------------------------------------|-------|--|

| Name                                      | Flash          | Name                                      | Flash            | Name                                               | Flash           | Name                                               | Flash |  |

| block                                     | 964            | block                                     | 864              | block                                              | 976             | block                                              | 912   |  |

| byte                                      | 1,344          | byte                                      | 1,276            | byte                                               | 1,392           | byte                                               | 1,324 |  |

| event                                     | 1,156          | event                                     | 1,056            | event                                              | 1,232           | event                                              | 1,114 |  |

| initialize                                | 364            | initialize                                | 252              | initialize                                         | 360             | initialize                                         | 340   |  |

| isr                                       | 8              | isr                                       | 4                | isr                                                | 8               | isr                                                | 4     |  |

| mutex                                     | 1,672          | mutex                                     | 1,516            | mutex                                              | 1,680           | mutex                                              | 1,576 |  |

| queue                                     | 1,784          | queue                                     | 1,708            | queue                                              | 1,872           | queue                                              | 1,796 |  |

| semaphore                                 | 904            | semaphore                                 | 868              | semaphore                                          | 928             | semaphore                                          | 918   |  |

| thread                                    | 3,257          | thread                                    | 3,040            | thread                                             | 3,253           | thread                                             | 3,084 |  |

| time                                      | 40             | time                                      | 40               | time                                               | 40              | time                                               | 40    |  |

| timer                                     | 1,328          | timer                                     | 1,130            | timer                                              | 1,372           | timer                                              | 1,164 |  |

| trace                                     | 104            | trace                                     | 104              | trace                                              | 120             | trace                                              | 120   |  |

| In addition, if                           | error checking | is turned on, a                           | add the followir | ig values to the                                   | e previous data | :                                                  |       |  |

| ThreadX <sup>®</sup><br>ARM Cortex<br>GCC | M4 with        | ThreadX <sup>®</sup><br>ARM Cortex<br>IAR | M4 with          | ThreadX <sup>®</sup><br>ARM Cortex M0+ with<br>GCC |                 | ThreadX <sup>®</sup><br>ARM Cortex M0+ with<br>IAR |       |  |

| Name                                      | Flash          | Name                                      | Flash            | Name                                               | Flash           | Name                                               | Flash |  |

| block                                     | 404            | block                                     | 396              | block                                              | 448             | block                                              | 404   |  |

| byte                                      | 444            | byte                                      | 440              | byte                                               | 488             | byte                                               | 452   |  |

| event                                     | 360            | event                                     | 360              | event                                              | 408             | event                                              | 376   |  |

| mutex                                     | 420            | mutex                                     | 408              | mutex                                              | 460             | mutex                                              | 432   |  |

| queue                                     | 548            | queue                                     | 540              | queue                                              | 596             | queue                                              | 544   |  |

| semaphore                                 | 396            | semaphore                                 | 376              | semaphore                                          | 452             | semaphore                                          | 408   |  |

| thread                                    | 824            | thread                                    | 800              | thread                                             | 912             | thread                                             | 824   |  |

| timer                                     | 408            | timer                                     | 384              | timer                                              | 432             | timer                                              | 396   |  |

## 3. NetX<sup>™</sup> Embedded TCP/IP and UDP Stacks

## 3.1 Component Introduction

SSP includes an optimized embedded TCP/IP-IPv4-compliant protocol stack, NetX<sup>TM</sup>, for enabling Internet of Things (IoT) and Machine to Machine (M2M) communication protocols and embedded applications that require network connectivity. NetX<sup>TM</sup> is completely integrated with ThreadX<sup>®</sup> and is based on Express Logic's unique Piconet<sup>TM</sup> architecture that provides a zero-copy API interface for applications. Key features and capabilities provided with NetX<sup>TM</sup> include:

- Fast execution

- TraceX<sup>®</sup> system analysis support

- BSD sockets compatible API

- UDP Fast-Path lets basic UDP packets pass through NetX <sup>TM</sup> without copying or context switches

- Flexible packet management.

NetX<sup>TM</sup> provides a complete set of protocol components that comprise the TCP/IP standard:

- RFC 791 Internet Protocol (IP)

- RFC 826 Address Resolution Protocol (ARP)

- RFC 903 Reverse Address Resolution Protocol (RARP)

- RFC 792 Internet Control Message Protocol (ICMP)

- RFC 3376 Internet Group Management Protocol (IGMP)

- RFC 768 User Datagram Protocol (UDP)

- RFC 793 Transmission Control Protocol (TCP)

- RFC 1112 Host Extensions for IP Multicasting.

In SSP v1.2.0, both  $e^2$  studio and IAR Embedded Workbench for Synergy have Configurators to assist Developers in creating code for NetX<sup>TM</sup>.

|                 | NetX Pro                     | otocol (nx_xxx)               |                                                            |

|-----------------|------------------------------|-------------------------------|------------------------------------------------------------|

|                 | NetX IP Instance             |                               | NetX <protocol> Common<br/>(for some protocols)</protocol> |

| NetX Common(nx) | NetX Packet Pool<br>Instance | NetX Port ETHER<br>(sf_el_nx) |                                                            |

Figure 3.1 NetX<sup>™</sup> Stack Configuration

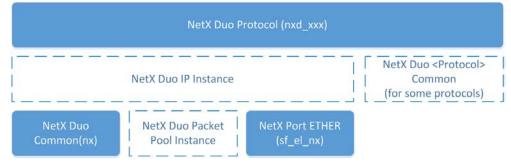

## 4. NetX Duo<sup>™</sup> Dual IPv4/IPv6 Stack

## 4.1 Component Introduction

For applications requiring IPv6 support, SSP includes Express Logic's NetX Duo<sup>TM</sup>, a dual IPv4 and IPv6 compliant TCP/IP protocol stack. NetX Duo<sup>TM</sup> is completely integrated with ThreadX<sup>®</sup> RTOS and includes all features and capabilities available with NetX<sup>TM</sup>, which further extends the capabilities of SSP-based devices to auto-configure their interface addresses through the Stateless Address Auto configuration protocol. Devices can also use layered structures to enable devices to process IPv6 headers more efficiently. NetX Duo<sup>TM</sup> applications are individually selectable for each project providing flexibility to the system designer to incorporate only the applications necessary for the target application.

Figure 4.1 NetX Duo<sup>™</sup> Stack Configuration

NetX Duo<sup>TM</sup> implements the following protocols:

- All IPv4 protocols available in NetX<sup>TM</sup>

- Zero-copy API

- UDP Fast Path Technology

- BSD-compatible socket layer

- RFC 2460 IPv6 Specification

- RFC 4861 Neighbor Discovery for IPv6

- RFC 4862 IPv6 Stateless Address Auto configuration

- RFC 1981 Path MTU Discovery for IPv6

- RFC 4443 ICMPv6

- RFC 791 Internet Protocol (IP)

- RFC 826 Address Resolution Protocol (ARP)

- RFC 903 Reverse Address Resolution Protocol (RARP)

- RFC 792 Internet Control Message Protocol (ICMP)

- RFC 3376 Internet Group Management Protocol (IGMP)

- RFC 768 User Datagram Protocol (UDP)

- RFC 793 Transmission Control Protocol (TCP)

- RFC 1112 Host Extensions for IP Multicasting

NetX Duo<sup>TM</sup> has been accredited by the IPv6 forum with Phase-II IPv6-Ready Logo certification. NetX Duo<sup>TM</sup> has been pre-certified by TUV and UL to IEC 61508 SIL 4, IEC 62304 Class C, ISO 26262 ASIL D, UL/IEC 60730, UL/IEC 60335, UL 1998, and EN 50128 SW-SIL 4.

## 4.2 Estimated Memory Requirements

| NetX Duo™<br>ARM Cortex M4 w                                                        | vith GCC             | NetX Duo™<br>ARM Cortex M0+ with IAR                |        |  |  |  |

|-------------------------------------------------------------------------------------|----------------------|-----------------------------------------------------|--------|--|--|--|

| Name                                                                                | Flash                | Name                                                | Flash  |  |  |  |

| arp                                                                                 | 3,884                | arp                                                 | 3,498  |  |  |  |

| icmp                                                                                | 1,704                | icmp                                                | 1,590  |  |  |  |

| icmpv4                                                                              | 868                  | icmpv4                                              | 794    |  |  |  |

| icmpv6                                                                              | 5,484                | icmpv6                                              | 5,184  |  |  |  |

| igmp                                                                                | 1,696                | igmp                                                | 1,700  |  |  |  |

| invalidate                                                                          | 100                  | invalidate                                          | 96     |  |  |  |

| ip                                                                                  | 11,297               | ір                                                  | 9,854  |  |  |  |

| ipv4                                                                                | 1,016                | ipv4                                                | 820    |  |  |  |

| ipv6                                                                                | 7,612                | ipv6                                                | 6,708  |  |  |  |

| nd                                                                                  | 4,128                | nd                                                  | 3,696  |  |  |  |

| packet                                                                              | 1,704                | packet                                              | 1,658  |  |  |  |

| ram                                                                                 | 1,168                | ram                                                 | 1,180  |  |  |  |

| rarp                                                                                | 768                  | rarp                                                | 706    |  |  |  |

| system                                                                              | 278                  | system                                              | 236    |  |  |  |

| tcp                                                                                 | 14,744               | tcp                                                 | 13,294 |  |  |  |

| udp                                                                                 | 3,572                | udp                                                 | 3,292  |  |  |  |

| In addition, if error<br>previous data:<br>NetX Duo <sup>™</sup><br>ARM Cortex M4 w | checking is turned o | n, add the following<br>NetX Duo™<br>ARM Cortex M0+ |        |  |  |  |

| Name                                                                                | Flash                | Name                                                | Flash  |  |  |  |

| icmp                                                                                | 328                  | icmp                                                | 324    |  |  |  |

| icmpv6                                                                              | 68                   | icmpv6                                              | 68     |  |  |  |

| ір                                                                                  | 404                  | ір                                                  | 382    |  |  |  |

| ipv6                                                                                | 832                  | ipv6                                                | 812    |  |  |  |

| nd                                                                                  | 388                  | nd                                                  | 368    |  |  |  |

| tcp                                                                                 | 220                  | tcp                                                 | 216    |  |  |  |

| udp                                                                                 | 608                  | udp                                                 | 580    |  |  |  |

In SSP v1.2.0, both  $e^2$  studio and IAR Embedded Workbench for Synergy have Configurators to assist Developers in creating code for NetX Duo<sup>TM</sup>.

## 5. NetX<sup>™</sup> Applications Bundle

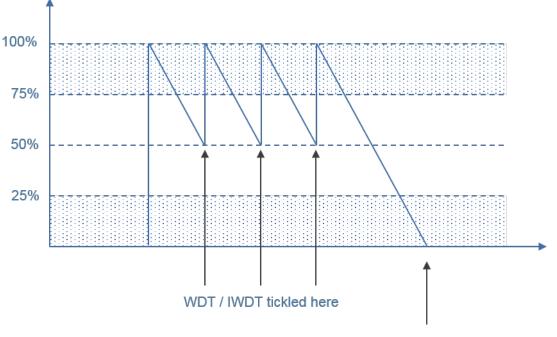

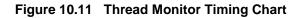

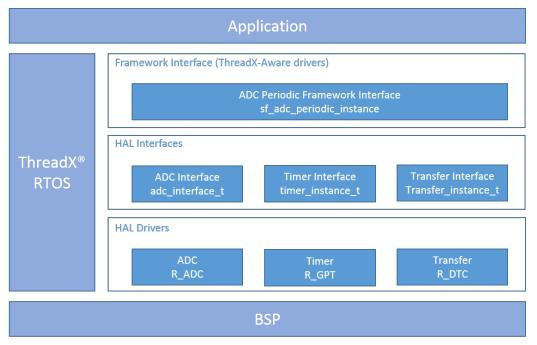

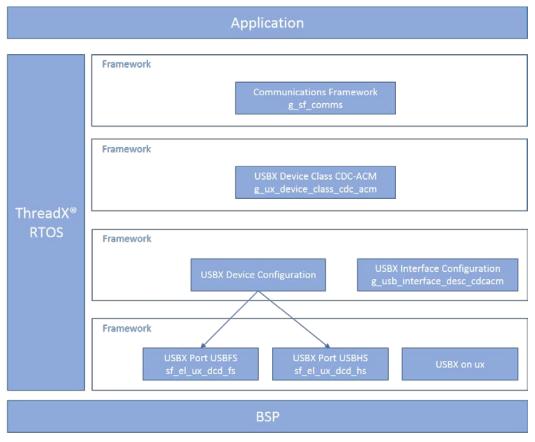

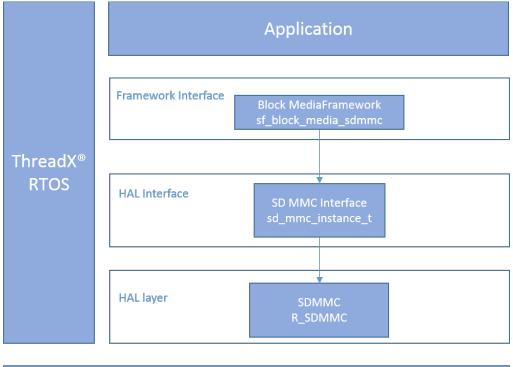

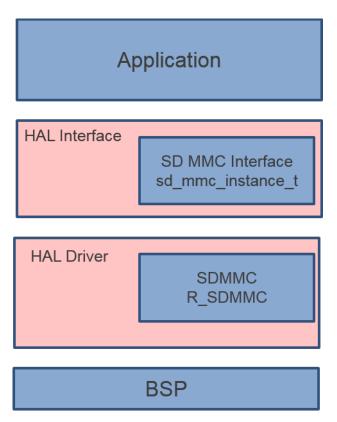

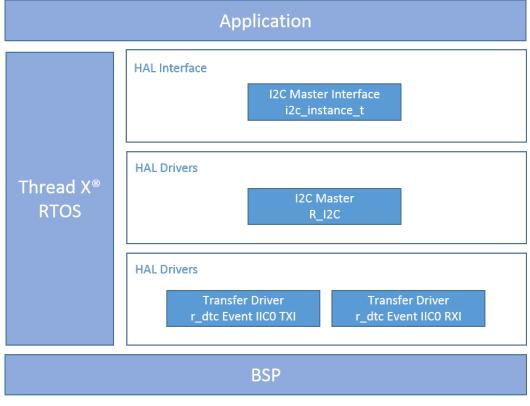

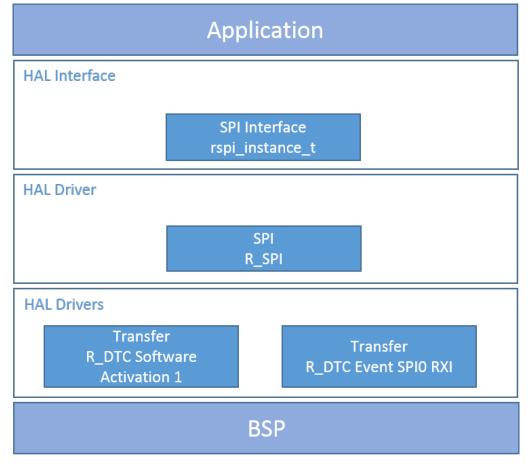

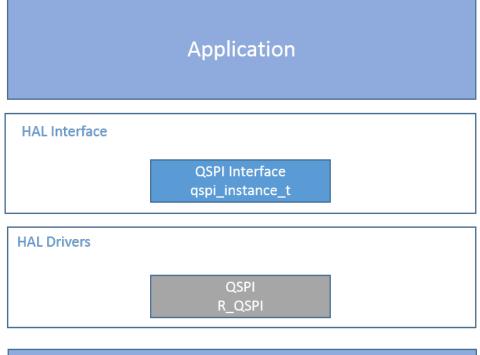

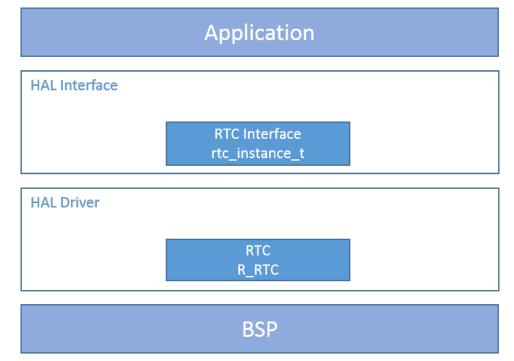

## 5.1 Component Introduction