# Digital Equipment Corporation Maynard, Massachusetts

LPS11 laboratory peripheral system user's guide

DEC-11-HLPGA-C-D

LPS11 laboratory peripheral system user's guide

digital equipment corporation · maynard. massachusetts

1st Edition, March 1973 2nd Printing, September 1973 3rd Printing (Rev), January 1974 4th Printing, November 1974

#### Copyright © 1974 by Digital Equipment Corporation

The material in this manual is for informational purposes and is subject to change without notice.

Printed in U.S.A.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

| DEC       | PD |

|-----------|----|

| FLIP CHIP | FO |

| DIGITAL   | CO |

| UNIBUS    |    |

|           |    |

PDP FOCAL COMPUTER LAB

# CONTENTS

|                  | Page                                           |

|------------------|------------------------------------------------|

| CHAPTER 1        | I DO11 OVOTEM                                  |

| CHAFTER I        | LPS11 SYSTEM                                   |

| 1.1              | INTRODUCTION                                   |

| 1.2              | SCOPE OF MANUAL                                |

| 1.3              | GENERAL DESCRIPTION                            |

| 1.4              | DETAILED DESCRIPTION                           |

| 1.4.1            | Standard LPS11-S                               |

| 1.4.1.1          | Bus Control                                    |

| 1.4.1.2          | Power Supply                                   |

| 1.4.1.3          | Front Panel                                    |

| 1.4.1.4          |                                                |

| 1.4.1.4          | Back Panel                                     |

| <b>CHAPTER 2</b> | ANALOG-TO-DIGITAL CONVERTER SUBSYSTEM          |

|                  |                                                |

| 2.1              | GENERAL DESCRIPTION                            |

| 2.1.1            | Block Diagram                                  |

| 2.2              | DETAILED DESCRIPTION                           |

| 2.2.1            | LPSAD-12                                       |

| 2.2.2            | LPSAM                                          |

| 2.2.3            | LPSAG/LPSAG-VG 2-2                             |

| 2.2.4            | LPSSH                                          |

| 2.2.5            | LPSAD-NP                                       |

| 2.3              | USER INTERFACING                               |

| 2.3.1            | A407 Eight-Channel A/D Multiplexer             |

| 2.3.2            | A/D Preamplifiers 2-7                          |

| 2.4              | PROGRAMMING 2-9                                |

| 2.4.1            | A/D Status Register                            |

| 2.4.2            | A/D Buffer                                     |

| 2.4.3            | Dual Mode Operation                            |

| 2.4.4            | DMA Operation                                  |

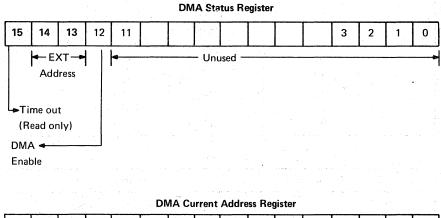

| 2.4.4.1          | DMA Status Register                            |

| 2.4.4.2          |                                                |

| 2.4.4.3          | DMA Word Count Register                        |

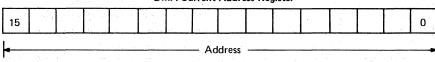

| 2.4.4.4          | DMA Current Address Register                   |

| 2.4.4            | Programming Sequence to Operate the DMA Option |

|                  | Programming Examples                           |

| 2.4.5.1          | Programming Example 1                          |

| 2.4.5.2          | Programming Example 2                          |

| 2.4.5.3          | Programming Example 3                          |

| 2.4.5.4          | Programming Example 4                          |

| 2.5              | LPSAM-SG AND BA408 SWITCHED GAIN OPTIONS       |

| 2.5.1            | Description                                    |

| 2.5.2            | Performance Specifications                     |

| 2.5.3            | Packaging                                      |

| 2.5.4            | Programming                                    |

| 2.5.5            | Switched Gain with LPSSH 2-21                  |

| 2.5.6            | Switched Gain with Pre-Amps                    |

| 2.5.6.1          | Input Ranges                                   |

| 2.5.6.2          | Resolution                                     |

| 2.5.6.3          | Zero Drift with Pre-Amps 2-22                  |

| 2.5.6.4          | Noise Levels with Pre-Amps 2-22                |

# **CONTENTS** (Cont)

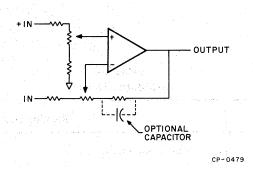

| 2.5.7   | Filtering the Switched Gain Input                     | 2-23 |

|---------|-------------------------------------------------------|------|

| 2.5.7.1 | Reasons for Input Filtering                           |      |

| 2.5.7.2 | Filtering Capability of the Switched Gain Multiplexer |      |

| 2.5.7.3 | Zero Shift Due to Filter                              | 2-24 |

| 2.5.7.4 | Throughput Limitations Due to Filter                  | 2-24 |

| CHAPTER 3 | LPSKW PROGRAMMABL | <b>E REA</b> | L-TIME | CLOCK |

|-----------|-------------------|--------------|--------|-------|

| UNALIENS  |                   |              |        |       |

| 3.1     | GENERAL DESCRIPTION 3-1                              |

|---------|------------------------------------------------------|

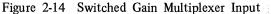

| 3.2     | BLOCK DIAGRAM DESCRIPTION 3-1                        |

| 3.2.1   | Status Register                                      |

| 3.2.2   | Mode Control                                         |

| 3.2.2.1 | Single Interval Mode                                 |

| 3.2.2.2 | Repeated Interval Mode 3-2                           |

| 3.2.2.3 | External Events Timing Mode                          |

| 3.2.2.4 | Event Timing from Zero Base Mode                     |

| 3.2.3   | Rate Control and Clock 3-3                           |

| 3.2.4   | Buffer/Preset and Counter Registers 3-3              |

| 3.2.5   | Interrupt Control                                    |

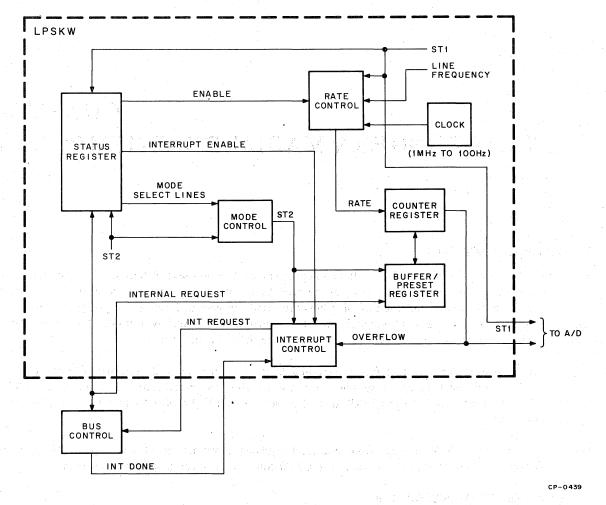

| 3.2.6   | Schmitt Triggers                                     |

| 3.3     | USER INTERFACING                                     |

| 3.4     | PROGRAMMING 3-7                                      |

| 3.4.1   | Status Register                                      |

| 3.4.2   | Buffer/Preset and Counter Registers 3-9              |

| 3.4.3   | Register Addressing, Vector Addressing, and Priority |

| 3.4.4   | Program Examples                                     |

| 3.4.4.1 | Program Example 1 3-9                                |

| 3.4.4.2 | Program Example 2                                    |

|         |                                                      |

÷

. . 5-6

. .

| CHAPTER 4 | LPSDR-A DIGITAL I/O AND RELAY |

|-----------|-------------------------------|

| 4.1       | GENERAL DESCRIPTION           |

Drive . . .

5.3.3

| 4.1                                              | GENERAL DESCRIPTION 4-1                                                                                                                                                                                                           |

|--------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

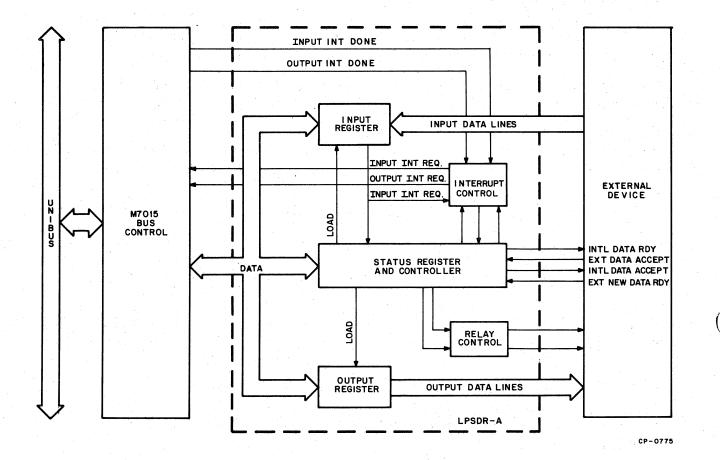

| 4.2                                              | BLOCK DIAGRAM DESCRIPTION 4-1                                                                                                                                                                                                     |

| 4.2.1                                            | Output Register                                                                                                                                                                                                                   |

| 4.2.2                                            | Input Register                                                                                                                                                                                                                    |

| 4.2.3                                            | Interrupt Control                                                                                                                                                                                                                 |

| 4.2.4                                            | Relays 4-6                                                                                                                                                                                                                        |

| 4.3                                              | USER INTERFACING                                                                                                                                                                                                                  |

| 4.4                                              | <b>PROGRAMMING</b>                                                                                                                                                                                                                |

| 4.4.1                                            | Status Register                                                                                                                                                                                                                   |

| 4.4.2                                            | Data Registers                                                                                                                                                                                                                    |

|                                                  |                                                                                                                                                                                                                                   |

| 4.4.3                                            | Programming Examples                                                                                                                                                                                                              |

| 4.4.3<br>CHAPTER 5                               |                                                                                                                                                                                                                                   |

|                                                  | Programming Examples                                                                                                                                                                                                              |

| CHAPTER 5                                        | Programming Examples    4-13      DISPLAY CONTROL    GENERAL DESCRIPTION                                                                                                                                                          |

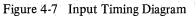

| <b>CHAPTER 5</b> 5.1                             | Programming Examples       4-13         DISPLAY CONTROL       5-1         GENERAL DESCRIPTION       5-1         BLOCK DIAGRAM DESCRIPTION       5-1                                                                               |

| <b>CHAPTER 5</b><br>5.1<br>5.2                   | Programming Examples       4-13         DISPLAY CONTROL       5-1         GENERAL DESCRIPTION       5-1         BLOCK DIAGRAM DESCRIPTION       5-1         Status Register       5-1                                             |

| <b>CHAPTER 5</b><br>5.1<br>5.2<br>5.2.1          | Programming Examples       4-13         DISPLAY CONTROL       5-1         GENERAL DESCRIPTION       5-1         BLOCK DIAGRAM DESCRIPTION       5-1         Status Register       5-1                                             |

| <b>CHAPTER 5</b><br>5.1<br>5.2<br>5.2.1<br>5.2.2 | Programming Examples       4-13         DISPLAY CONTROL       5-1         GENERAL DESCRIPTION       5-1         BLOCK DIAGRAM DESCRIPTION       5-1         Status Register       5-1         Digital-to-Analog Control       5-2 |

# **CONTENTS** (Cont)

|         |                      |     |     |     |       |       |      |     |       |             |      |     |     |      | Page |

|---------|----------------------|-----|-----|-----|-------|-------|------|-----|-------|-------------|------|-----|-----|------|------|

| 5.3.4   | Ground Logic         |     |     | • • |       | ••••  |      | ÷   |       | · · · · · · |      | ••• | • • | • •  | 5-7  |

| 5.4     | PROGRAMMING          |     | • • | •   |       | · .·. |      | ••• | • • • |             | ÷.   |     | ••• |      | 5-7  |

| 5.4.1   | X and Y Registers .  |     |     |     |       |       | •••• | ••• | • • • |             | •••  |     | ••• | • •  | 5-7  |

| 5.4.2   | Status Register      |     | • • |     |       | • • • |      | ••• |       | ••••        | • •  | • • |     |      | 5-7  |

| 5.4.3   | Programming Examples |     |     |     |       |       |      |     |       |             |      |     |     |      |      |

| 5.4.3.1 | Program Example      | 1 . |     |     |       | • • • | •••• | ••• | ••••  | ••••        | 2    | • • | • • | •••• | 5-9  |

| 5.4.3.2 | Program Example      |     |     |     |       |       |      |     |       |             |      |     |     |      |      |

| 5.4.3.3 | Program Example      | 3 . |     |     | • • • | • • • |      | ••• |       | • • •       | •••• |     | • • | • •  | 5-11 |

|         |                      |     |     |     |       |       |      |     |       |             |      |     |     |      |      |

|         |                      |     |     |     |       | 40 g  |      |     |       |             |      |     |     |      |      |

| APPENDIX A | FLOATING | i VECTORS | FOR THE | PDP-11 |

|------------|----------|-----------|---------|--------|

|            |          |           |         |        |

|            |          |           |         |        |

APPENDIX B PROGRAMMER'S REFERENCE

### ILLUSTRATIONS

Page

## Figure No.

4-6

| and the second |                                                                     |

|------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|

| 1-1                                                                                                              | LPS11-S Bus Control Block Diagram 1-3                               |

| 1-2                                                                                                              | Address Register                                                    |

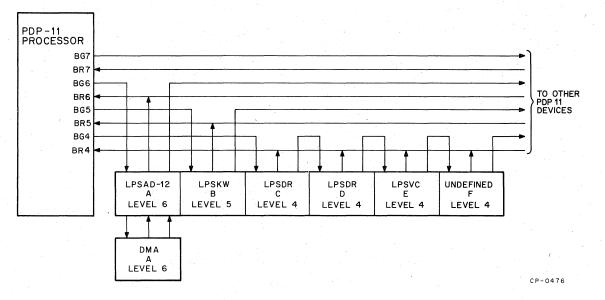

| 1-3                                                                                                              | Priority Chaining of LPS11 System 1-4                               |

| 1-4                                                                                                              | LPS11-S Front Panel                                                 |

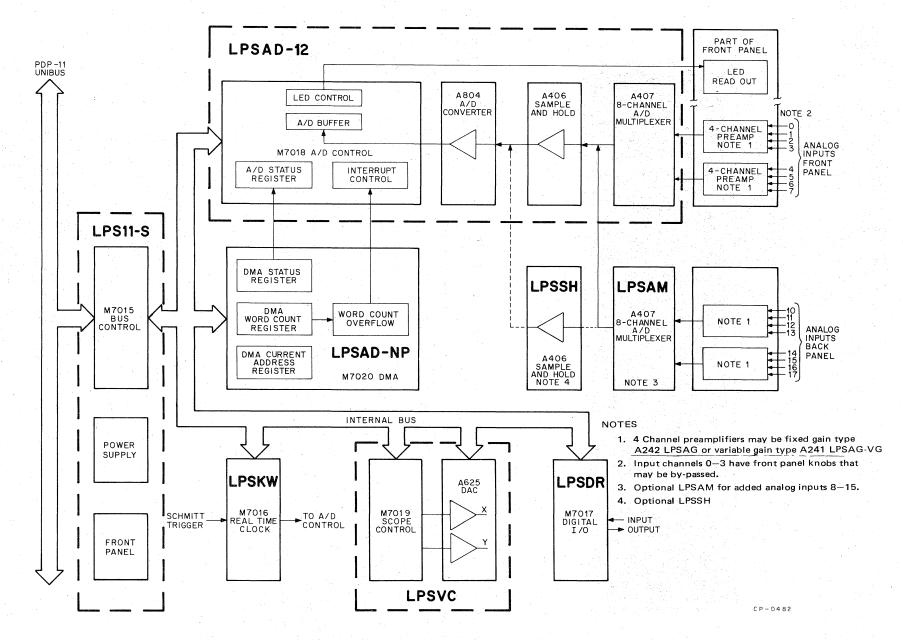

| 1-5                                                                                                              | LPS11-S Laboratory Peripheral System and Options, Block Diagram 1-6 |

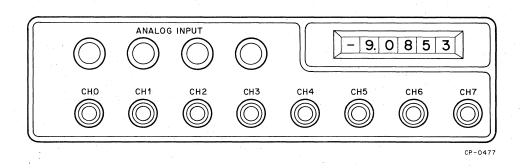

| 2-1                                                                                                              | Analog Section of Front Panel 2-3                                   |

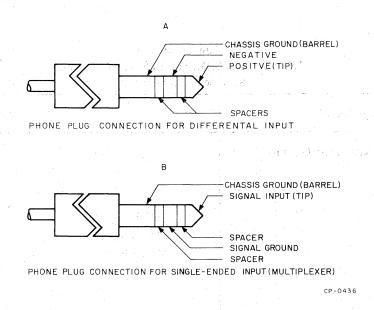

| 2-2                                                                                                              | Correct Phone Plug Connections for Handling External Signals        |

| 2-3                                                                                                              | Recommended Input Wiring 2-6                                        |

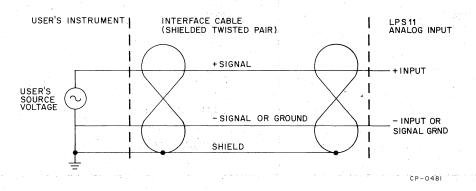

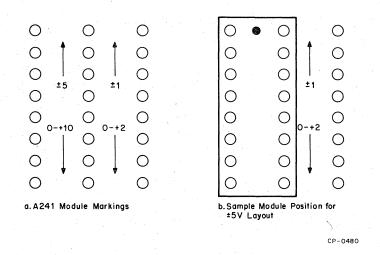

| 2-4                                                                                                              | LPSAG-VG Channel Range Selection via Jumper 2-8                     |

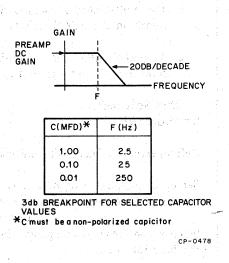

| 2-5                                                                                                              | Low Pass Filtering                                                  |

| 2-6                                                                                                              | Bandwidth Reduction via Capacitor                                   |

| 2-7                                                                                                              | A/D Status Register                                                 |

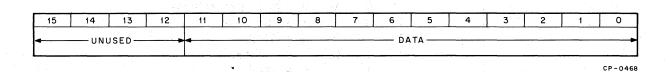

| 2-8                                                                                                              | A/D Buffer Register (Read Only)                                     |

| 2-9                                                                                                              | LED Register (Write Only) 2-11                                      |

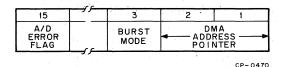

| 2-10                                                                                                             | A/D Status Register Segment 2-14                                    |

| 2-11                                                                                                             | DMA Status Register                                                 |

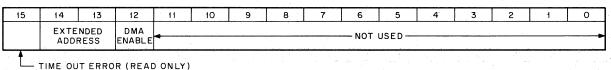

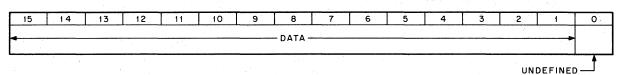

| 2-12                                                                                                             | DMA Word Count Register (Complement) 2-16                           |

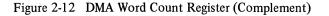

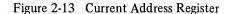

| 2-13                                                                                                             | Current Address Register                                            |

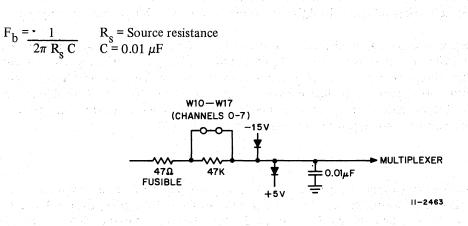

| 2-14                                                                                                             | Switched Gain Multiplexer Input 2-23                                |

| 3-1                                                                                                              | LPSKW Block Diagram                                                 |

| 3-2                                                                                                              | Real-Time Clock Front Panel Section 3-4                             |

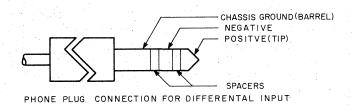

| 3-3                                                                                                              | Input or Output Phone Jack Connections 3-5                          |

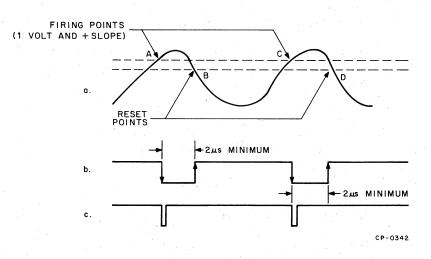

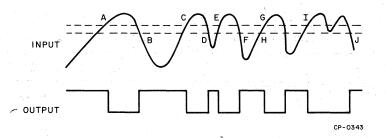

| 3-4                                                                                                              | Schmitt Trigger Firing                                              |

| 3-5                                                                                                              | Schmitt Trigger Firing – Hysteresis                                 |

| 3-6                                                                                                              | LPSKW Status Register 3-9                                           |

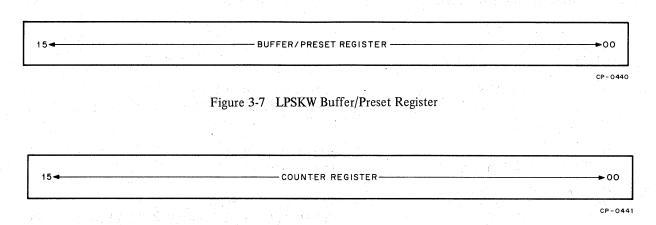

| 3-7                                                                                                              | LPSKW Buffer/Preset Register 3-9                                    |

| 3-8                                                                                                              | LPSKW Counter Register 3-9                                          |

| 4-1                                                                                                              | Digital I/O Block Diagram                                           |

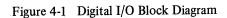

| 4-2                                                                                                              | Input Register Interrupt Switches 4-5                               |

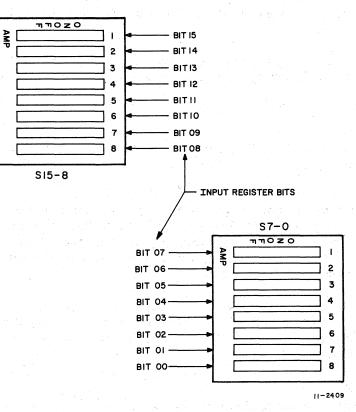

| 4-3                                                                                                              | LPSDR-A Signal Labels for Input/Output Connectors 4-8               |

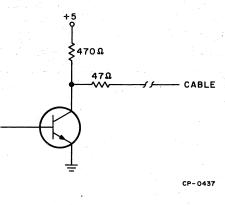

| 4-4                                                                                                              | Cable Driving Circuit                                               |

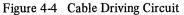

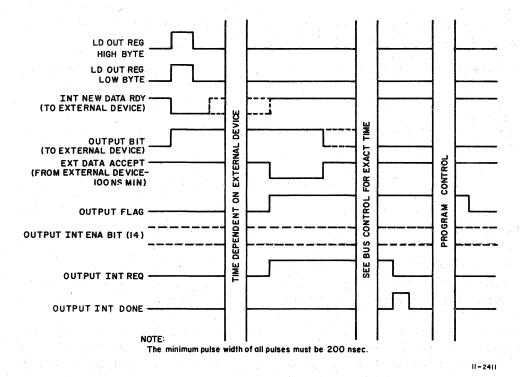

| 4-5                                                                                                              | LPSDR-A Output Timing Diagram 4-10                                  |

| 4-6                                                                                                              | Fime Voltage vs Time Chart for Computing Signal Rise Time           |

# ILLUSTRATIONS (Cont)

Page

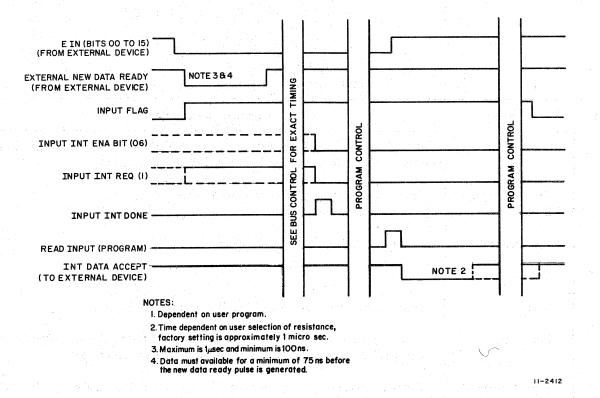

| 4-7 | Input Timing Diagram                  | 4-11 |

|-----|---------------------------------------|------|

| 4-8 | Status Register                       |      |

| 5-1 | LPSVC Block Diagram                   |      |

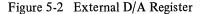

| 5-2 | External D/A Register                 |      |

| 5-3 | Status Register                       |      |

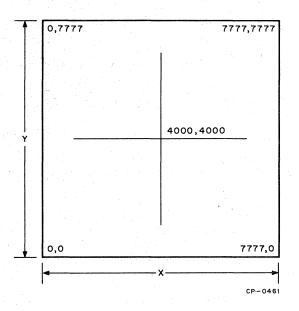

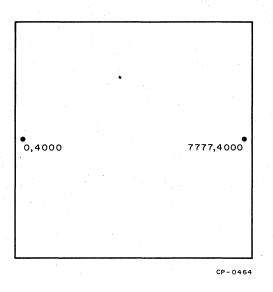

| 5-4 | Scope Grid Coordinate (X, Y)          |      |

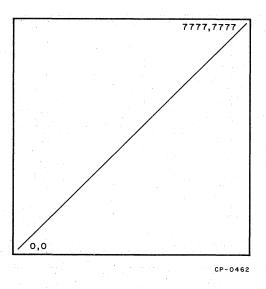

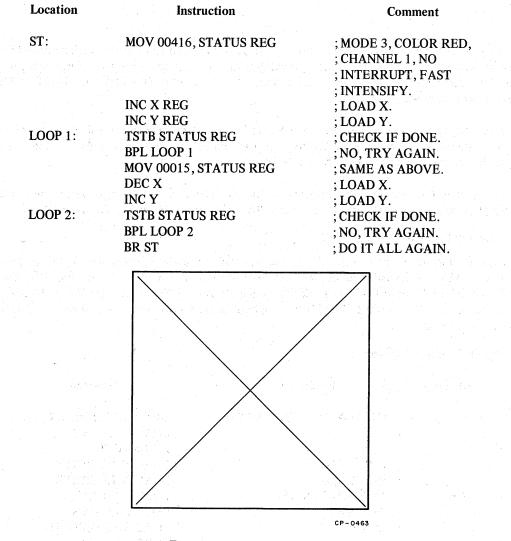

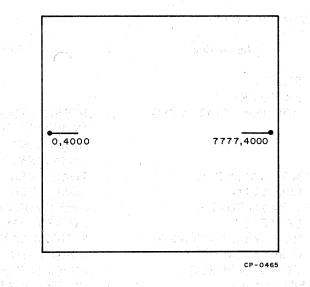

| 5-5 | Program 1 Display                     |      |

| 5-6 | Program 2 Display                     |      |

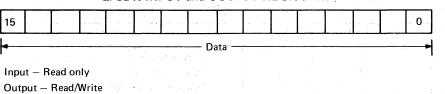

| 5-7 | Normal Intensify – Wait for Done Flag | 5-11 |

| 5-8 | Fast Intensify – Disregard Done Flag  | 5-12 |

# TABLES

## Table No.

| Table No. |                                                          | Page |

|-----------|----------------------------------------------------------|------|

| 1-1       | LPS11-S Configurations                                   | 1-2  |

| 1-2       | LPS11-S Options                                          |      |

| 2-1       | LPSAD-12, LPSAM, and LPSAG/LPSAG-VG                      |      |

|           | Specifications Summary                                   | 2-3  |

| 2-2       | RC1 Analog Inputs                                        | 2-7  |

| 2-3       | LPSAG, LPSAG-VG Range Chart                              |      |

| 2-4       | A/D Status Register                                      |      |

| 2-5       | A/D Buffer Bit Assignments                               |      |

| 2-6       | A/D Status Word and DMA Address                          |      |

| 2-7       | DMA Status Register Bit Assignments                      |      |

| 2-8       | Gain Programming                                         |      |

| 2-9       | 6-Bit Channel Addresses                                  |      |

| 2-10      | Input Ranges                                             |      |

| 2-11      | Least Significant Bit (LSB) Value, Resolution            |      |

| 2-12      | Break Frequencies and Source Resistance Values           |      |

| 2-13      | Throughput Rates                                         |      |

| 3-1       | Schmitt Trigger Specifications for the LPSKW             |      |

| 3-2       | LPSKW Status Register Bit Assignments                    |      |

| 4-1       | Mode Select Jumper Configuration                         |      |

| 4-2       | LPSDR-A Input/Output Pin Assignments                     |      |

| 4-3       | Pulse Width Computations                                 |      |

| 4-4       | Status Register Operation                                |      |

| 5-1       | Pin Assignments for Back Panel Display Connector (RC3)   |      |

| 5-2       | Jumper Arrangements for LPSVC Option                     | 5-3  |

| 5-3       | Scope Specifications                                     | 5-4  |

| 5-4       | Gain Selection                                           |      |

| 5-5       | Polarity Selection (Used with gains listed in Table 5-4) |      |

| 5-6       | D/A Converter Sussifications                             |      |

|           | (Assuming Setup for VR14 or VR20)                        | 5-5  |

| 5-7       | Intensity Pulse Voltage                                  | 5-6  |

| 5-8       | External DAC Register                                    |      |

| 5-9       | Status Register                                          |      |

| A-1       | Priority Ranking for Floating Vectors                    |      |

|           | (Starting at 300 and proceeding upward)                  | A-1  |

# CHAPTER 1 LPS11 SYSTEM

#### **1.1 INTRODUCTION**

The Lab Peripheral System is a high performance, modular, real-time subsystem that interfaces with the PDP-11 family of computers via a single asynchronous bus, the Unibus. The flexibility of the system makes it well suited to a variety of applications, including biomedical research, analytical instrumentation, data collection and reduction, monitoring, data logging, industrial testing, engineering, and technical education.

#### 1.2 SCOPE OF MANUAL

This manual offers the information that the Lab Peripheral System user needs to use the system effectively. Chapter 1 describes the overall system and the interrelationship of its parts from a functional standpoint. Chapters 2 through 5 cover options to the system, including the LPSAD-12 A/D Converter, the LPSKW Real-Time Clock, the LPSDR Digital I/O, and the LPSVC Display Control, respectively. Each chapter contains a detailed description of the option, as well as programming information. Instructions, register addresses, and vector addresses are listed in the appendices.

#### **1.3 GENERAL DESCRIPTION**

The Lab Peripheral System includes a 12-bit A/D converter, a programmable real-time clock with two Schmitt triggers, a display controller with two 12-bit D/A converters, and a 16-bit digital I/O option. Dual sample-and-hold preamplifiers and direct memory access capabilities for the A/D system are also available on an optional basis.

The front panel of the LPS11-S is designed to facilitate interfacing with outside instrumentation. The LPS11-S is 5-1/4 in. high, and mounts in a standard 19-in. cabinet. The power supply and all necessary cabling are included.

#### **1.4 DETAILED DESCRIPTION**

The Lab Peripheral System is available in six standard configurations, listed in Table 1-1. These are divided into rack mountable and table top configurations, and each is available for operation with 115V, 50/60 Hz, 230V, 50/60 Hz, or 100V, 50/60 Hz input power.

Up to nine different option types may be added to the basic Lab Peripheral System package. These options and their prerequisites are listed in Table 1-2, and are described in greater detail in succeeding chapters.

#### 1.4.1 Standard LPS11-S

The standard LPS11-S is the basic unit of the Lab Peripheral System. It is housed in a 5-1/4 in. box, and includes power supply, bus control, prewired backplane, and front and back panels. The LPS11-S connects to any PDP-11 computer via a standard Unibus cable.

| Designation | Description                                                                                                        |

|-------------|--------------------------------------------------------------------------------------------------------------------|

| LPS11-SA    | Lab Peripheral System mounting unit, front panel, Unibus interface, and power supply. Rack mountable. 115V, 60 Hz. |

| LPS11-SB    | Same as above except 230V, 50 Hz.                                                                                  |

| LPS11-SC    | Same as above except 100V, 50 Hz.                                                                                  |

| LPS11-SD    | Lab Peripheral System mounting unit, front panel, Unibus interface, and power supply. Table top. 115V, 60 Hz.      |

| LPS11-SE    | Same as above except 230V, 50 Hz.                                                                                  |

| LPS11-SF    | Same as above except for 100V, 50 Hz.                                                                              |

Table 1-1 LPS11-S Configurations

| Туре No. | Description                                                                                                                                                                    | Prerequisites         |  |  |  |  |  |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|--|--|--|--|--|

| LPSAD-12 | 12-bit ADC, sample & hold, 8-channel multiplexer, and LED (light-emitting diodes) 6-digit programmable decimal readout display.                                                |                       |  |  |  |  |  |

| LPSAD-NP | Direct memory access (DMA) option for the LPSAD-12 ADC.                                                                                                                        | LPSAD-12              |  |  |  |  |  |

| LPSAM    | Eight-channel expansion multiplexer.                                                                                                                                           | LPSAD-12              |  |  |  |  |  |

| LPSSH    | Second sample & hold; implement if a dual sample & hold configuration is required.                                                                                             |                       |  |  |  |  |  |

| LPSAG    | Four differential preamplifiers with $\pm 1V$ input. Maximum of 4 LPSAGs per LPS11-S system.                                                                                   | LPSAD-12 or<br>LPSAM* |  |  |  |  |  |

| LPSAG-VG | Four independently selectable multigain differential preamplifiers.<br>Ranges: $\pm 1V$ , $\pm 5V$ , 0 to $\pm 2V$ , 0 to $\pm 10V$ ; all differential inputs.                 | LPSAD-12 or<br>LPSAM* |  |  |  |  |  |

| LPSKW    | Programmable real-time clock and two Schmitt triggers.                                                                                                                         | LPS11-S               |  |  |  |  |  |

| LPSVC    | Display control including two 12-bit DACs. This controller is capable of handling DEC VR14 and VR20 CRT displays. Also, Tektronix RM503, 602, 604, 611, and 613 oscilloscopes. | LPS11-S               |  |  |  |  |  |

| LPSDR    | Sixteen-bit buffered digital I/O with drive capabilities and two programmable N.O. relays.                                                                                     | LPS11-S               |  |  |  |  |  |

Table 1-2 LPS11-S Options

\*If more than eight channels are implemented.

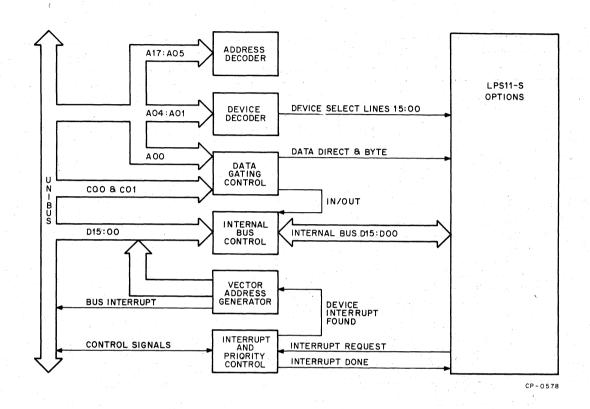

1.4.1.1 Bus Control – The bus control of the LPS11-S is an interface between the Unibus and the internal bus and LPS11-S options. The bus control forms its own internal bus (Figure 1-1), permitting the system to address up to six options, cause interrupts, and transfer data. It can decode up to 16 sequential addresses. These addresses are jumper selectable; changing the jumpers changes the total block of 16, but the respective ordering remains the same.

Figure 1-1 LPS11-S Bus Control Block Diagram

The bus control can handle six interrupts at individual bus priorities. Each option has its own interrupt and interrupt vector address (vector addresses are also selectable, and are defined as a floating vector field), its own interrupt priority chip (pluggable on the bus control), and its own enable/disable jumper for interrupts.

Bus control interfacing involves address lines, interrupts, and priorities.

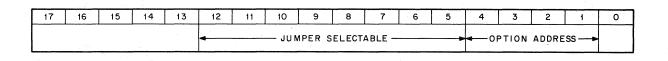

- a. Address Lines Eighteen address lines are used to address the Lab Peripheral System and its options. The address register is shown in Figure 1-2. Bits 12–05 are jumper selectable (A12 through A05 jumpers), allowing the user to change the address block. The module is shipped with addresses as shown in Appendix A; these may be changed, but the respective ordering will remain the same.

- b. Interrupts Interrupts may occur at any time from any Lab Peripheral System device. Upon issuance of an interrupt request from the device, the interrupt control of the bus control checks the BG and BR lines for priorities. When a BG is generated, the vector address generator sends an interrupt vector address to the Unibus. A bus interrupt is then generated, and the processor interrupts to the address specified by the vector address generator. Appendix A illustrates the vectors and their floating addresses. These addresses are sequential in nature, and exist between locations 000 and 777 (jumper assignable).

Priorities – Priorities are necessary when two or more interrupts occur simultaneously. When this occurs, the bus grant priority control examines the interrupt requests and determines which device has the highest priority. That device is handled first, after which the next highest priority is established. This priority chaining (Figure 1-3) allows interrupts to be handled efficiently.

CP-0483

Figure 1-3 Priority Chaining of LPS11 System

If Device A and Device C and Device E should all interrupt simultaneously, the bus grant priority control would allow Device A (Level 6 is high) to interrupt first (Devices C and E are Level 4, which is low). After the Device A interrupt is completed, Device C would be granted the next interrupt because it is electrically closer to the PDP-11 than is Device E, even though both are Level 4. Finally, Device E would be granted its interrupt.

The levels of operation indicated in Figure 1-3 are interchangeable. The bus control is shipped in this configuration, which is suggested for the user. If the levels are changed, however, the user must consider the following:

• Device importance

c.

- Size of typical device transfer (number of words maximum)

- Duration of typical transfer (time maximum).

**1.4.1.2** Power Supply – Power for the LPS11-S is supplied by a special supply, providing +5V at 13A and  $\pm 15V$  at 2A each.

**1.4.1.3** Front Panel – The front panel of the LPS11-S is divided into three main areas (Figure 1-4). The largest of these areas, labeled ANALOG INPUT, includes phone jacks for inputs to analog channels 0-7, potentiometer knobs for channels 0-3, and a 6-digit light emitting diode (LED) display. This area is described in greater detail in Chapter 2 of this manual, covering the LPSAD-12 A/D Converter.

Figure 1-4 LPS11-S Front Panel

The second area of the LPS11-S front panel, labeled REAL TIME CLOCK, includes an output jack for the clock counter overflow and identical sets of controls and phone jacks for Schmitt triggers 1 and 2, each set consists of an input jack, an output jack, a slope polarity switch, and a firing level potentiometer. This area is described in greater detail in Chapter 3 of this manual, covering the LPSKW Real-Time Clock option to the Lab Peripheral System.

The third area of the front panel includes two pair of binding posts, labeled RELAY 1 and RELAY 2 after the two normally-open relays that they represent. These are controlled by the LPSDR Digital I/O option to the Lab Peripheral System, and are described more completely in Chapter 4 of this manual.

**1.4.1.4** Back Panel – The back panel of the LPS11-S contains four 25-pin connectors which service three of the options to the Lab Peripheral System. Each connector is labeled to indicate which option it services, and is added to the box when the related option is added to the system. The connectors are routed through a connector shield board to the options (Figure 1-5). Pin assignments for the individual connectors are listed in tabular form in the chapters covering their related options.

Figure 1-5 LPS11-S Laboratory Peripheral System and Options, Block Diagram

1-6

ŧ,

3

# CHAPTER 2 ANALOG-TO-DIGITAL CONVERTER SUBSYSTEM

#### 2.1 GENERAL DESCRIPTION

The analog-to-digital subsystem enables the Lab Peripheral System user to sample analog data at specified rates and to store the equivalent digital value for subsequent processing. The basic subsystem consists of an 8-channel multiplexer (eight single-ended  $\pm 5V$  inputs), sample-and-hold circuitry, a 12-bit A/D converter, and six programmable light emitting diode (LED) numerical readouts. Available options provide for:

- a. System Expansion The LPSAM multiplexer makes it possible to expand the LPSAD-12 to 16 channels.

- b. Dual Sample-and-Hold The LPSSH option permits the user to acquire data from two fixed and predetermined channels simultaneously.

- c. Direct Memory Access (DMA) The LPSAD-NP option allows the transfer of data to memory at maximum rates without processor intervention, eliminating the software overhead of programmed I/O transfers.

- d. Preamplification The LPSAG option implements four channels with preamplifiers and provides a  $\pm 1V$  differential input to each of those channels. Ranges of 0 to 2V,  $\pm 5V$ , and 0 to 10V are additionally available via the LPSAG-VG option.

#### 2.1.1 Block Diagram

Figure 1-5 shows an expanded A/D subsystem for the Lab Peripheral System in block diagram form. The basic subsystem may be expanded to a more elaborate configuration that includes 16 multi-range differential channels, dual sample-and-hold, a 12-bit analog-to-digital converter (ADC), and the direct memory access (DMA) interface, as well as a real-time clock. The clock is described more completely in Chapter 3; the other available options are described in the following paragraphs.

#### 2.2 DETAILED DESCRIPTION

#### 2.2.1 LPSAD-12

The LPSAD-12 is a 12-bit successive approximation A/D converter, consisting of four functional modules: an M7018 A/D Control module, an A804 A/D Converter module, an A406 Sample-and-Hold module, and an A407 8-Channel A/D Multiplexer module.

The M7018 A/D Control module controls all A/D operations. Its status register decodes multiplexer operation, sample-and-hold operation, A/D converter operation, and DMA operation. The A/D buffer register receives the converted analog signal in offset binary format.

A/D conversion may be initiated by a programmed instruction, or, if the Lab Peripheral System configuration includes the LPSKW Real-Time Clock, by either the overflow from the clock counter or the firing of a Schmitt trigger. During the conversion, the sample-and-hold mode is changed from sample to hold. The converted offset binary data is placed in the control module A/D buffer register, where it may be tested by the processor, cause an interrupt, or be transferred to memory.

The A804 A/D Converter module, although shipped as a 12-bit A/D converter, is capable of being used an an 8-, 9-, 10-, 11-, or 12-bit converter. The number of bits converted is determined by the position of rotary switch S1 on the A804 module. Conversion time is set using potentiometer R23, which is the center potentiometer on the module. Recommended conversion times are as follows:

8-Bit: 4.5 μs 9-Bit: 6 μs 10-Bit: 8 μs 11-Bit: 15 μs 12-Bit: 19 μs

For improved differential linearity, the 12-bit conversion may be set for as high as  $25 \ \mu s$ .

#### 2.2.2 LPSAM

The LPSAM option consists of a single A407 8-Channel A/D Multiplexer module, which operates in the same manner as the 8-channel multiplexer of the LPSAD-12. When not preceded by a preamplifier, it provides eight single-ended  $\pm 5V$  inputs.

#### 2.2.3 LPSAG/LPSAG-VG

The LPSAG and LPSAG-VG options provide preamplification for the analog channels. The LPSAG provides a  $\pm 1V$  differential input to each of the four channels it serves. Two LPSAGs are needed to amplify all eight channels of the basic LPSAD-12. Two more are required if an LPSAM is implemented into the Lab Peripheral System.

The LPSAG-VG, which is also a 4-channel preamplifier, operates in a manner similar to the LPSAG in providing a  $\pm 1$ V input, but also offers additional gain and offset ranges of 0 to 2V,  $\pm 5$ V, and 0 to 10V. The input ranges for each of the four channels are individually selectable, as described in Paragraph 2.3.2.

#### 2.2.4 LPSSH

The LPSSH option is contained on a single A406 Sample-and-Hold module, and provides dual sample-and-hold capability. The basic sample-and-hold circuitry ensures adequate conversions, even on rapidly changing signals, by holding the input voltage constant until the conversion process is complete. The LPSSH permits simultaneous sampling of two fixed and predetermined channels, and is controlled by the status register.

The system must contain both the basic LPSAD-12 and an LPSAM as prerequisites to the LPSSH.

#### 2.2.5 LPSAD-NP

The LPSAD-NP Direct Memory Access (DMA) interface consists of a single M7020 DMA module. The primary function of this interface is to store data faster than normal I/O programming will allow. The throughput rate of A/D conversions can be increased from 40 kHz to the actual converter speed (50 kHz-12 bits/100 kHz-10 bits/150 kHz-8 bits). The LPSAD-NP is designed primarily for single-channel operation; however, dual-channel operation is also possible.

The only prerequisite for the LPSAD-NP is the LPSAD-12.

#### 2.3 USER INTERFACING

The LPSAD-12 is the basic building block of the Lab Peripheral System A/D converter subsystem. Access is via the front panel, shown in Figure 2-1. Table 2-1 contains specifications for the LPSAD-12, LPSAM, and LPSAG/LPSAG-VG.

ξ.

Figure 2-1 Analog Section of Front Panel

| Characteristic                    | Specification                                                                                                                   |

|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| LPSAD-12 A/D Converter Option     |                                                                                                                                 |

| Input voltage range               | ±5V, single-ended                                                                                                               |

| Input channels                    | 8                                                                                                                               |

| Input impedance                   | $10^9\Omega$ in parallel with 100 pF, measured at rear panel.                                                                   |

| Input bias current                |                                                                                                                                 |

| Channel on (±10V input)           | 200 nA typ. For -10V <v <+10v<br="" in="">(Input clamps to ±10V)<br/>Switching transient = -5 mA maximum<br/>0.5 μs maximum</v> |

| Crosstalk                         | 80 dB at 1 kHz, rolling off at 20 dB per decade.                                                                                |

| Warmup time                       | 3 minutes                                                                                                                       |

| Control                           | Controlled by programmed instructions, clock counter overflow, or Schmitt trigger from LPSKW                                    |

| Maximum program throughput rate   | PDP-11/20 with optimal coding:                                                                                                  |

| Programmed start                  | 40 kHz typical                                                                                                                  |

| Overflow or Schmitt trigger start | 45 kHz typical                                                                                                                  |

| Table 2-1                           |  |  |  |  |  |

|-------------------------------------|--|--|--|--|--|

| LPSAD-12, LPSAM, and LPSAG/LPSAG-VG |  |  |  |  |  |

| Specifications, Summary             |  |  |  |  |  |

| Characteristic                      | Specification                                                                                                        |  |  |  |  |

|-------------------------------------|----------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| PSAD-12 A/D Converter Option (Cont) |                                                                                                                      |  |  |  |  |

| Resolution                          | 12 bits (1 part in 4096) can be reduced to 8, 9, 10, or 11 bits for faster conversion time with switch on module     |  |  |  |  |

| Dutput format                       | Parallel, 12 bits, right justified, offset binary, double buffered                                                   |  |  |  |  |

| Accuracy, at 25°C                   | ±0.035% of full scale                                                                                                |  |  |  |  |

| inearity                            | 0.02% of full scale                                                                                                  |  |  |  |  |

| Differential linearity              | 1 LSB                                                                                                                |  |  |  |  |

| Cemperature stability               | 30 ppm/°C<br>(0.003%FS/°C)                                                                                           |  |  |  |  |

| Repeatability                       | $2\sigma \leq 1/2$ LSB                                                                                               |  |  |  |  |

| Conversion time                     | The time lapse from start command until a 12-bit result is acquired is 20 $\mu$ s.                                   |  |  |  |  |

| PSAM Multiplexer Option             |                                                                                                                      |  |  |  |  |

| nput voltage range                  | ±5V, single-end                                                                                                      |  |  |  |  |

| nput channels                       | 8                                                                                                                    |  |  |  |  |

| nput impedance                      | $10^9\Omega$ in parallel with 100 pF, measured at rear panel                                                         |  |  |  |  |

| nput bias current                   |                                                                                                                      |  |  |  |  |

| Channel on (±10V input)             | 200 nA typ. For -10V < V in <+10V<br>(Input clamps to ±10V)<br>Switching transient = -5 mA maximum<br>0.5 μs maximum |  |  |  |  |

| Channel off                         | 200 nA typ.                                                                                                          |  |  |  |  |

| Crosstalk                           | 80 dB at 1 kHz, rolling off at 20 dB per decade                                                                      |  |  |  |  |

| Analog output voltage range         | ±5V                                                                                                                  |  |  |  |  |

# Table 2-1 (Cont)LPSAD-12, LPSAM, and LPSAG/LPSAG-VGSpecifications Summary

| Characteristic                      | Specification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LPSAG/LPSAG-VG Preamplifier Options |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Input voltage range                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| LPSAG<br>LPSAG-VG                   | ±1V differential<br>±1V, 0 to +2V,<br>±5V, 0 to +10V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Input channels                      | $\frac{1}{2} = \frac{1}{2} \left[ \frac{1}{2} + 1$ |

| Crosstalk                           | 80 dB at 1 kHz, rolling off at 20 dB per decade                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Input impedance                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| + to ground<br>-to ground           | 128K in parallel with 100 pF<br>64K in parallel with 100 pF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Differential                        | 128K in parallel with 50 pF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Input bias current                  | 40 nA maximum at + or – input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |