## Disk Control Products Specification Booklet

# Table of Contents

Am9580 Hard Disk Controller (HDC)

Am9581 Floppy/Hard Disk Data Separator

© 1984 Advanced Micro Devices, Inc.

Advanced Micro Devices reserves the right to make changes in its products without notice in order to improve design or performance characteristics. The company assumes no responsibility for the use of any circuits described herein.

901 Thompson Place, P.O. Box 3453, Sunnyvale, California 94088 (408) 732-2400 TWX: 910-339-9280 TELEX: 34-6306

Printed in U.S.A.

## Am9580

Hard Disk Controller (HDC)

#### ADVANCED INFORMATION

#### DISTINCTIVE CHARACTERISTICS

- · Linked list command and data structure

- Controls up to 4 drives, any combination of hard or floppy disk drives

- ST506/412 and user defined disk interface options supported

- Two on-chip sector buffers are programmable for sector sizes of 128, 256, and 512 bytes

- Error checking algorithms supported include

- CRC/CCITT

- Single burst Reed-Solomon

- Double burst Reed-Solomon

- External ECC (Error Correcting Code)

- On-chip DMA capability supports 32-bit addressing in 8/16-bit systems

#### GENERAL DESCRIPTION

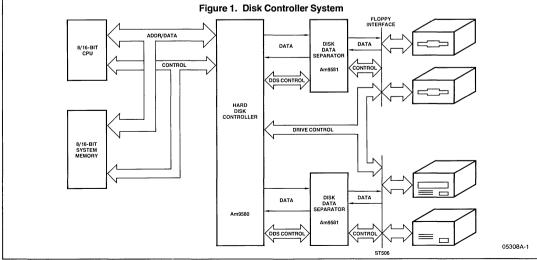

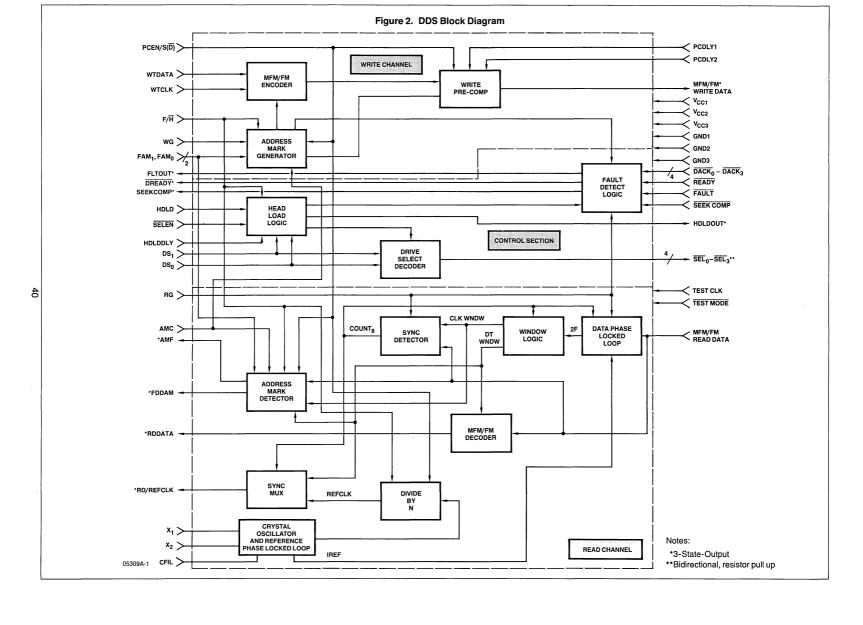

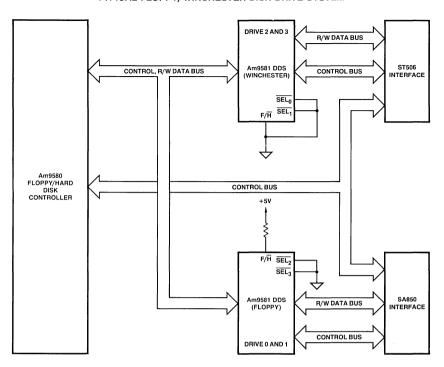

The Am9580 Hard Disk Controller (HDC) is a single chip solution to the problems encountered in designing Data Formatters and Disk System Controllers. Together with its companion part, the Am9581 Disk Data Separator (DDS), the Am9580 provides all the functions which until now have been found only on sophisticated board-level products.

The Am9580 has been designed with the necessary flexibility to cope with the differing requirements of today's broad marketplace while still retaining the advanced technology and innovative features that tomorrow's market will demand.

The Am9580 supports both Rigid and Flexible Disk Drives and their accompanying Data Formats. The Am9580 can control up to four drives, allowing any mix of Rigid and Flexible drives. As the characteristics of each drive are independently user-programmable, the system designer is provided with the flexibility needed to control any disk drive.

A sophisticated on-chip DMA Controller fetches the commands, writes status information, fetches data to be written on disk and writes data read from disk. The DMA operation is programmable to adjust the bus occupancy, data bus width (8-bit or 16-bit), and wait state insertion. Two sector buffers allow zero sector interleaving to access data on physically contiquous sectors, improving both file access

time and system throughput. The buffers are programmable for sector sizes of 128, 256, and 512 bytes.

The Am9580 insures data integrity by selecting one error detecting code (CRC-CCITT), or one of two error correcting codes (single and double burst Reed-Solomon). Additionally, the HDC provides handshake signals to control external ECC circuitry to implement any ECC algorithm.

The Am9580 provides signals which are necessary to control external Encode/Decode and Address Mark circuitry such as found on the Am9581. By partitioning the Disk Control System in this way, future developments in the field of Data Encoding can still take advantage of the HDC's advanced Data Formatting and Control capabilities.

The flexible, user programmable disk interface can be configured to control ST506 or standard Floppy Disk interfaces with only a few buffers required and can easily be adapted to other interface standards.

The Am9580 provides a comprehensive, high level command set for multi-sector disk I/O, marginal data recovery, diagnostics and error recovery. Commands may be linked together to be executed sequentially by the Am9580 without any host intervention. This linked list command structure also simplifies command insertion, deletion, or rearrangement.

This document contains information on a product under development at Advanced Micro Devices, Inc. The information is intended to help you to evaluate this product. AMD reserves the right to change or discontinue work on this proposed product without notice.

Order # 05308A

## **HDC Logic Symbol**

05308A-26

HDC Connection Diagram (not yet available)

## **FUNCTIONAL OVERVIEW**

#### HARDWARE ARCHITECTURE

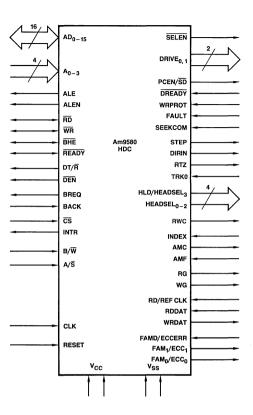

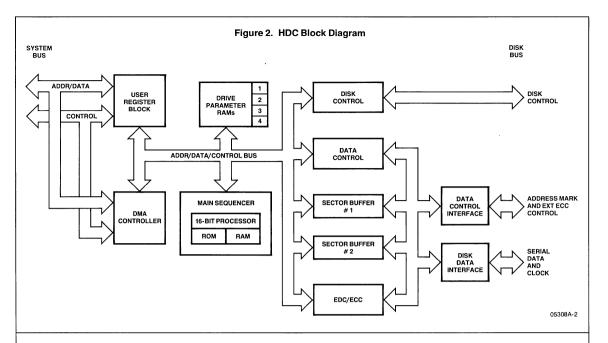

The HDC supports two interfaces as shown in the block diagram in Figure 2; the system interface communicates with the host CPU and system memory, and the disk interface controls the data separator and the disk drives.

#### System Interface

The HDC is designed for easy interfacing to most 8-bit or 16-bit, multiplexed or demultiplexed, synchronous or asynchronous microprocessor buses. A strap pin programs the system interface for either byte (8-bit) or word (16-bit) mode. In Slave Mode, the host CPU can access the internal registers of the HDC. In Master Mode, the on-chip DMA controller controls the system bus.

#### **DMA Controller**

The on-chip DMA controller provides the HDC with the ability to execute complex disk I/O operations without intervention by the host CPU. The DMA controller scans the command chain stored in system memory, updates the Status Result Area when errors occur, and transfers the data between the internal sector buffers and system memory. Data may optionally be stored in noncontiguous memory to support linked-list data storage in word processing systems.

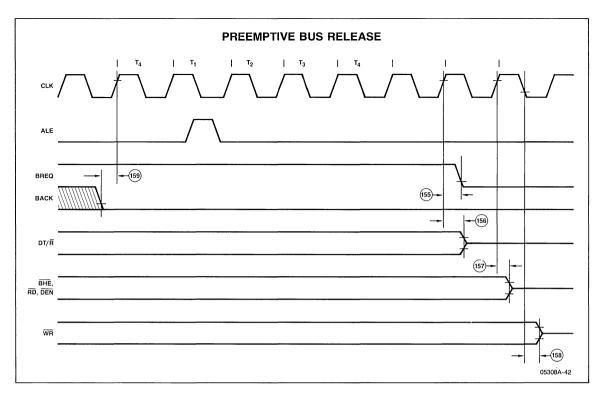

The DMA controller generates 32-bit linear addresses to access system memory of up to 4 GBytes directly. For multiple bus master systems, the DMA transfers can be throttled to dedicate only a certain share of the system bus bandwidth to the HDC. The Mode Register specifies the DMA burst length and dwell time. DMA bursts can be preempted by removing Bus Acknowledge (BACK). The HDC can insert a programmable number of software Wait States into DMA bus cycles. Additionally, hardware Wait States can be added via the  $\overline{\text{READY}}$  input. The HDC updates the upper address word (A $_{16}$  to A $_{31}$ ) when a carry out of the lower 16 bits indicates it is necessary.

#### **User Registers**

The Mode Register defines the operation of the DMA controller. The Status/Command Register controls the basic operation of the HDC itself. The Next Block Pointer (NBP) Register links to the first Input/Output Parameter Block (IOPB) of the command chain. The Status Result Pointer Register and the Status Result Length Register define the Status Result Area.

#### Main Sequencer

The main sequencer translates the high-level system commands into the control signals for the various independent functional sections of the HDC. The power of this 16-bit processor is used to ease the complex data manipulation burden of the system CPU.

#### **Drive Parameter RAMs**

The Drive Parameter RAMs store the specification parameters for individual drives that adapt the HDC to any combination of disk recording schemes. The contents can be altered

at any time with a single IOPB. Once loaded these parameters allow disk commands to be independent of the drive format. For example, the write command is the same whether it is for a single-density floppy disk drive or a Winchester hard disk drive.

#### **Error Checking**

The HDC features two powerful Reed-Solomon errorcorrecting codes, as well as the industry-standard errordetection code, CRC-CCITT. It also supports user-definable, external error-correction schemes. These, along with the programmable retry and and correction attempt policy, allow maximum control of data integrity.

#### Sector Buffers

The HDC transfers data to or from disk without adding time constraints on the system bus bandwidth. The two internal sector buffers can be filled or emptied at any speed without interfering with the data transfer between the sector buffers and the disk. The two internal sector buffers can be toggled for zero sector interleave disk data operations. While one sector buffer is filled with data from disk, the other buffer is emptied by the DMA controller. Physically contiguous sectors on a track can thus be read or written on the fly.

#### **Disk Control Interface**

The lines of the Disk Control Interface conform to the ST506 disk drive interface standard. Other drive interface standards can be supported with some external circuitry. The ST506 interface selects one of the four disk drives and one of up to 16 heads. Any combination of floppy disk and hard disk drives can be connected. The Drive Parameter Blocks specify the seek dwell, seek pulse width, and head settle timing.

The HDC can perform implied and overlapped seeks. When the implied seek option is selected, the HDC automatically causes the appropriate seeks when issuing a read or write command. If this option is disabled, then the HDC should be issued separate seek commands before executing read or write commands.

When the overlapped seek option is selected, drives can seek in parallel, thus minimizing the seek overhead in multiple disk drive systems. After the HDC has issued a seek command to one drive and while this drive performs the seek, the HDC scans subsequent IOPBs for commands requiring seeks on other drives. If the HDC finds such commands, it issues seek commands to these drives to make them seek in parallel. On receiving a "Seek Complete" from the first drive, the HDC resumes execution of the command chain.

#### **Disk Data Interface**

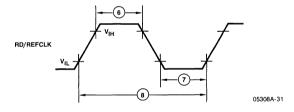

The Disk Data Interface controls the Address Mark handshake with the data separator, controls the optional external ECC logic, and handles the serial data input and output. Operating asynchronously to the other blocks of the device, the Disk Data Interface is driven by the Read/Reference Clock (RD/REF CLK) generated by the data separator. The Disk Data Interface converts the data stored in the sector

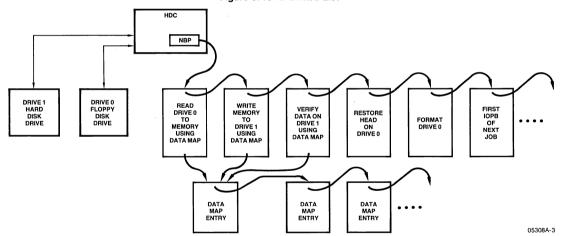

The IOPB chain in Figure 3 copies the data of a floppy disk to a hard disk, verifies the data, and, when the verification is successful, formats the floppy disk. First it reads the data from the floppy disk into a temporary buffer in system memory. The data-mapping option lets the system use any free memory space. The subsequent write command uses the same data map to transfer data to the hard disk. The verify command ensures that data was written correctly by performing a byte-by-byte comparison of the data on the hard disk with the data in the temporary buffer. Optionally, the chain execution may be stopped in the event of an error in the write or verify command. If there was no problem with the data transfer, the HDC will perform the restore and for-

mat commands. Optionally, the system can be informed that the disk copy has been completed and that the memory space allocated for the temporary buffer of the disk data is free to be reused.

The seek-lookahead mechanism of the HDC will move forward through the IOPB chain to see where it can overlap head seeks. In this example, the HDC will move the head on the hard disk into position for the write command while the read command is still executing. When the HDC starts executing the write command, it will look ahead in the chain and start executing the restore command on the floppy drive to move the head back to track zero. If possible, the HDC will do additional head positioning for commands further down the IOPB chain.

buffer into a serial bit stream for the disk or it de-serializes the incoming bit stream to be loaded into one of the sector buffers. Non-data information, such as the header, pads, gaps, preambles, and postambles, is conditioned according to the parameters stored in the Drive Parameter RAMs to meet the defined recording standard.

#### SOFTWARE ARCHITECTURE

#### **IOPB Command Structure**

The HDC features a high-level data and command structure. The basic unit of a command structure is the Input/ Output Parameter Block (IOPB). The host CPU creates IOPBs in system memory to pass control and status information to the HDC. The HDC fetches these IOPBs using its on-chip DMA controller. Each IOPB specifies one disk command and contains all parameters needed to execute it. To start execution of an IOPB, the host CPU loads the address of the first IOPB into the Next Block Pointer Register and issues the command "Start Chain" by programming the Status/Command Register. After the IOPB is executed the HDC reports the status information and waits for further instructions. The host CPU can examine the Status/ Command Register for information about the command termination. The CPU can also get status from the Status Result Block in memory if an error occurs.

Optionally, IOPBs may be connected in a linked-list format which the HDC can interpret sequentially. With this structure, a complex list of disk commands can be set up and executed by the HDC without CPU intervention. The CPU is then totally free from any processing for disk control. For example, the host CPU can set up a list of commands to copy an entire floppy disk to a hard disk, verify that the data was copied correctly, and, if so, reformat the floppy disk—all without host CPU intervention.

An IOPB command chain is basically a queue of jobs waiting for execution by the HDC. This offers a pre-defined and efficient structure for the operating system to handle its disk I/O. The ID field of the IOPB allows the operating system to link a particular disk command to the user process that made the disk request. The jobs can thus be placed in the HDC job queue and then forgotten by the operating system unless an error occurs. All the information required to retrace an error is provided by the HDC Status Result Block.

Since the HDC manages the disk job queue, it can look ahead in the queue to overlap some time-consuming operations. Head movement (seeking) can require a major portion of the disk access time. Since the HDC controls up to four drives, it can perform an IOPB operation on one drive while it is executing seeks for future IOPBs on the other drives. This can eliminate the seek-time overhead when those subsequent IOPBs are finally executed.

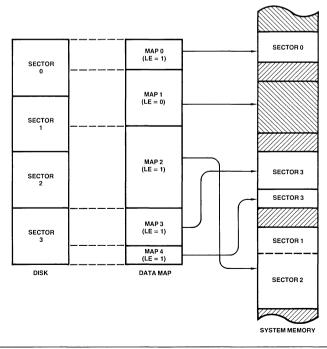

#### **Data Mapping**

Sector data to be transferred to or from the disk may be stored in noncontiguous system memory using the data mapping option. Definable portions of a disk file can be written to or read from separate areas of memory on a byte-bybyte basis. Word processing systems can employ this feature to save text arranged in a linked-list directly on disk and eliminate the time-consuming task of converting the linked-list into a linear list. The Data Map defines the linked-

list data structure. The Data Map option is processed by the HDC while the disk is in operation, so that data maps can be handled without affecting data transfer rate.

#### Status Result Blocks

When the HDC finds that an IOPB has caused an error, it writes a Status Result Block (SRB). Errors can be caused by invalid command codes, disk read and write errors, and seek or memory time-outs. Since the SRB contains the ID number for the IOPB which caused the error, the operating system can determine which disk I/O job caused the error and report this to the user. Depending upon the type of error and what policy has been selected, the HDC may continue with the IOPB chain automatically or wait for the host processor to tell it whether to start over or continue. The SRBs contain all the specific information required to find the exact location of the error and to make recovery as complete as possible.

#### Registers

When the IOPB command chain has been set up, the Next Block Pointer Register of the HDC should be set to point to the first IOPB in the chain. Writing a Start Chain command to the Status/Command Register causes the HDC to copy the first IOPB into its internal memory. It starts executing the IOPB after updating the Next Block Pointer to the next command in the IOPB chain. The Status/Command Register also reports HDC error and status codes (such as memory time-outs, IOPB option results, and other information related to the internal operation of the HDC).

The Status Result Pointer points to an area of memory reserved for Status Result Blocks (SRBs). The length of this memory block is defined by the Status Result Length Register, which specifies the number of SRBs. (Each SRB is 10 bytes.) The error-handling scheme of the operating system can manipulate this as needed to coordinate disk use.

The Mode Register controls the HDC's share of the system bus bandwidth to adapt the HDC to the system performance requirements.

### REGISTER DESCRIPTION

Four registers control the operation of the HDC. These registers can be accessed directly by the host CPU. The addresses are shown in Figure 4.

#### MODE REGISTER

Bit assignments of this 16-bit read/write register are shown in Figure 6. This register may be read or written at any time. A hardware or software reset initializes all bits in this register to zero. DMA Burst Length and DMA Dwell Time control the share of the system bus bandwidth allocated to the HDC. DMA Burst Length defines the maximum length of a DMA burst in bytes and DMA Dwell Time specifies the minimum time between DMA bursts that the HDC must stay off the system bus.

Wait Select (WS) defines the number of software Wait States that are inserted into bus transactions. The HDC inserts this number of Wait States and then waits until the READY line is activated (hardware Wait States). If no acknowledge is received within 2<sup>16</sup> clock periods, a time-out error is generated.

Figure 4. Register Addresses

| cs | Аз | A <sub>2</sub> | A <sub>1</sub> | Register Accessed                 |

|----|----|----------------|----------------|-----------------------------------|

| L  | L  | L              | L              | Status/Command Register           |

| L  | L  | L              | Н              | Mode Register                     |

| L  | L  | Н              | L              | Next Block Pointer (low word)     |

| L  | L  | Н              | н              | Next Block Pointer (high word)    |

| L  | Н  | L              | L              | Status Result Pointer (low word)  |

| L  | Н  | L              | н              | Status Result Pointer (high word) |

| L  | Н  | Н              | L              | Status Result Length              |

| L  | Н  | н              | н              | Reserved                          |

| Н  | х  | X              | Х              | No Register Accessed              |

Figure 5. Data Bus Assignment for Byte/Word Transfers

| MODE        | B/W | BHE | A <sub>0</sub> | AD (15 : 8) | AD (7:0) |

|-------------|-----|-----|----------------|-------------|----------|

|             | L   | L   | L              | HIGH        | LOW      |

| Word Access | L   | н   | L              | _           | LOW      |

|             | L   | L   | н              | HIGH        | -        |

| Puta Assess | н   | Н   | L              | -           | LOW      |

| Byte Access | Н   | Н   | Н              | _           | HIGH     |

## Figure 7. Status/Command Register

The two seek bits control the seek mode. When the Implied Seek option is enabled, the HDC automatically positions the head to the desired track when executing disk commands. This means that explicit seek commands need not precede disk read and write commands. Overlapped seeks are seeks on multiple drives in parallel. In Restricted Mode, seek operations are controlled by external logic. Therefore STEP, DIRIN, and RTZ should not be connected. In Buffered Mode, seek operations and drive selection are handled externally. Therefore, all disk control lines should not be connected. In Buffered Mode the HDC controls only the data transfer (RDDAT, WRDAT, RD/REF CLK and WG), the data separator handshake and ECC operation (AMC, AMF, INDEX, FAM/ECC(1:0), and FAMD/ECCERR).

When the Lock-out bit is set, the HDC does not read or modify internal registers. It also keeps the DMA off the system bus. However, dependent on the time this bit is being set, it may execute further DMA bursts to finish the current sector transfer

The Interrupt Mask enables and disables the interrupts output pin.

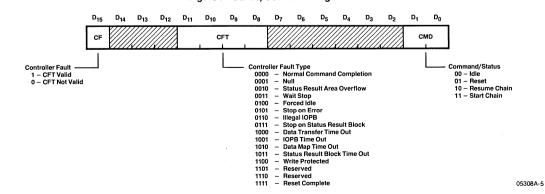

#### STATUS/COMMAND REGISTER

The host CPU can access the Status/Command Register any time (Figure 7). The execution of some commands modify the content of this register. A hardware or software reset initializes all bits of the Status/Command Register to zero.

#### Command

When the command field is written by the host CPU, it causes the HDC to enter the programmed state. By reading this field, the host CPU can determine the state of the HDC.

Idle The HDC is not performing any action.

If CF (Controller Fault) is asserted, then

CFT (Controller Fault Type) gives the result of the last known action performed. Any command might be written to this command field while the HDC is

idle.

Reset The software reset is immediately executed. On completion of reset, the HDC goes to the idle state. Any access of a register while in the reset of the state.

of a register while in the reset state holds READY inactive until the reset is completed, causing the CPU to wait. A software reset is equivalent to a

hardware reset.

Resume Chain The HDC resumes execution of the

IOPB chain where it was interrupted due to a Status Result Area overflow. When receiving the Idle command, the HDC completes the current IOPB and

then enters the Idle state.

Start The IOPB chain pointed to by the Next Block Pointer is executed. When receiv-

ing the Idle command, the HDC completes the current IOPB and then

enters the Idle state.

#### **Controller Fault**

When this bit is set, the Controller Fault Type field is valid. The CF-bit is set by the HDC when entering the Idle state and reset when leaving the Idle state.

#### **Controller Fault Type**

The Controller Fault Type indicates the status of the HDC upon entering the Idle state. Whenever the Controller Fault Type is updated, the HDC issues an interrupt.

Normal Complete — Execution of the IOPB chain terminated without fault.

Null NBP — A Resume or Start Chain command was given with NBP zero.

SRA Overflow — The HDC filled the Status Result Area (SRA).

Wait Stop — An IOPB was completed with the

option Wait Stop set.

Forced Idle — An Idle command was given while

executing the Resume or Start Chain command.

Stop on Error — Non-recoverable disk error in conjunction with the SE-bit set caused the HDC to terminate chain execu-

tion.

Illegal IOPB — The HDC attempted to execute an

undefined IOPB.

SRB Error — A Status Result Block (SRB) was written when executing an IOPB with the Stop on SRB (SSRB) option set.

Data Time Out — Memory Time Out when transferring data.

IOPB Time Out — Memory Time Out when reading an

DM Time Out — Memory Time Out when reading the

Data Map.

SRB Time Out — Memory Time Out when writing a

Status Result Block.

Write Protected — WRPROT line was asserted when

executing a Disk Write command.

Reset — Hardware or software reset has been

Hardware or software reset has been executed.

#### **NEXT BLOCK POINTER**

The Next Block Pointer Register is a 32-bit register pointing to the IOPB currently being executed. The HDC updates it on IOPB completion.

#### STATUS RESULT POINTER

The 32-bit Status Result Pointer Register points to the system memory location where the next Status Result Block can be written. This pointer is updated after adding a new Status Result Block to the Status Result Area.

#### STATUS RESULT LENGTH

The 16-bit Status Result Length Register defines the size of the Status Result Area in terms of the number of Status Result Blocks. Therefore, the maximum size of the Status Result Area is 65536 Status Result Blocks. The Next Block Pointer, the Status Result Pointer, and the Status Result Length should only be updated while the HDC is in the Idle state.

#### COMMAND DESCRIPTION

All operations of the HDC result from commands. Commands are set up in system memory in IOPBs (I/O Parameter Blocks) (Figures 8 and 9). The HDC starts interpreting the command list after receiving the "Resume Chain" or "Start Chain" command from the host CPU (see Status/Command Register description). Errors and warnings on command execution are reported by adding Status Result Blocks (SRB) to the Status Result Area.

## NORMAL DISK I/O COMMANDS

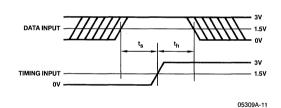

The HDC supports three normal disk I/O commands: READ, WRITE, and VERIFY. The multi-sector operation is performed on DRIVE starting at the desired TRACK, HEAD and SECTOR. RECORD COUNT defines the number of sectors. The General Select Byte in the Drive Parameter Block specifies whether the track number or the head number is to be incremented on sector overflow. SOURCE/DESTINATION ADDRESS is the starting address of the data block in sys-. tem memory (DME Low) or the address of the first Data Map Entry (DME High). These commands verify the head position before attempting the data transfer and hence verify seeks implicitly. The Data Mark option allows the DATA MARK parameter to be used instead of F8H. On singledensity floppy disks, the Data Mark option also causes the search for a deleted data mark. (See Section "HDC/Data Separator Handshaking.")

#### READ

READ performs a multi-sector data transfer from disk to system memory.

## WRITE

WRITE performs a multi-sector data transfer from system memory to the disk.

#### **VERIFY**

VERIFY compares multi-sector data on disk with data stored in system memory. It reports any mismatches or data read errors by updating the Status Result Area.

#### **INITIALIZATION COMMANDS**

#### **FORMAT**

The HDC formats the number of tracks specified by TRACK COUNT starting at HEAD and TRACK. The head and track number are incremented according to the General Select Byte in the Drive Parameter Block. The sectors are numbered as per the order given in the sector map, which is sequentially loaded from system memory starting at MAP POINTER. The number of sectors per track is specified in the Drive Parameter Block of this DRIVE. The data field of each sector is filled with PATTERN.

#### RELOCATE TRACK

A relocation vector is written to all data fields of a bad track. The relocation vector consists of the new track number (ALTERNATE TRACK) and the new head number (ALTERNATE HEAD) (i.e., the track's relocated location). Also, the address mark is changed from FE $_{\rm H}$  to FD $_{\rm H}$  to mark that this track is relocated. Thus, when the HDC encounters three consecutive sectors with an FD $_{\rm H}$  data mark, it assumes the track has been relocated. This command is illegal for single-density floppy disk drives.

#### LOAD DRIVE PARAMETER BLOCK

This command loads the Drive Parameter Block (DPB) for the selected DRIVE into the internal Drive Parameter RAM (see "Drive Parameters").

#### DUMP DRIVE PARAMETER BLOCK

The Drive Parameter Block for the selected DRIVE is transferred from the internal Drive Parameter RAM to the DESTINATION ADDRESS.

#### MARGINAL DATA RECOVERY COMMANDS

#### READ PHYSICAL SECTOR

This command lets the user recover a marginal data field which is unrecoverable by normal disk error recovery procedures. First it seeks to the desired track. If TRACK VERIFY is selected, the HDC reads ID fields until three consecutive sector headers show the right track number. This verifies it is on the right track. Beginning with the next index mark, the HDC starts counting the PHYSICAL SECTOR number of IDs specified by "PHYSICAL SECTOR" to locate the desired sector. It reads the data field while disregarding the ID field. The user can thus possibly recover data where headers and/or data marks have been rendered unreadable. PHYSICAL SECTOR specifies the absolute location of the sector. No retries are performed.

#### READ ID

READ ID attempts to recover the header ID information of a marginal sector. If LOCATOR DUMP is selected, then the first valid ID read is transferred to the DESTINATION ADDRESS. If LOCATOR DUMP is not selected, then the ID of the absolute sector specified by PHYSICAL SECTOR is transferred to DESTINATION ADDRESS. If this command is successfully executed, it updates the HDC's track position.

#### LOAD BUFFER

The data pointed to by the SOURCE ADDRESS is transferred to the internal sector buffer. The number of bytes transferred is determined by the sector size for the selected DRIVE.

## DUMP BUFFER

The data in the internal sector buffer is transferred to system memory starting at DESTINATION ADDRESS. The number of bytes transferred is specified by the sector size for the selected DRIVE.

Figure 8. IOPB Structure

| D <sub>C</sub>   |

|------------------|

| OINTER (15 : 0)  |

| DINTER (31 : 16) |

| ID               |

| OPTIONS          |

| BYTE 8           |

| BYTE 10          |

| BYTE 12          |

| BYTE 14          |

| BYTE 16          |

| BYTE 18          |

|                  |

(1) Not yet defined.

05308A-6

Figure 9. IOPB Parameters

|                                  |   |    |      | Options | <br>S |    |   |   |         |        |         |         |         | l                  | 1            |                 | T                 |                |                 |                 |

|----------------------------------|---|----|------|---------|-------|----|---|---|---------|--------|---------|---------|---------|--------------------|--------------|-----------------|-------------------|----------------|-----------------|-----------------|

| Command                          | 7 | 6  | 5    | 4       | 3     | 2  | 1 | 0 | Byte 9  | Byte 8 | Byte 11 | Byte 10 | Byte 13 | Byte 12            | Byte 15      | Byte 14         | Byte 17           | Byte 16        | Byte 19         | Byte 18         |

| Read                             | w | SE | SSRB |         | DME   | DM |   |   |         | Drive  | Tra     | nck     | Head    | Sector             | Data<br>Mark | Record<br>Count |                   | nation<br>: 0) | Destir<br>(31   |                 |

| Write                            | w | SE | SSRB |         | DME   | DM |   |   |         | Drive  | Tra     | ick     | Head    | Sector             | Data<br>Mark | Record<br>Count |                   | rce<br>: 0)    | Sou<br>(31      | rce<br>: 16)    |

| Verify                           | w | SE | SSRB |         | DME   | DM |   |   |         | Drive  | Tra     | ack     | Head    | Sector             | Data<br>Mark | Record<br>Count |                   | rce<br>: 0)    | Sou<br>(31      |                 |

| Format                           | w | SE | SSRB |         |       |    |   |   | Pattern | Drive  | Tra     | ıck     | Head    |                    | Track        | Count           | Map F<br>(15      | ointer<br>: 0) | Map P<br>(31    | ointer<br>: 16) |

| Relocate<br>Track                | w | SE | SSRB |         |       |    |   |   |         | Drive  | Tra     | ack     | Head    |                    | Alter<br>Tra |                 | Alternate<br>Head |                |                 |                 |

| Load Drive<br>Parameter<br>Block | w | SE | SSRB |         |       |    |   |   |         | Drive  |         |         |         |                    |              |                 |                   | ırce<br>: 0)   | Sou<br>(31      | rce<br>: 16)    |

| Dump Drive<br>Parameter<br>Block | w | SE | SSRB |         |       |    |   |   |         | Drive  |         |         |         |                    |              |                 |                   | nation<br>: 0) | Destir<br>(31 : | nation<br>: 16) |

| Read Physical<br>Sector          | w | SE | SSRB |         | τv    |    |   |   |         | Drive  | Tra     | ick     | Head    | Physical<br>Sector |              |                 | Desti             | nation<br>: 0) | Destir<br>(31   |                 |

| Read ID                          | w | SE | SSRB |         | L     |    |   |   |         | Drive  | Tra     | ıck     | Head    | Physical<br>Sector |              |                 |                   | nation<br>: 0) | Destir<br>(31   |                 |

| Load Buffer                      | w | SE | SSRB |         | DME   |    |   |   |         | Drive  |         |         |         |                    |              |                 |                   | rce<br>: 0)    | Sou<br>(31      | rce<br>: 16)    |

| Dump Buffer                      | w | SE | SSRB |         | DME   |    |   |   |         | Drive  |         |         |         |                    |              |                 | Desti<br>(15      | nation<br>: 0) | Destir<br>(31   |                 |

| Load<br>Syndrome                 | w | SE | SSRB |         |       |    |   |   |         | Drive  |         |         |         |                    |              |                 |                   | rce<br>: 0)    | Sou<br>(31      | rce<br>: 16)    |

| Dump<br>Syndrome                 | w | SE | SSRB |         |       |    |   |   |         | Drive  |         |         |         |                    |              |                 |                   | nation<br>: 0) | Destir<br>(31   | nation<br>: 16) |

| Correct Buffer                   | w | SE | SSRB |         | LD    |    |   |   |         | Drive  |         |         |         |                    |              |                 |                   | nation<br>: 0) | Destir<br>(31   |                 |

| Seek                             | w | SE | SSRB |         | ΤV    |    |   |   |         | Drive  | Tra     | ick     | Head    |                    |              |                 |                   |                |                 |                 |

| Restore                          | w | SE | SSRB |         | TV    |    |   |   |         | Drive  |         |         |         |                    |              |                 |                   |                |                 |                 |

#### LOAD SYNDROME

The Reed-Solomon check bytes are transferred from SOURCE ADDRESS to the internal Syndrome RAM. This command generates an error if the Drive Parameter Block of the selected DRIVE specifies CRC or external ECC error-checking.

#### DUMP SYNDROME

The Reed-Solomon check bytes are dumped to the DES-TINATION ADDRESS.

## CORRECT BUFFER

This command uses the contents of the Syndrome RAM to correct the data in the internal sector buffer. It generates an error if the Drive Parameter Block of the selected DRIVE specifies CRC or external ECC error-checking. If the LOCATOR DUMP option is selected, the HDC additionally writes the location and values of errors sequentially to DESTINATION ADDRESS. If the buffer address is greater than the sector size and the error pattern is non-zero, then the error is uncorrectable for that locator. If the error pattern and the buffer address both are zero, then no error was detected by that locator. If the error pattern is zero and the buffer address is greater than the sector size, then the error occurred in the check bytes.

#### **HEAD MOVEMENT COMMANDS**

#### SEEK

The HEAD of the selected DRIVE is moved to the desired TRACK. If TRACK VERIFY is selected, the HDC looks at the first encountered header to determine whether it is on the right track. If the track numbers mismatch, the HDC reports an error. Usually, this command is issued only if implied and overlapped seeks are disabled.

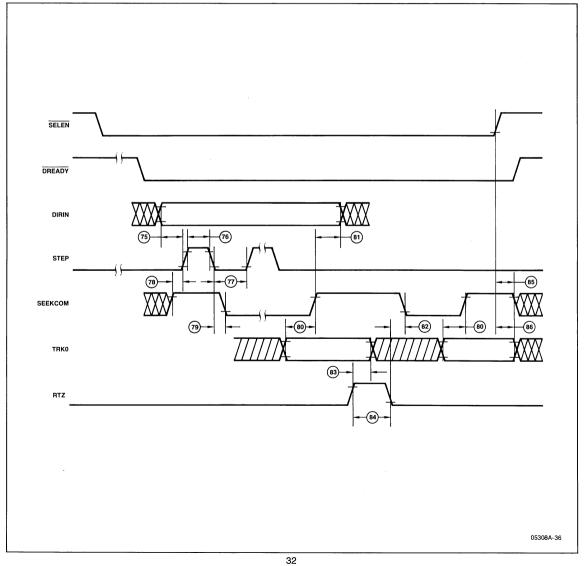

#### RESTORE

RESTORE moves the heads of the selected DRIVE to track 0. This command synchronizes the HDC and the drives or recovers seek errors. The HDC supports two restore options. It can restore drives by issuing step-out pulses until the drive reaches track 0 and asserts TRK0. Optionally, drives with built-in restore logic may be restored by a pulse on the RTZ (Return To Zero) line. If TRACK VERIFY is selected, the HDC will also scan the header IDs in order to verify that the restore was successful.

#### **OPTION BYTE**

One byte in each IOPB contains a set of options applicable to the particular command.

W --- WAIT

Ater execution of current IOPB, continue with next IOPB.

Stop IOPB execution after terminating current IOPB.

SE - TOP ON ERROR

0 - Option disabled.

Stop IOPB chain execution if current IOPB causes a Status Result block to be witten. SSRB - STOP ON STATUS RESULT BLOCK

0 — Option disabled.

Stop IOPB chain execution if current IOPB causes a Status Result block to be written.

DME - DATA MAP ENABLE

0 - Data Mapping disabled.

Data Mapping enabled. Source/ Destination Address links to first Data Map Entry.

DM - DATA MARK

0 - Data Mark disabled.

Data Mark enabled (see Normal Disk I/O Commands).

TV - TRACK VERIFY

0 - Track Verify disabled.

Track Verify enappled (see Read Physical Sector and Seek).

L — LOCATOR DUMP

0 — Locator Dump disabled.

1 — Locator Dump enabled (see Read ID).

#### **DATA MAPPING OPTIONS**

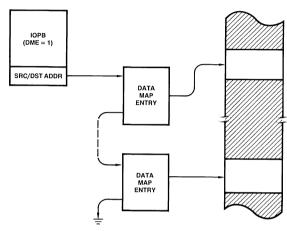

The Data Mapping option lets the HDC process data stored in noncontiguous system memory. This option is available to five commands: Read, Write, Verify, Load Buffer, and Dump Buffer. It is enabled by setting the Data Map Enable bit (DME-bit) in the IOPB.

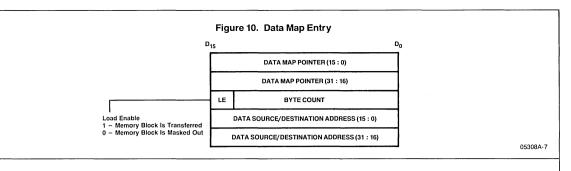

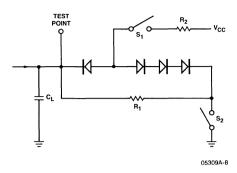

The last two words of the IOPB (Source/Destination Address) link to the first Data Map Entry (Figures 10 and 11). If this pointer is zero, then the Data Map does not exist and the HDC does not transfer data. Data Map Entries are linked together via the Data Map Pointer. The Data Map linked-list is terminated if the Data Map Pointer is set to zero. Each Data Map Entry defines a data buffer in system memory starting at the address defined by Data Source/Destination Address. The size of this buffer is defined by Byte Count. When Byte Count is set to zero, the HDC assumes a size of 2<sup>15</sup> bytes. When the Load Enable (LE-bit) is reset to zero, the HDC masks off a data block with the size specified by Byte Count (Figure 12).

#### STATUS RESULT BLOCK (SRB)

The host CPU reserves a Status Result Area defined by the 32-bit Status Result Pointer register and the 16-bit Status Result Length Register. Whenever the HDC terminates a command and an error occurred, it adds a Status Result Block (Figures 13 and 14) to the Status Result Area. A Status Result Block carries the same unique ID number of the IOPB where the error occurred.

## **Multi-record Command Terminated**

This SRB indicates that a Multi-record command has been terminated due to an error condition at the specified TRACK, HEAD, SECTOR, and RECORD COUNT.

#### No IDs Found On Track

A given Track was searched for an ID and none was found.

Figure 11. Data Map Entry Linked List

05308A-8

Figure 12. Data Mapping

05308A-9

Figure 13. Layout of Status Result Blocks

| D <sub>15</sub> | Do     |

|-----------------|--------|

| Byte 1          | Byte 0 |

| Byte 3          | Byte 2 |

| Byte 5          | Byte 4 |

| Byte 7          | Byte 6 |

| Byte 9          | Byte 8 |

Figure 14. Status Result Blocks

| Status Result Block                    | Byte 1 | Byte 0 | Byte 3          | Byte 2              | Byte 5 | Byte 4  | Byte 7    | Byte 6        | Byte 9          | Byte 8          |

|----------------------------------------|--------|--------|-----------------|---------------------|--------|---------|-----------|---------------|-----------------|-----------------|

| Multirecord Command<br>Terminated      | IC     | )      | Record<br>Count | Code <sup>(1)</sup> | Tra    | ack     | Head      | Sector        |                 |                 |

| No IDs Found on Track                  | IC     | )      |                 | Code                | Tra    | ack     | Head      |               |                 |                 |

| Format Error                           | IC     | )      |                 | Code                | Tra    | ack     | Head      |               |                 |                 |

| Seek Error                             | IC     | )      |                 | Code                | Currer | t Track | Desire    | d Track       | Current<br>Head | Desired<br>Head |

| Fatal Seek Error                       | IC     | )      |                 | Code                | Currer | t Track | Desire    | d Track       | Current<br>Head | Desired<br>Head |

| Relocated Track                        | IC     | )      |                 | Code                | Currer | t Track | New       | Track         | Current<br>Head | New<br>Head     |

| Relocated Track<br>(No Vector)         | IC     | )      |                 | Code                | Tra    | ack     | Head      |               |                 |                 |

| Record Not Found                       | IC     |        |                 | Code                | Tra    | ack     | Head      | Sector        |                 |                 |

| Record Not Found<br>(ID Errors)        | IC     | )      |                 | Code                | Tra    | ack     | Head      | Sector        |                 |                 |

| Multirecord Overflow                   | IC     | )      |                 | Code                | Tra    | ack     | Head      | Sector        |                 |                 |

| Data Not Recovered                     | IC     | )      |                 | Code                | Tra    | ack     | Head      | Sector        |                 |                 |

| Data Not Recovered with Retries        | IC     | )      | Retry<br>Count  | Code                | Tra    | ack     | Head      | Sector        |                 |                 |

| Data Not Recovered with ECC            | IC     | )      | Retry<br>Count  | Code                | Tra    | ack     | Head      | Sector        |                 |                 |

| Data SYNC Fault                        | 11     | )      |                 | Code                | Tr     | ack     | Head      | Sector        |                 |                 |

| Data Mark Error                        | . 10   | )      | Data<br>Mark    | Code                | Tr     | ack     | Head      | Sector        |                 |                 |

| Sector Size Mismatch                   | IC     | )      | Sector<br>Size  | Code                |        |         |           |               |                 |                 |

| Data Non-Verify                        | I      | )      |                 | Code                | Tr     | ack     | Head      | Sector        |                 |                 |

| Physical Data Recovered with ECC       | IC     | )      |                 | Code                |        |         |           |               |                 |                 |

| ECC Error Not Corrected                | 10     | )      |                 | Code                |        |         |           |               |                 |                 |

| ECC Not Selected                       | 10     | )      |                 | Code                |        |         |           |               |                 |                 |

| ECC Error in Data Field                | 10     | )      |                 | Code                |        |         |           |               |                 |                 |

| Data Mark Physical Error               | II     | ס      | Data<br>Mark    | Code                |        |         |           |               |                 |                 |

| ID CRC Error                           | IE     | )      |                 | Code                |        |         |           |               |                 |                 |

| Fault While Seeking                    | 10     | )      |                 | Code                | Tr     | ack     |           |               |                 |                 |

| Restore Fault                          | 10     | D      | Drive<br>Status | Code                | Tr     | ack     |           |               |                 |                 |

| Fault While Head Select                | 10     | D      |                 | Code                |        |         | Head      |               |                 |                 |

| Drive Selection Fault                  | 10     | D      | Drive<br>Status | Code                |        | -       |           |               |                 |                 |

| Drive Status Trap                      | 11     | D      | Drive<br>Status | Code                |        |         |           |               |                 |                 |

| Data Timeout                           | li li  | D      |                 | Code                | Byte   | Count   | Block Add | ress (15 : 0) | Block Addr      | ess (31 : 16)   |

| No Single Density<br>Floppy Relocation | II     | D      |                 | Code                |        |         |           |               |                 |                 |

| End of Data Map                        | II     | D .    |                 | Code                |        |         |           |               |                 |                 |

<sup>(1)</sup> Not yet defined.

#### **Format Error**

When reading or writing, it indicates that an Index Pulse occurred when not expected. When formatting, it indicates that the Index Pulse occurred before the format was completed. This means the number of sectors times the sector size is too large for the track.

#### Seek Error

The HDC has read a valid ID showing that the current TRACK/HEAD differs from the expected TRACK/HEAD.

#### Fatal Seek Error

After a seek error the HDC has performed a restore and a second seek, but the seek error still persists. The IOPB is aborted

#### **Relocated Track**

A track was read as relocated and the HDC auto-vectored to the new track.

#### Relocated Track (No Vector)

A track was read as relocated, but the HDC could not find a valid data field to read the vector. The IOPB is aborted.

#### Record Not Found

No ID was found corresponding to the desired sector number.

#### Record Not Found (ID Errors)

Sector was not found, but one or more IDs had CRC errors.

#### **Multi-record Overflow**

The HDC aborted a Multi-record command because the last sector of a track was read and the programmed Multi-Record Policy prohibits a track/head increment.

#### **Data Not Recovered**

The HDC could not recover a sector requested by a read command.

#### **Data Recovered with Retries**

Data was recovered using read retries (RETRY COUNT).

#### **Data Recovered with ECC**

The Reed-Solomon successfully corrected a read error. Retry Count specifies the number of retries performed before the error was corrected.

#### **Data Sync Fault**

The HDC successfully read the ID for the desired sector, but could not find an Address Mark for the data field.

#### Data Mark Error

The Data Mark read did not correspond to the Data Mark specified by the Drive Parameter Block.

#### Sector Size Mismatch

Sector Size read from the Header field does not match the Sector Size defined in the Drive Parameter Block (floppy formats only).

#### Data Non-Verify

The Verify command detected a mismatch between disk and memory data.

#### **Physical Data Recovered with ECC**

The Read Physical Sector command had to use ECC to correct the data field

#### **ECC Error Not Corrected**

The data transferred to system memory by Read Physical Sector contained uncorrected errors.

#### **FCC Not Selected**

Error correction attempted when ECC was not selected internally.

#### **ECC Error In Data Field**

An error was detected in the data field of a sector.

#### **Data Mark Physical Error**

The Data Mark read by Read Physical Sector did not correspond to programmed Data Mark.

#### **ID CRC Error**

A CRC error was detected when reading the ID field by the Read ID command.

#### Fault While Seeking

While seeking, the FAULT line was asserted or the SEEKCOM line was not asserted.

#### **Restore Fault**

The HDC could not restore the drive.

## **Fault While Head Select**

The HDC could not select the specified head. The FAULT line was asserted or SEEKCOM was not asserted (for floppy disk drives only).

#### **Drive Selection Fault**

A fault occurred when selecting a drive. The Drive Status byte latches the levels of the status lines when the fault occurred:

$D_9 = DREADY$

$D_{10} = FAULT$

$D_{11} = SEEKCOM$

$D_{12} = WRPROT$

$D_{13} = TRK0$

#### **Drive Status Trap**

An unexpected change in state of one or more drive status lines occurred while the drive was selected. The Drive Status byte latches the status lines. The IOPB is aborted.

#### **Data Time-out**

A memory time-out occurred while accessing the system memory. The Block Address defines the starting location of a block of system memory where the time-out occurred. Byte Count defines the length of the block.

#### No Single-Density Floppy Relocation

A Relocate Track command was attempted on a single-density floppy disk drive.

#### **End Of Data Map**

Unexpected end of Data Map encountered.

## DISK DATA I/O SECTOR FORMATS

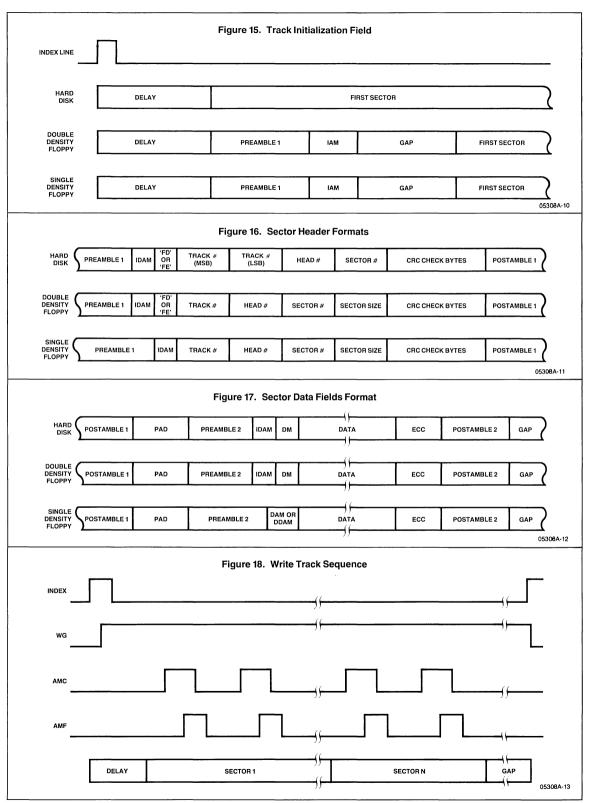

Data is stored on the disk in sectors. Each sector consists of two fundamental parts: the header and the data field. The sizes of all pads, gaps, preambles, postambles, and data fields are programmable in the Drive Parameter Block. Floppy disk formats also have an Index field at the beginning of each track.

#### Header

The header contains the Address Mark, the track number, the head number, and the sector number (Figure 16). Two trailing CRC check bytes protect the header. The beginning of the header is marked by an ID Address Mark (IDAM). The single-density floppy format requires a single-byte address mark while the double-density floppy and hard disk formats use a two-byte address mark. The first byte (the only byte for single-density floppy formats) of the address mark is a unique clock/data pattern written and detected by the data separator. Since the unique clock/data pattern is written by the disk data separator, its length and layout are transparent to the HDC. The second byte, which is processed by the HDC, specifies that this is a normal (FE<sub>H</sub>) or a relocated (FD<sub>H</sub>) track. This byte is not present for single-density floppy formats. A preamble and a postamble compensate for speed and mechanical variations of the disk system. The length of both fields is user-programmable.

## Data Field

A Data Mark similar to the header's ID Address Mark marks the beginning of the data field (Figure 17). The single-density floppy format uses a single-byte Data Mark which is different from the Address Mark. The data field can be marked by two types of data marks to specify either a normal data field or a deleted data field. The double-density floppy and the hard disk formats have a two-byte Data Mark consisting of a unique clock/data pattern similar to the Address Mark and a user-programmable Data Mark byte.

The data field has a user-programmable length of 128, 256, or 512 bytes. It is protected by one of three user-selectable data protection algorithms: CRC-CCITT (error detection), Single-Burst or Double-Burst Reed-Solomon (error detection and correction). Optionally, external error processing logic can be interfaced for hard disk format to implement any user-designed algorithm. The check bytes are stored in the ECC field. For external error processing, the user-designed external error processing logic reads and writes the ECC field. The number of ECC bytes appended varies from 2 to 15 bytes for the internal ECC options and 1 to 256 bytes (determined by the drive parameter block) for external ECC.

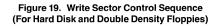

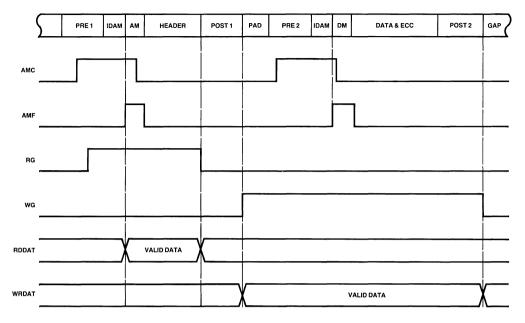

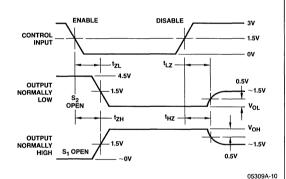

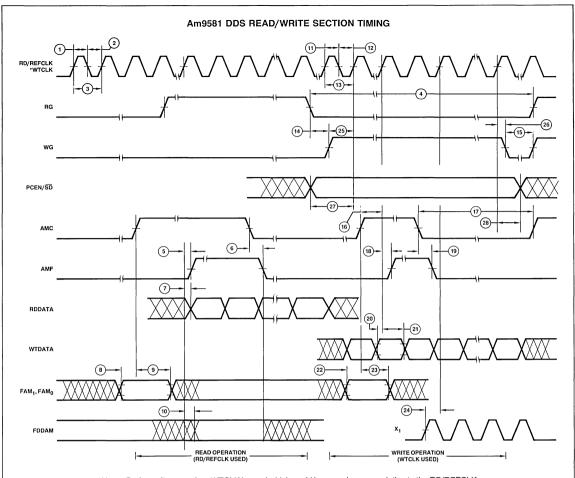

#### DATA SEPARATOR INTERFACE SIGNALS

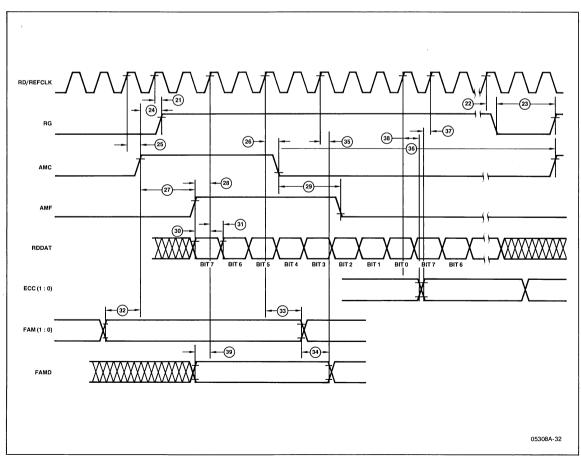

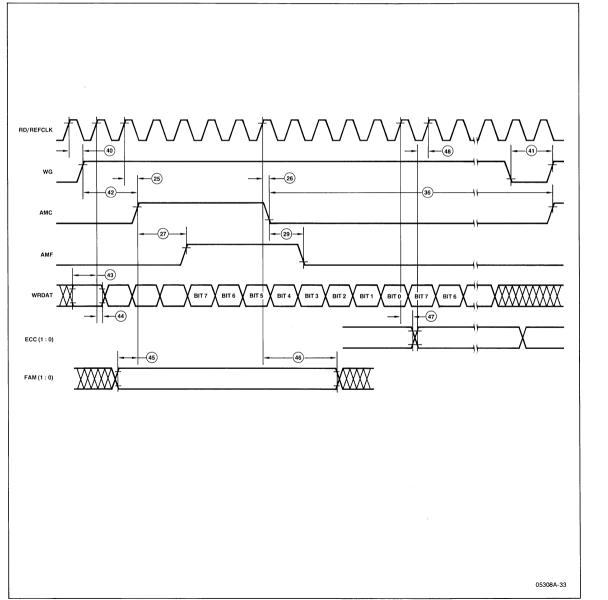

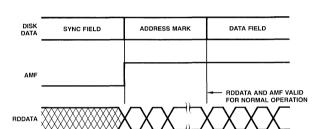

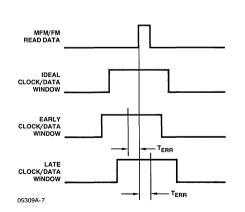

The data lines (RDDAT and WRDAT) transfer the data to and from the disk. The transfer is controlled by five signals: INDEX, AMC, AMF, RG, and WG. The FAM/ECC(1:0) and FAMD/ECCERR lines interface with external hardware to allow user-definable error-detection/correction. For floppy formats, these lines interface with the data separator to allow address/data mark detection and generation.

#### **Header Search Mechanism**

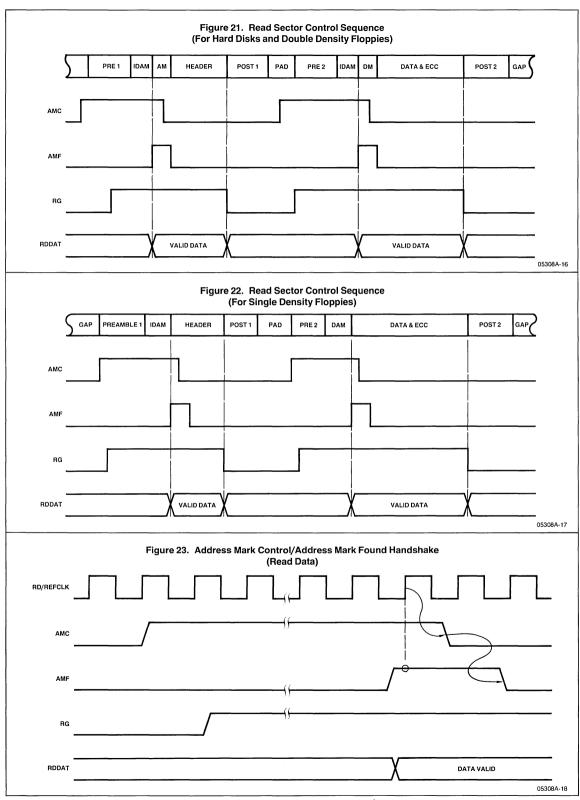

The unique clock/data patterns of the address/data marks are written and detected by the data separator only. When the HDC attempts to read a header or to access a data field, it activates Address Mark Control (AMC).

For floppy formats, the FAM/ECC(1:0) outputs differentiate between the various index, address, and data marks defined by the IBM Single- and Double-density Format. Whenever the HDC activates the AMC line to read or write a special mark from a floppy disk, the data separator should use the FAM/ECC(1:0) to determine the unique clock/data pattern to read or write. Additionally, for single-density floppy formats, the FAMD/ECCERR pin indicates that a deleted data address mark should be written or read.

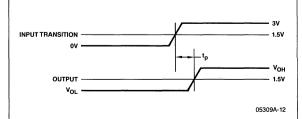

Next, the HDC activates Read Gate (RG) and waits for the data separator acknowledge. The data separator should assert Address Mark Found (AMF) when it detects an address/data mark. The rising edge of AMF indicates that valid data will be on the RDDAT pin on the next rising edge of the RD/REF CLK (see Figure 23). For double-density floppy and hard disk formats, the HDC checks the next eight bits for an FD<sub>H</sub> or FE<sub>H</sub>. If the check fails, a data address mark was found; the HDC deactivates AMC and RG. After AMF becomes inactive, AMC is reasserted followed by RG and the whole procedure is repeated until a header is found or it is determined that no header can be found (indicated by three index pulses). For single-density floppy formats, the rising edge of AMF indicates that a header address mark has been found.

After finding a valid header address mark, the HDC compares the next 48 bits (6 bytes) of serial data with the track, head, and sector number of the desired sector (and sector size for floppy formats) to determine if the right header has been found. A CRC check ensures the correctness of the header information. If the track or the head numbers recovered from the header do not match the desired track or head number, an error is flagged and the command is aborted. For floppy formats, sector size is also checked against the sector size defined for the current drive. The sector number is checked to see if this is the desired sector.

If the correct sector number was not found, then the process is started all over again until either the desired sector is found or the HDC determines that the sector cannot be found on the current track. If three index pulses are detected (indicating 2+ disk revolutions), the Sector Not Found error is flagged.

If the correct sector number was found, the search for the data mark begins.

05308A-14

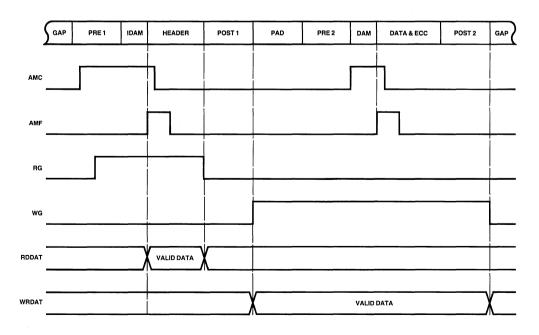

Figure 20. Write Sector Control Sequence (For Single Density Floppies)

05308A-15

#### **Data Field Read**

The HDC uses the same handshake procedure outlined above to search for the data address mark. For double-density floppy and hard disk formats, the HDC compares the byte following the data address mark to the programmed data mark to confirm that the data field has been found. The HDC reads the data field into the sector buffer and the ECC bytes into the error logic. For hard disk formats, the HDC ignores the ECC field if external ECC is selected. The external error processing logic should read the ECC field to verify the integrity of the data field. FAM/ ECC(1:0) and FAMD/ECCERR control the external error logic handshake. Immediately after the ECC field has been read, RG is turned off and the sector-read operation is terminated.

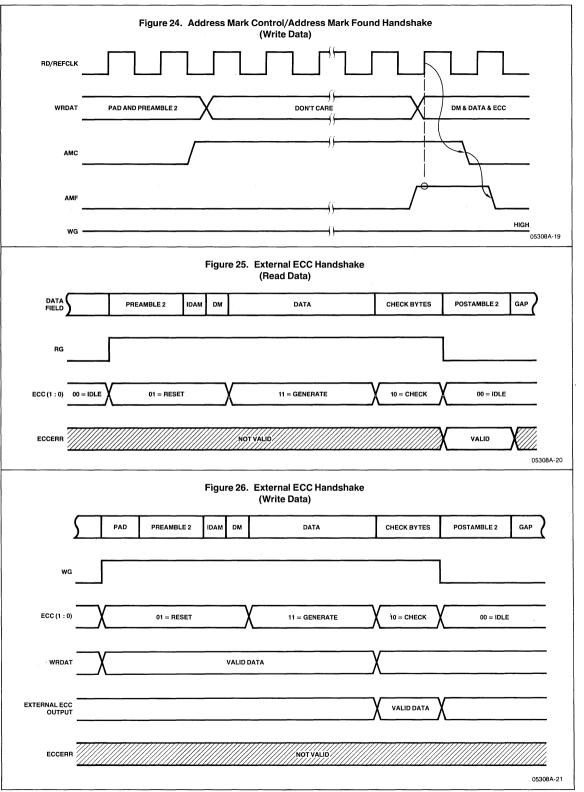

#### **Data Field Write**

Sector-write commands proceed similarly to sector-reads while searching for the desired sector. After finding the desired sector header, the subsequent data field and ECC field, including pad, preamble2, data address mark and postamble2 is overwritten. The HDC activates Write Gate (WG) at the beginning of the pad. Write Data on WRDAT line is valid with the next rising edge of the clock. First the HDC writes the pad and preamble2 fields. On completion of preamble2, AMC is activated. For floppy formats, FAM/ ECC(1:0) indicate to the data separator the data address mark to write. The data separator should assert AMF after writing the last data address mark bit. The HDC resumes data output with the next clock. For double-density floppy and hard disk formats, the HDC writes a userprogrammable data mark first. Next the data field is output on the WRDAT line. Depending on the selected ECC mode, either the HDC or the external error logic appends the check bytes to the data field. FAM/ECC(1:0) and FAMD/ECCERR control the external error logic handshake. WG is turned off after the postamble2 field is written. This completes the write-sector sequence.

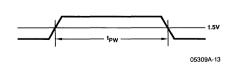

#### **Format Track**

Format Track always writes the entire track. It is the only command that writes the sector header. Beginning with the rising edge of the INDEX pulse, the HDC asserts WG and outputs the pattern for the delay field (Figure 18). Note that disk drives require that the delay field be wider than the INDEX pulse width. For floppy formats, an Index Address Mark (IAM) field follows the delay field. Then the HDC starts writing sectors.

For writing the headers, the HDC uses the track, head and sector size information supplied by the format IOPB. A sector map in the system memory supplies the logical sector number sequence. The first byte of the sector map is written in the sector number field of the first physical sector. The second byte is written in the second physical sector. This process continues until the required number of sectors have been formatted. For multiple track format commands, the sector maps for the tracks to be formatted are organized in a linear list in the system memory. The Map Pointer of format IOPB points to the beginning of this sector map list.

For writing address/data marks, the HDC proceeds as described in the section "Data Field Write". The data field is

filled with the user-supplied pattern byte in the format IOPB. The gap between the end of the last sector and the rising edge of the index pulse is filled by the gap pattern. The length of this gap field depends on the track capacity and the number of sectors/track. It is different from the intersector gap which has a user-definable length. The patterns written for all fields are shown in the table below.

| Field      | Single-density floppy formats | Double-density<br>floppy and<br>hard disk formats |

|------------|-------------------------------|---------------------------------------------------|

| Delay      | FF <sub>H</sub>               | 4E <sub>H</sub>                                   |

| Preamble1  | 00 <sub>H</sub>               | 00 <sub>H</sub>                                   |

| Postamble1 | FF <sub>H</sub>               | 4E <sub>H</sub>                                   |

| Pad        | 00 <sub>H</sub>               | 00 <sub>H</sub>                                   |

| Preamble2  | 00 <sub>H</sub>               | 00 <sub>H</sub>                                   |

| Postamble2 | FF <sub>H</sub>               | 4E <sub>H</sub>                                   |

| Gap        | FF <sub>H</sub>               | 4E <sub>H</sub>                                   |

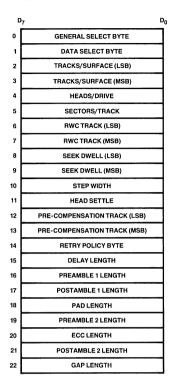

#### **DRIVE PARAMETER PROGRAMMING** (Figure 27)

The HDC contains one set of Drive Parameter Registers for each drive. The system can only access this register set indirectly by either of the following commands: Load Drive Parameter Block and Dump Drive Parameter Block. The block is set up in contiguous system memory. Byte values in this table, when set to zero, represent the value 256.

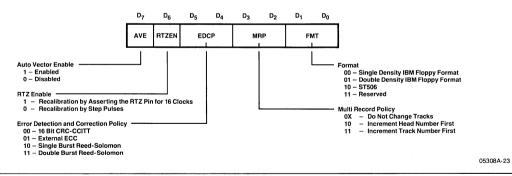

#### General Select Byte (Figure 28)

The EDCP field determines which of the error-checking algorithms the HDC should use to recover marginal data. The Auto Vector Enable bit (AVE) allows the HDC to vector automatically to the new track if a given track is found to be relocated. This bit is ignored for single-density floppy formats. The Multi-Record Policy (MRP) field determines the policy followed for multiple sector transfers. Multi- record commands may require that the HDC select a new track to access subsequent sectors. One option is to increment the head number. If the head number overflows, the HDC resets it to zero and increments the track number. If the track number overflows, it is reset to zero. The second option allows the track number to be incremented first. On overflow, the head number is incremented. The RTZEN bit defines the recalibration mode (move head to track 0). The HDC can either assert the RTZ pin (16 clock cycles active) or issue STEP pulses until TRK0 becomes active. The maximum number of STEP pulses for recalibration is 65535.

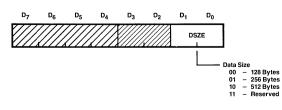

#### Data Select Byte (Figure 29)

The DSZE field defines the size of the data field for a particular drive.

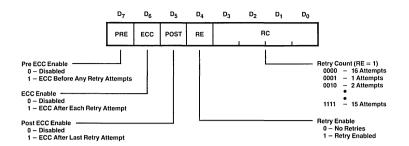

#### Retry Policy Byte (Figure 30)

The most significant three bits define the error-checking policy. These bits are ignored if CRC or external ECC is used. If ECC Before Retry is selected, the HDC uses ECC even when retry attempts are disabled. The RE-bit enables the number of retry attempts defined by Retry Count (RC).

Figure 27. Drive Parameter Block

05308A-22

Figure 28. General Select Byte

Figure 29. Data Select Byte

05308A-24

Figure 30. Retry Policy Byte

05308A-25

#### **Drive Parameters**

Tracks/Surface specifies the number of cylinders (tracks) in the range from 0 to 65536. Head/Drive specifies the number of moving heads (1 to 256). However, only the four least significant bits are output at the head select pins. Sectors/ Track defines the number of sectors per track (1 to 256). Heads/Drive and Sectors/Track are only needed for multirecord IOPBs to allow the HDC to determine the new track number. RWC Track specifies the track number where the Reduced Write Current pin should be activated (only for ST506 and floppy formats). If the current track number is greater than RWC Track, the pin (RWC) is activated. Precompensation Track specifies the track where the precompensation starts.

#### Seek Timing

Step Width (8-bit) determines the width of step pulses in increments of 12 clock cycles. Seek Dwell (16-bit) sets the delay between the falling edge and the rising edge of step pulses in increments of 12 clock cycles. Head Settle defines the time to allow the heads of the selected drive to settle, after the head select lines change, in increments of 4 clock cycles.

#### **Sector Format**

The sector format parameters specify the sizes of particular sector header and data fields.

#### **DISK DATA PROTECTION**

All data stored on disk is protected by error-checking algorithms. The HDC supports four modes:

- 16-bit CRC-CCITT (error detection)

- Single-Burst Reed-Solomon (single-burst correction)

- Double-Burst Reed-Solomon (double-burst correction)

- External ECC

The error-checking scheme for each drive is defined by the EDCP field in the General Select Byte of the Drive Parameter Block. It is possible to use a different ECC for each sector or track provided that the Drive Parameter Block is constantly changed. However, this is not a recommended procedure.

#### **CRC-CCITT**

The CRC-CCITT code is a cyclic-based, error-detecting/ non-correcting code. It is the industry standard error checking code for magnetic disk systems. CRC-CCITT is mandatory for the protection of the sector ID field, but the data field can be protected by any of the four modes mentioned above. The CRC generator polynomial is:

$$X^{16} + X^{12} + X^{5} + 1$$

The guaranteed capabilities of the code are listed below:

- · Detects all odd number bit errors

- · Detects all single-burst errors of 16 bits or less

- · Detects all single, double, and triple bit errors

#### Single-Burst Reed-Solomon

The HDC supports two error correction codes, Single-Burst Reed-Solomon and Double-Burst Reed-Solomon. Single-Burst Reed-Solomon corrects single-burst errors and detects double-burst and some triple-burst errors. A single burst of errors is defined as any number of bit errors (contiguous or noncontiguous) where the distance between the first and the last bit error does not exceed the burst length given in the table below. The ECC code protects the check bytes as well as the data. The guaranteed performance of the Single-Burst Reed-Solomon code is shown below.

| Sector<br>Size<br>(# of bytes) | Capa             | ection<br>ability<br>bits) | Capa             | Correction<br>Capability<br>(# of bits) |   |  |  |

|--------------------------------|------------------|----------------------------|------------------|-----------------------------------------|---|--|--|

|                                | Single<br>Bursts | Double<br>Bursts           | Single<br>Bursts | Double<br>Bursts                        |   |  |  |

| 128                            | 33               | 9                          | 9                | 0                                       | 6 |  |  |

| 256                            | 33               | 9                          | 9                | 0                                       | 6 |  |  |

| 512                            | 57               | 17                         | 18               | 0                                       | 9 |  |  |

This table shows, for instance, that in a sector of 256 bytes any single burst of errors with a length of up to 33 bits will be detected. Note, that two single bit errors separated by more than 32 bits will count as a double-burst error. Alternatively, any two random single-bursts (double-burst) of up to 9 bits each will be detected also. In this example, this code can correct a single burst of errors up to 9 bits and cannot correct double-burst errors. The table presents the guaranteed capabilities of this code. Under certain circumstances the code is capable of detecting longer bursts or even triple-burst errors.

#### **Double-Burst Reed-Solomon**

Double-Burst Reed-Solomon is an enhanced version of Single-Burst Reed-Solomon. This code can detect and correct single- and double-burst errors of the maximum size listed below:

| Sector<br>Size<br>(# of bytes) | Capa             | ection<br>ability<br>bits) | Corre<br>Capa<br>(# of | # of<br>Check<br>Bytes |    |

|--------------------------------|------------------|----------------------------|------------------------|------------------------|----|

|                                | Single<br>Bursts | Double<br>Bursts           | Single<br>Bursts       | Double<br>Bursts       |    |

| 128                            | 49               | 16                         | 25                     | 9                      | 10 |

| 256                            | 49               | 16                         | 25                     | 9                      | 10 |

| 512                            | 81               | 24                         | 41                     | 17                     | 15 |

#### External ECC

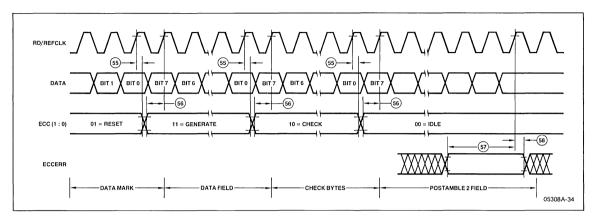

The HDC features external ECC to allow schemes other than CRC-CCITT or Reed-Solomon. External ECC can only be used for the protection of data fields. Three lines (ECC < 1:0 > and ECCERR) simplify interfacing the external ECC hardware. ECC < 1:0 > present the status of the HDC to allow the external ECC to run synchronously. The status is coded in Gray code; only one bit changes when going from one state to the next (Figure 26).

In the IDLE state, no data field of a sector is written or read. The external ECC should be inactive.

RESET should reset the external ECC to prepare itself for an ECC process. At the end of the data mark, while reading or writing the last bit, the status lines change into the GENERATE state.

On the next rising edge of the RD/REF CLK, the external ECC must be prepared to receive valid data on either the RDDAT or WTDAT lines (depending on whether RG or WG is asserted). The external ECC must generate the check bytes. When reading or writing the last bit of the data field, the lines change to the CHECK state.

CHECK enables the external ECC either to multiplex the check bytes on WRDAT (WG active) or to compare the generated check bytes with the bytes read from RDDAT (RG active). With the external ECC, a programmable number of check bytes can be added to the data field of a sector (1 to 256 bytes).

On completion of the check byte field, at the last bit of the last check byte, the status lines change back to the IDLE state. On the next rising edge of the RD/REF CLK, the IDLE state will be in effect. During the Postamble2 section following the check bytes, the ECCERR pin will be sampled by the HDC for an "Error Found" signal from the external ECC. If the ECCERR pin remains inactive throughout the Postamble2 field, then the HDC assumes that the data is valid. If the ECCERR line is activated at any time during the Postamble2 field, then the HDC assumes that an error occurred in the data field.

#### INTERFACING

#### SYSTEM INTERFACE

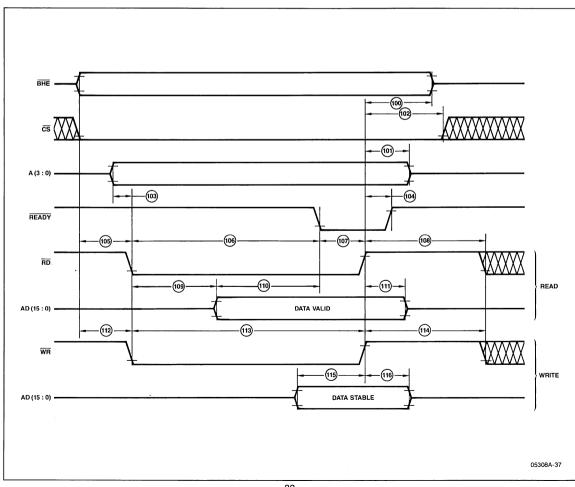

For both Slave Mode and Master Mode the system bus interface can be programmed for byte ( $B\overline{W}$  High) or word ( $B\overline{W}$  Low) transfers as shown in Figure 5.

#### Slave Mode

In Slave Mode, the host CPU can access the five internal registers of the HDC.  $A_0$  to  $A_3$  indicate the address of the internal register (Figure 4). In Byte Mode, the High byte is accessed if  $A_0$  is High and the Low byte is accessed if  $A_0$  is Hold and the Low byte is accessed if  $A_0$  is High and the Low byte is accessed if  $A_0$  is READY to indicate that it is ready to complete the access.

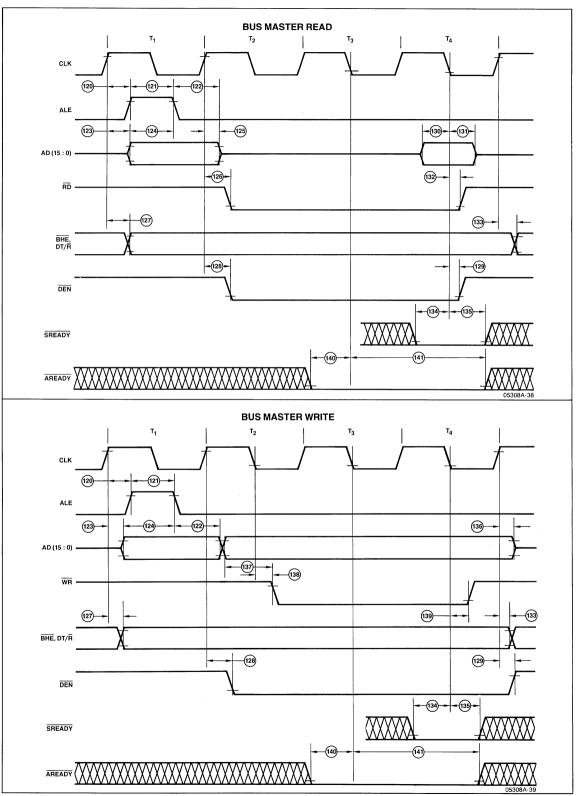

#### Master Mode

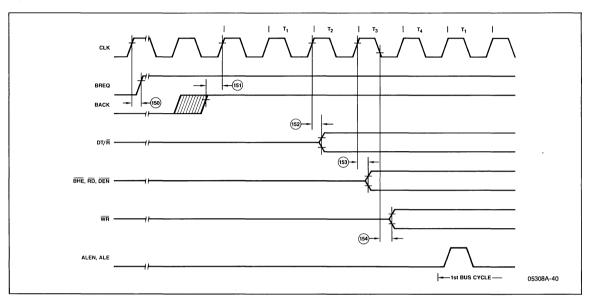

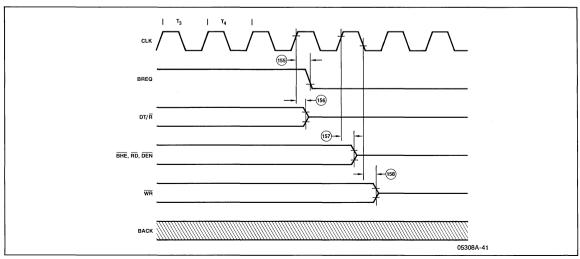

The HDC is in Master Mode when it controls the system bus. To request the mastership on the system bus, the HDC asserts Bus Request (BREQ). The bus is granted to the HDC when Bus Acknowledge (BACK) is active. The HDC keeps BREQ asserted until it releases the bus after finishing a DMA burst of programmable length or when the burst is preempted by removing BACK.

A Byte transfer occurs in Word Mode when only one byte remains to be transferred or when the system address is odd. The throttling of DMA transfers on the system bus is controlled by the Mode Register. The HDC inserts a programmable number of software Wait States into the DMA bus cycle. Additionally, it inserts hardware Wait States until the memory asserts READY.

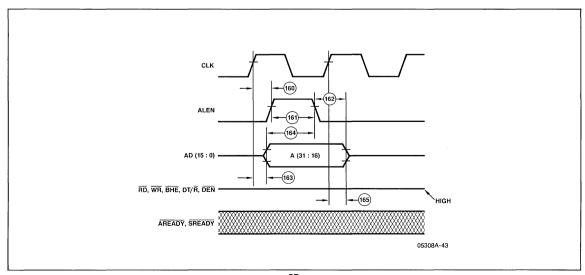

Upper Address Latch Enable (ALEN) may latch the upper address word (A $_{16}$  to A31) in an external address latch. The upper address is only updated if a change demands this update.

#### Interrupts

The HDC interrupts the host CPU when it has completed the initialization procedure executed after a hardware or software reset or when it has completed a command chain. The initialization interrupt cannot be disabled. The interrupt on command chain completion can be enabled or disabled by the Interrupt Mask bit in the Mode Register.

#### **DISK CONTROL INTERFACE**

The Disk Control Interface selects drives and heads and controls the head positioning. It is programmable either to provide a floppy disk type of interface or to conform with the ST506 drive interface standard.

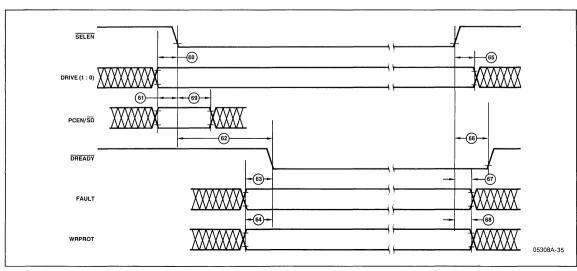

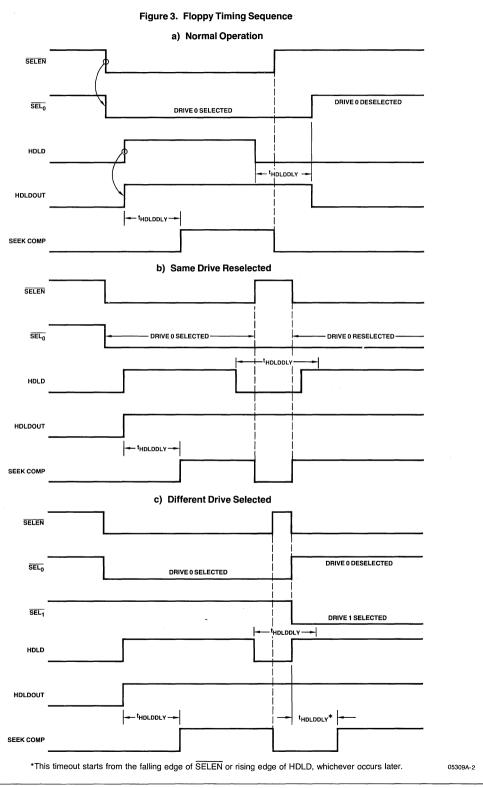

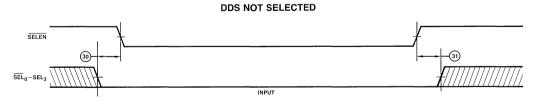

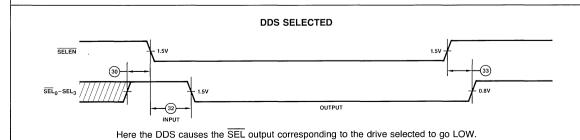

#### **Drive Selection**

Drives are de-selected when SELEN is High. The two bits DRIVE <1:0> select one of up to four drives. DRIVE <1:0> are valid when SELEN is Low. SELEN remains Low as long as the drive is selected. The selected drive acknowledges the selection by activating DREADY. If SELEN is not acknowledged within 2<sup>16</sup> clocks, then the HDC assumes that the selected drive is not present and generates a time-out error. If FAULT is asserted after activating DREADY, then the HDC de-selects the drive and generates a fault error.

#### **Head Positioning**

Seek operations are performed via the lines STEP, DIRIN, SEEKCOM, RTZ, and TRK0. Normal seeks pulse the STEP line to move the head to the desired track. Restore may pulse the STEP or RTZ line to move the head to track 0. DIRIN specifies the direction in which the head should move on SEEK pulses.

SEEKCOM is asserted by the drive to indicate that the head has moved to the desired track. Once the drive has acknowledged the completion of a seek by activating SEEKCOM, it must keep SEEKCOM active as long as it is selected or until it receives another seek command; otherwise the HDC issues a drive fault error. When executing the restore or seek commands, the drive must acknowledge the first STEP pulse or the RTZ pulse (SEEKCOM pulsed Low) within 2<sup>16</sup> clocks or the HDC will generate a seek error.

#### Write Protect

The Write Protect line is sampled just prior to execution of a WRITE or FORMAT command. If the line is High, the command is aborted.

#### INTERFACE SIGNALS

$m V_{CC1}, V_{CC2} - + 5V$  Power Supply  $m V_{SS1}, V_{SS2} - Ground$

#### SYSTEM INTERFACE LINES

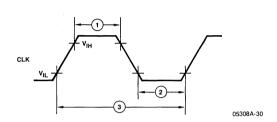

#### CLK — System Clock (Input)

CLK is a TTL-compatible clock input to time DMA transfers and disk control operations (seeks).

#### RD — Read (Input/Output, Active Low)

Read is a bidirectional, active Low, three-state signal. A Low on this line indicates that the CPU or HDC is performing an I/O or memory read cycle. When the HDC is in Slave Mode, this is an input signal used by the CPU to read the internal registers of the HDC. When the HDC is the bus master, this signal is an output used by the HDC to access data from memory.  $\overline{\text{RD}}$  and  $\overline{\text{WR}}$  must not be active simultaneously.

#### WR — Write (Input/Output, Active Low)

Write is a bidirectional, active Low, three-state signal. A Low indicates that the CPU or HDC is performing an I/O or memory write cycle. When the HDC is in Slave Mode, it is an input signal used by the CPU to load the internal registers of the HDC. When the HDC is Bus Master, this signal is an output used by the HDC to write data into system memory.  $\overline{\text{RD}}$  and  $\overline{\text{WR}}$  must not be active simultaneously.

#### ALE — Address Latch Enable (Output, Active High)

The trailing edge of ALE latches the lower address word ( $A_0$  to  $A_{15}$ ) into the external address latch.

## ALEN — Upper Address Latch Enable (Output, Active High)

The trailing edge of ALEN latches the upper address word ( $A_{16}$ to  $A_{31}$ ) into the external address latch. The HDC executes Upper Address latch cycles as necessary to minimize bus occupancy. The address is updated when a new command is executing or whenever the upper address for the current bus cycle differs from the address of the previous bus cycle.

### DT/R — Data Transmit/Receive (Output, Three-State)

When the HDC is bus master, a High on this output indicates that data is being transmitted from the HDC. A Low on this output indicates that data is being transferred into the HDC. This output is three- stated when the HDC is not in control of the system bus.

## DEN — Data Enable (Output, Active Low, Three-State)

When the HDC is bus master, a Low on this output indicates that data is driven on the Address/Data bus or the Address/Data bus is three-stated for receiving data. This output is three-stated when the HDC is not in control of the system bus.

#### BHE — Byte High Enable (Input/Output, Active Low)

BHE is a bidirectional, active Low signal to enable data onto the most significant byte of the data bus (AD<sub>15</sub>–AD<sub>8</sub>). BHE is Low when data is to be accessed on the high portion of the bus.

| BHE | Α0 | Size       |

|-----|----|------------|

| L   | L  | Whole word |

| L   | Н  | Upper byte |

| Н   | L  | Lower byte |

| Н   | Н  | Reserved   |

When the HDC is a bus master, this pin is an output. It is an input when the HDC is in Slave Mode.  $\overline{BHE}$  is disabled and ignored when the HDC is strapped to a byte interface.

## AD < 15:0 > — Address/Data Bus (Input/Output, Active High)

The Address/Data Bus is a time-multiplexed, bidirectional, three- state, 16-bit bus used for all system transactions. A logic High on the bus corresponds to a "1" and a logic Low corresponds to a "0". AD $_0$ is the least significant bit. The presence of an address is defined by ALE or ALEN. When ALE is High, the bus contains the Lower Address bits  $A_0$  to  $A_{15}$ . When ALEN is High, the bus contains Upper Address bits  $A_{16}$  to  $A_{31}$ . The 32-bit address allows the HDC to direct linear addressing of 4 GBytes.

The presence of data is indicated by  $\overline{RD}$  and  $\overline{WR}$ . When the HDC is in Slave Mode  $\overline{RD}$  and  $\overline{WR}$  may be asynchronous to the system clock (CLK). In Master Mode the Address/Data Bus is driven synchronously using a four-cycle bus transfer.

#### A<sub>0</sub> — Address Line 0 (Input, Active High)

This pin selects between the odd byte (High) and the even byte (Low) of the internal registers. It is used only when the HDC is in Slave Mode.

### A<3:1> — Address Line 1 to 3 (Input, Active High)

When the HDC is in Slave Mode, these lines are the address inputs selecting one of the internal registers. These lines are ignored when the HDC is bus master.

#### READY — Ready (Input/Output, Open Drain, Active Low)

When the HDC is bus master, this is an input to extend the bus cycle for slow memories and peripheral devices. When the HDC is in Slave Mode, this is an output indicating that the HDC is ready to complete the bus transfer. The READY input may be synchronous or asynchronous depending on the programming of the A/S strap.

#### BREQ — Bus Request (Output, Active High)

The HDC activates BREQ to request the control of the system bus.

## BACK — Bus Acknowledge (Input, Active High)